# HARDWARE NEURAL ACCELERATOR IMPLEMENTATION FOR IoT BASED APPLICATIONS

## **M.Tech** Thesis

By C SANDEEP 2002102017

## DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE JUNE 2022

# HARDWARE NEURAL ACCELERATOR IMPLEMENTATION FOR IoT BASED APPLICATIONS

A THESIS

Submitted in partial fulfillment of the requirements for the award of the degree **of**

Master of Technology

By C SANDEEP

## DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE JUNE 2022

#### **INDIAN INSTITUTE OF TECHNOLOGY INDORE**

#### **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the thesis entitled HARDWARE NEURAL ACCELERATOR FOR IOT BASED APPLICATIONS in the partial fulfillment of the requirements for the award of the degree of MASTER OF TECHNOLOGY and submitted in the DEPARTMENT OF ELECTRICAL ENGINEERING, Indian Institute of Technology Indore, is an authentic record of my own work carried out during the time period from August 2020 to June 2022 under the supervision of Prof. Santosh Kumar Vishvakarma, Professor, Department of Electrical Engineering, Indian Institute of Technology Indore.

The matter presented in this thesis has not been submitted by me for the award of any other degree at this or any other institute.

Signature of the student with date **C** Sandeep

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

Signature of the Supervisor of

M.Tech. thesis (with date)

Prof. Santosh Kumar Vishvakarma

Mr. C Sandeep has successfully given his M.Tech. Oral Examination held on 07/06/2022.

Signature(s) of Supervisor(s) of M.Tech. thesis Date: 09/06/2022

achon.

Signature of PSPC Member #1 Date: 09.06.2022

Convener, DPGC Date: 09/06/2022

. galaberger

Signature of PSPC Member #2 Date: <sup>09.06.2022</sup>

#### ACKNOWLEDGEMENT

I wish to thank my supervisor, Prof. Santosh Kumar Vishvakarma, Professor, IIT Indore, for his patience, guidance, and support. I have benefited greatly from their wealth of knowledge. I am extremely grateful that he took me on as a student and continued to have faith in me throughout the year. He has been very supportive since day one and I am grateful to him for devoting his time in guiding and motivating me to make the right decision. I am thankful to him for providing me with the opportunities that shaped my M.Tech to be as it is today. I would also like to thank Ph.D. scholar Gopal Raut for his technical guidance and supportive during M.Tech thesis project.

I sincerely thank my PSPC members, Prof. Ram Bilas Pachori, and Dr. Jayaprakash Murugesan, for their useful suggestions and valuable remarks during M.Tech project work. Their encouraging words and thoughtful, detailed feedback have been very important to me. I also acknowledge IIT Indore for providing me the necessary infrastructure and research facilities for the project work. I am thankful to all the faculty members of the Discipline of Electrical Engineering for their kind support during my M.Tech work.

Finally, I owe a lot to my family, friends, and classmates for always encouraging and supporting me to stay motivated and focused on completing the project.

C Sandeep

# Dedicated to my family

#### Abstract

#### HARDWARE NEURAL ACCELERATOR FOR IoT BASED APPLICATIONS

In recent years, on-chip Neural Network Accelerators have grown in popularity as one of the best algorithms for numerous key detection and classification problems in image, speech, and a variety of other never-ending applications in intelligent system design. While their on-chip presence is desirable, their high computational demands continue to be a roadblock in the development of the next generation of System on Chips. Although hardware accelerators for Convolutional Neural Networks are frequently simple designs, a traditional design approach has not been very successful, as they often require a lot of silicon area and power. Fixed point processing, according to researchers, can result in a large reduction in resource use while having a negligible influence on accuracy. Many issues that are challenging for other computational models, such as image processing, pattern recognition, prediction, and classification, are well-suited to a Convolutional Neural Network. Hardware designs can feature a more parallel structure of CNNs to improve performance or lower implementation costs, especially for applications that require high parallel computation. However, hardware platforms have a lot of unique disadvantages, including limits with high data precision, which is related to the hardware cost of the necessary computation, and the hardware implementation's lack of reconfigurability compared to software. Due to resource-intensive parts such as multipliers, current Convolutional Neural Network hardware implementations have an excess area need. The present work addresses this challenge by proposing a Co-ordinate Rotation Digital Computer (CORDIC)- based neuron architecture (RECON) implemented using In-SRAM In-Memory Computing and modified Static Manchester Carry Adder, which can be configured to compute multiplyaccumulate (MAC). The CORDIC-based architecture uses linear relationship to realize MAC, whereas CORDIC algorithm uses minimum resources to realize

different mathematical operations. The CORDIC architecture is area and powerefficient with the overhead of lower throughput. In this project, we propose a Pipelined CORDIC based MAC using In-Memory Computing and modified Static Manchester Carry adder. This proposed design significantly increases the throughput by 40% when compared with conventional methods. Choosing 8-bit precision improves the power consumption and area utilization. When operated at 1V, the power consumption decreases by 38%. Hence, the proposed design offers the best throughput among the state of art and consumes lesser power and area when designed at 8-bit precision and operated at 1 V.

## **TABLE OF CONTENTS**

| TITLE PAGE        | Ι   |

|-------------------|-----|

| DECLARATION PAGE  | II  |

| ACKNOWLEDGEMENT   | III |

| DEDICATION PAGE   | IV  |

| ABSTRACT          | V   |

| TABLE OF CONTENTS | VII |

| LIST OF FIGURES   | XI  |

| LIST OF TABLES    | XV  |

| Chapter 1: Introduction                                                                                                                                                                                                                                                                          | 1                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1.1 Artificial Intelligence                                                                                                                                                                                                                                                                      | 1                                      |

| 1.1.1 Applications of Artificial Intelligence                                                                                                                                                                                                                                                    | 2                                      |

| 1.1.2 Categorization of Artificial Intelligence                                                                                                                                                                                                                                                  | 3                                      |

| 1.2 Machine Learning                                                                                                                                                                                                                                                                             | 3                                      |

| 1.2.1 Supervised Machine Learning algorithms                                                                                                                                                                                                                                                     | 4                                      |

| 1.2.2 Unsupervised Learning                                                                                                                                                                                                                                                                      | 4                                      |

| 1.2.3 Semi-supervised Learning                                                                                                                                                                                                                                                                   | 4                                      |

| 1.2.4 Reinforcement Learning                                                                                                                                                                                                                                                                     | 5                                      |

| 1.3 Deep Neural Network                                                                                                                                                                                                                                                                          | 5                                      |

| 1.3.1 Neural Networks and DNNs                                                                                                                                                                                                                                                                   | 7                                      |

| 1.4 Overview of DNNS                                                                                                                                                                                                                                                                             | 9                                      |

|                                                                                                                                                                                                                                                                                                  |                                        |

| 1.4.1 Convolutional Neural Networks                                                                                                                                                                                                                                                              | 10                                     |

| <ul><li>1.4.1 Convolutional Neural Networks</li><li>1.5 DNN Development Resources</li></ul>                                                                                                                                                                                                      | 10<br>14                               |

|                                                                                                                                                                                                                                                                                                  | -                                      |

| 1.5 DNN Development Resources                                                                                                                                                                                                                                                                    | 14                                     |

| <ul><li>1.5 DNN Development Resources</li><li>1.5.1 Frameworks</li></ul>                                                                                                                                                                                                                         | 14<br>15                               |

| <ul><li>1.5 DNN Development Resources</li><li>1.5.1 Frameworks</li><li>1.5.2 Popular Data Sets for Classification</li></ul>                                                                                                                                                                      | 14<br>15<br>15                         |

| <ul> <li>1.5 DNN Development Resources</li> <li>1.5.1 Frameworks</li> <li>1.5.2 Popular Data Sets for Classification</li> <li>1.6 Hardware of DNN processing</li> </ul>                                                                                                                          | 14<br>15<br>15<br>18                   |

| <ul> <li>1.5 DNN Development Resources</li> <li>1.5.1 Frameworks</li> <li>1.5.2 Popular Data Sets for Classification</li> <li>1.6 Hardware of DNN processing</li> <li>1.7 Machine Learning Accelerators</li> </ul>                                                                               | 14<br>15<br>15<br>18<br>21             |

| <ul> <li>1.5 DNN Development Resources</li> <li>1.5.1 Frameworks</li> <li>1.5.2 Popular Data Sets for Classification</li> <li>1.6 Hardware of DNN processing</li> <li>1.7 Machine Learning Accelerators</li> <li>1.7.1 Heterogenous Computing Platforms</li> </ul>                               | 14<br>15<br>15<br>18<br>21<br>22       |

| <ul> <li>1.5 DNN Development Resources</li> <li>1.5.1 Frameworks</li> <li>1.5.2 Popular Data Sets for Classification</li> <li>1.6 Hardware of DNN processing</li> <li>1.7 Machine Learning Accelerators</li> <li>1.7.1 Heterogenous Computing Platforms</li> </ul>                               | 14<br>15<br>15<br>18<br>21<br>22       |

| <ul> <li>1.5 DNN Development Resources</li> <li>1.5.1 Frameworks</li> <li>1.5.2 Popular Data Sets for Classification</li> <li>1.6 Hardware of DNN processing</li> <li>1.7 Machine Learning Accelerators</li> <li>1.7.1 Heterogenous Computing Platforms</li> <li>1.7.2 ASICs and FPGA</li> </ul> | 14<br>15<br>15<br>18<br>21<br>22<br>22 |

| 2.3 IMCs Fundamental Principles and Prominence               | 24 |

|--------------------------------------------------------------|----|

| 2.4 In-SRAM based IMC                                        | 26 |

| 2.4.1 6T SRAM                                                | 27 |

| 2.5 SRAM based IMC using local and global bitlines           | 29 |

| 2.5.1 Advantages of Fast and Reliable IMC design             | 31 |

| 2.5.2 <i>Abar.B</i> generation using IMC                     | 31 |

| 2.5.3 Read Enable and Write driver                           | 32 |

| Chapter 3: CORDIC Algorithm                                  | 35 |

| 3.1 Background                                               | 35 |

| 3.2 Algorithm                                                | 35 |

| 3.3 Accumulator Registers                                    | 39 |

| 3.4 Computation modes                                        | 40 |

| 3.4.1 Rotation mode                                          | 42 |

| 3.4.2 Vectoring mode                                         | 42 |

| 3.4.3 Arctangent                                             | 43 |

| 3.4.4 Vector Magnitude and Cartesian-Polar Transformation    | 43 |

| 3.5 Expanding the Computation Domain                         | 43 |

| Chapter 4: Modified Static Manchester Carry Adder/Subtractor | 47 |

| 4.1 Adders and Carry-Skip Adders                             | 49 |

| 4.2 Dynamic Manchester Carry Chain Adder                     | 49 |

| 4.3 Modified Static Manchester Carry Chain Adder             | 51 |

| Chapter 5: MAC Design Using CORDIC Algorithm                 | 55 |

| 5.1 CORDIC Algorithm                                         | 56 |

| 5.1.1 CORDIC configuration to MAC                            | 58 |

| 5.2 Pipelining to increase performance of MAC                | 58 |

| 5.3 Number of pipelining stages                              | 61 |

| Chapter 6: Results and Discussions |    |

|------------------------------------|----|

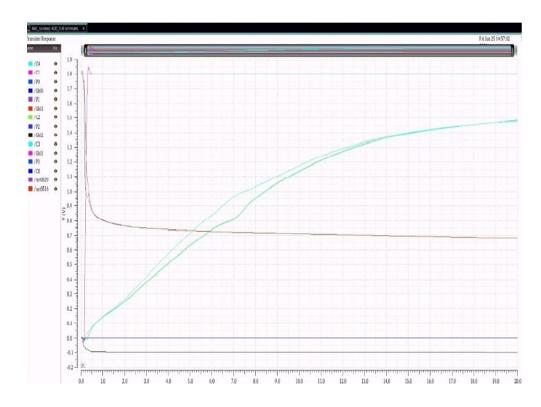

| 6.1 Delay Estimations              | 64 |

| 6.2 Power Estimations              | 65 |

| 6.3 Functional Verification        | 66 |

| 6.4 Conclusion                     | 67 |

68

#### References

## LIST OF FIGURES

| Figure<br>No.                                       | Figure Title Figure Title                                                                                                             |    |  |  |  |  |  |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|

| Fig. 1.1                                            | Deep learning in the context of artificial intelligence                                                                               |    |  |  |  |  |  |

| Fig. 1.2                                            | Connections to a neuron in the brain. $x_i$ , $wi$ , $f()$ , and b are                                                                |    |  |  |  |  |  |

|                                                     | the activations, weights, nonlinear function, and bias, respectively                                                                  |    |  |  |  |  |  |

| Fig. 1.3                                            | Simple neural network                                                                                                                 | 8  |  |  |  |  |  |

| Fig. 1.4                                            | Example of an image classification task. The machine                                                                                  | 10 |  |  |  |  |  |

|                                                     | learning platform takes in an image and outputs the                                                                                   |    |  |  |  |  |  |

|                                                     | confidence scores for a predefined set of classes                                                                                     |    |  |  |  |  |  |

| Fig. 1.5                                            | Dimensionality of convolutions. (a) 2-D convolution in<br>traditional image processing. (b) High dimensional<br>convolutions in CNN   | 12 |  |  |  |  |  |

| Fig. 1.6                                            | Convolutional neural networks                                                                                                         | 12 |  |  |  |  |  |

| Fig. 1.7                                            | Various forms of nonlinear activation functions                                                                                       | 14 |  |  |  |  |  |

| Fig. 1.8                                            | Various forms of pooling                                                                                                              | 15 |  |  |  |  |  |

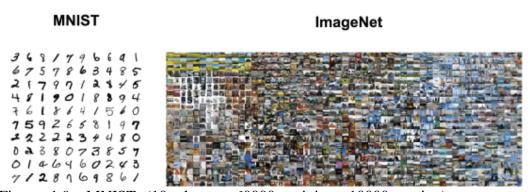

| Fig. 1.9                                            | MNIST (10 classes, 60000 training, 10000 testing) versus<br>ImageNet (1000 classes, 1.3 million training, 100000 testing)<br>data set | 17 |  |  |  |  |  |

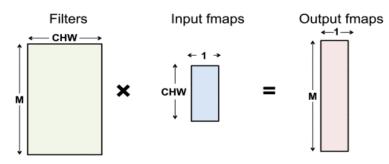

| Fig. 1.10                                           | Mapping to matrix multiplication for fully connected                                                                                  | 20 |  |  |  |  |  |

|                                                     | layers(a) Matrix Vector mul- tiplication is used when                                                                                 |    |  |  |  |  |  |

|                                                     | computing a single output feature map from a single input                                                                             |    |  |  |  |  |  |

| feature map. (b) Matrix Multiplications is used whe |                                                                                                                                       |    |  |  |  |  |  |

|                                                     | computing N output feature maps from N input feature                                                                                  |    |  |  |  |  |  |

|                                                     | maps                                                                                                                                  |    |  |  |  |  |  |

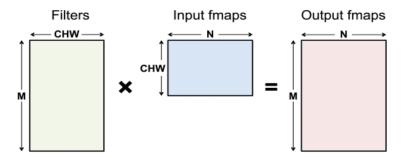

| <b>Fig. 1.11</b> Mapping to matrix multiplication for convolutional layers.<br>(a) Mapping convolution to Toeplitz matrix. (b) Extend |                                                                                                                                                                                                                                                                                                                            |    |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| Fig. 2.1                                                                                                                              | Toeplitz matrix to multiple channels and filters<br>Basic Principles and Significance of IMC                                                                                                                                                                                                                               | 25 |  |  |

| Fig. 2.2                                                                                                                              | Schematic of 6T SRAM                                                                                                                                                                                                                                                                                                       | 27 |  |  |

| Fig. 2.3                                                                                                                              | 6T SRAM based IMC schematic showing bitline computing                                                                                                                                                                                                                                                                      | 30 |  |  |

| Fig. 2.4                                                                                                                              | Schematic of SRAM based IMC using local and global bit lines showing bitline computing.                                                                                                                                                                                                                                    | 30 |  |  |

| Fig. 2.5                                                                                                                              | Variation of (a) drain current w.r.t external gate voltage of<br>baseline JLFET, (b) internal gate voltage with external gate<br>voltage, (c) drain current w.r.t gate voltage of NC JLFET for<br>distinct gate lengths. Symbol ( $\Delta$ ) denote simulation results<br>whereas lines (–) represent the developed model. | 32 |  |  |

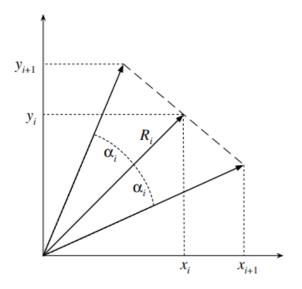

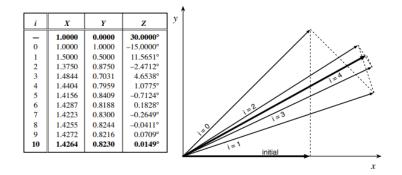

| Fig. 3.1                                                                                                                              | <i>i</i> <sup>th</sup> step iteration in cordic algorithm                                                                                                                                                                                                                                                                  | 37 |  |  |

| Fig. 3.2                                                                                                                              | The CORDIC Rotation mode                                                                                                                                                                                                                                                                                                   | 40 |  |  |

| Fig. 3.3                                                                                                                              | Cordic Vectoring Mode                                                                                                                                                                                                                                                                                                      | 42 |  |  |

| Fig. 3.4                                                                                                                              | Functions that can be computed using the CORDIC algorithm                                                                                                                                                                                                                                                                  | 46 |  |  |

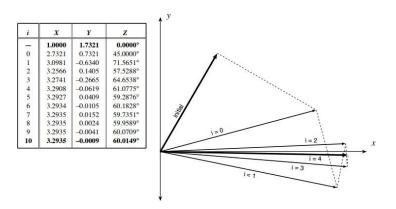

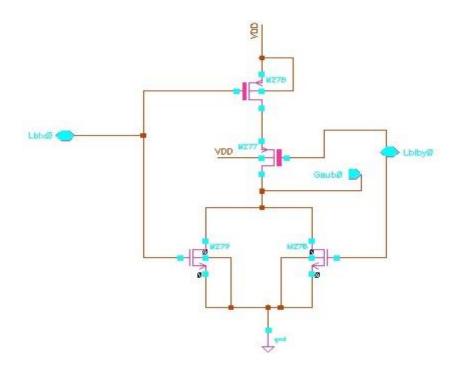

| Fig. 4.1                                                                                                                              | Schematic for obtaining carry propagator(P) and sum output from global bitlines and carry input                                                                                                                                                                                                                            | 48 |  |  |

| Fig. 4.2                                                                                                                              | Schematic for obtaining sum output by performing XOR operation of P and $C_i$                                                                                                                                                                                                                                              | 48 |  |  |

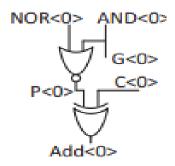

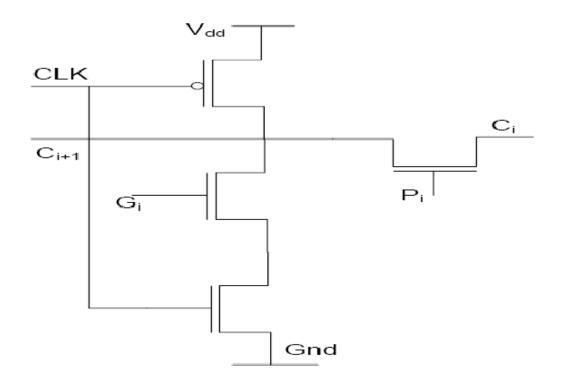

| Fig. 4.3                                                                                                                              | Schematic of Dynamic Manchester carry adder                                                                                                                                                                                                                                                                                | 50 |  |  |

| Fig. 4.4                                                                                                                              | Glitches due to floating intermediate node                                                                                                                                                                                                                                                                                 | 51 |  |  |

| Fig. 4.5 | Schematic of Dynamic Manchester carry adder                                                                                                           | 52 |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

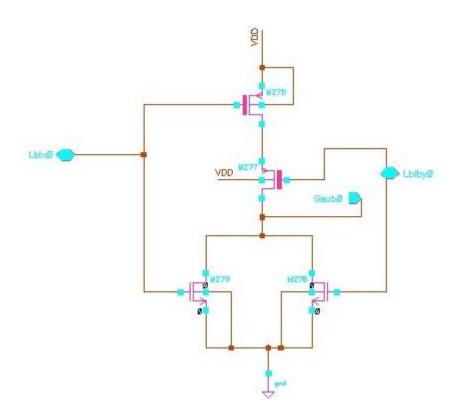

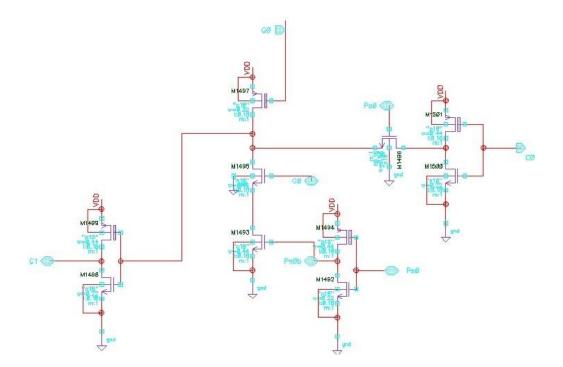

| Fig. 4.6 | $G_{sub}$ or $G_b$ or (Xbar.Y) generation using local bitlines of proposed In-SRAM IMC architecture                                                   | 54 |

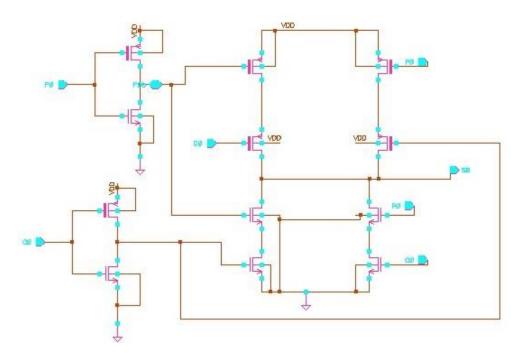

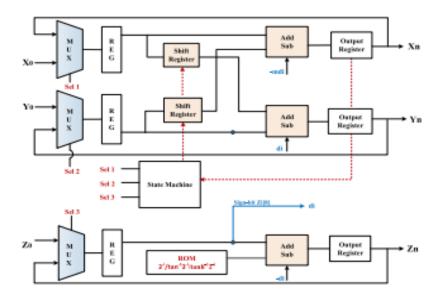

| Fig. 5.1 | Sign N-bit precision recursive CORDIC architecture that<br>can realize multiply- accumulate computation in linear<br>mode ( $m = 0 \& E_i = 2^{-i}$ ) | 56 |

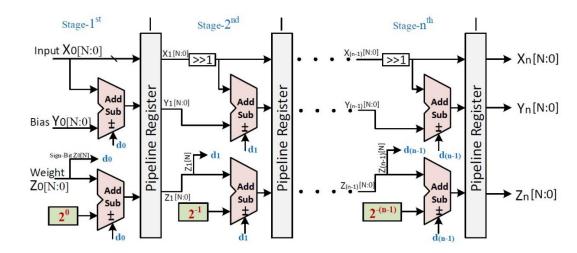

| Fig. 5.2 | n-stage pipelined MAC design using CORDIC algorithm                                                                                                   | 57 |

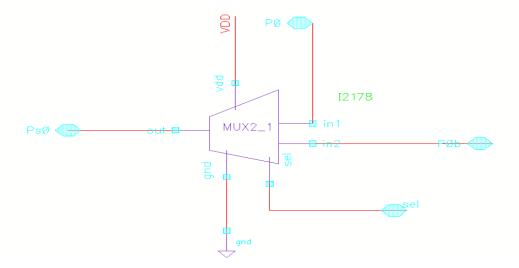

| Fig. 5.3 | MUX for selecting $P_0(adder)$ or $P_{0b}(subtractor)$ with select pin                                                                                | 60 |

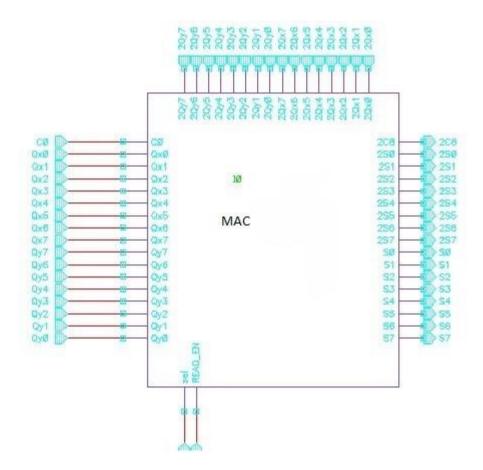

| Fig. 5.4 | Generation of MAC symbol                                                                                                                              | 62 |

|  | <br> |

|--|------|

|  |      |

|  |      |

|  |      |

## LIST OF TABLES

| Table<br>No. | Table Title                                                                                                                                                                                                     | Page No. |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Table 4.1    | Operation of Manchester Carry Adder                                                                                                                                                                             | 53       |

| Table 4.2    | Adder and subtractor outputs for X and Y operands                                                                                                                                                               | 53       |

| Table 5.1    | For high-performance MAC operation, iteration-level calculation is given for MAC computation using CORDIC in linear mode for fixed (8, 7) representation Processing at each nth stage in pipeline architecture. | 61       |

| Table 6.1    | Network Inference Accuracy                                                                                                                                                                                      | 64       |

| Table 6.3    | Delay comparison for the proposed design and the state-<br>of-the-art for MAC computation @45nm TT process<br>corner for 8-bit precision.                                                                       | 65       |

| Table 6.4    | Variation of Dynamic power with voltage TT process corner for 8-bit precision                                                                                                                                   | 65       |

| Table 6.5    | Computation of MAC using CORDIC and IMC for fixed point representation                                                                                                                                          | 66       |

| Table 6.6    | Computation of MAC using CORDIC and IMC for fixed point representation for different input, bias and weight                                                                                                     | 66       |

### **Chapter 1**

## **INTRODUCTION**

#### **1.1 Artificial Intelligence**

In recent years, artificial intelligence (AI) has gained traction. The modern world has been transformed by artificial intelligence (AI) and machine learning (ML). There has been great improvement in this field during the last twenty to thirty years. AI and machine learning are now applied in a variety of industries, including cancer detection and speech recognition. The immense quantity of processing power and the vast amount of data available have enabled this phenomenal expansion. Computers can learn from data and improve themselves using AI and machine learning techniques. These algorithms are capable of foreseeing the future.

Artificial intelligence (AI) is the simulation of human intelligence in machines that are programmed to think and act like humans. AI is a term used to describe any machine that mimics human mental functions such as learning and problem-solving. Beyond artificial intelligence, rationalizing and acting with the best possibility of achieving a given goal is a desirable characteristic. Machine learning is a subset of artificial intelligence that refers to the concept of computer programs learning and adapting to new data without the need for human intervention. Deep learning technology automates learning by ingesting massive volumes of unstructured data including text, photos, and videos.

When most people hear the term "artificial intelligence," they immediately think of a robot. This is due to the fact that high-budget films and novels depict human machines destroying the planet. Nothing, however, can conceal the reality.

Artificial intelligence is founded on the idea that human intelligence may be described in such a way that machines can readily copy and accomplish activities ranging from simple to sophisticated. The purpose of artificial intelligence is to mimic human cognitive capacities. Researchers and developers in this discipline are making rapid progress in precisely defining behaviors like learning, reasoning, and cognition. Some experts think that in the near future, developers will create systems that can learn or reason about any subject beyond human capabilities. Others, on the other hand, are skeptical because all cognitive activity have values derived from human experience.

As technology progresses, earlier artificial intelligence criteria become obsolete. Machines that calculate basic calculations or recognize text using optical character recognition, for example, are no longer called artificial intelligence because these functions are now regarded standard computer functions.

AI is constantly improving to benefit a wide range of sectors. A multidisciplinary approach based on mathematics, computer science, linguistics, psychology, and other disciplines is used to wire machines.

#### **1.1.1** Applications of Artificial Intelligence

The possibilities for AI are infinite. This technology is utilised in numerous domains and industries. In the healthcare industry, AI is being tested and used to dispense drugs and treatments to patients as well as execute surgical procedures in the operating room.

Computer chess and self-driving automobiles are two further instances of artificial intelligence machines. Because each action has an impact on the final result, each of these machines must evaluate the results of one of the tasks. The outcome in chess is victory. To operate in anti-collision mode, autonomous vehicles' computer systems must consider and calculate all external data.

Artificial intelligence can also be used in the finance sector. It helps banks fight fraud by detecting and marking debit cards and big account deposits that engage in unusual banking and financial activity. Trading was made easier and simpler with AI software. This is accomplished through expediting the appraisal of securities' supply, demand, and price.

#### 1.1.2 Categorization of Artificial Intelligence

Artificial intelligence can be classified into two types: weak and powerful. Weak artificial intelligence is a system that is meant to perform a single task. Video games, such as the chess example above, and personal assistants, such as Amazon's Alexa and Apple's Siri, are examples of weak AI systems. When you ask the assistant a question, it responds. Artificial intelligence systems that are robust perform tasks that are considered human-like. These are typically more complex and difficult systems. They are programmed to handle circumstances in which they may be required to solve problems without the assistance of a human. Self-driving cars and hospital operating rooms are examples of uses for these technologies.

#### **1.2 Machine Learning**

Machine learning is an artificial intelligence (AI) technology that allows systems to learn and improve on their own, without the need for programming. Machine learning tries to create computer algorithms that can utilise data to learn for themselves. The learning process starts with observations or data, such as examples, direct experience, or instruction, in order to find patterns in data and make better decisions in the future based on the examples we provide. The basic goal is for computers to learn on their own, without the need for human involvement, and to change their behavior accordingly.

#### **1.2.1** Supervised Machine Learning algorithms

This method includes a label identifying the desired solution for each case in the training data entered into the system. The data is primarily divided into two categories: training data and test data (score data). A model or theory is refined via training packages. This assumption is nothing more than a pedagogical mathematical statement. We examine the mistake while evaluating the model (the difference between the expected value and the value collected by the model). The goal of the training is to refine the model to achieve the lowest possible error. Training tests are used to evaluate education. The actual data can then be used to perform the appropriate function (prediction, distribution, etc.).

#### 1.2.2 Unsupervised Learning

The polar opposite of supervised learning is unsupervised learning. The training data does not include labels in this case. The system must learn on its own. These are essentially data point grouping strategies. Let's imagine you have a lot of client information on your website or in your store. You can use the clustering method to locate a group of clients who are similar to each other. You may see which customers you've worked with the most using this method. This categorization can be used to create marketing campaigns.

Detecting discrepancies is another crucial challenge. Credit card fraud detection, industrial defect detection, and data analytics data detection and discovery are just a few examples.

#### 1.2.3 Semi-supervised Learning

This is when the majority of the training data is unlabeled, with only a few labelled. As a result, most semi-supervised learning algorithms combine

supervised and unsupervised learning techniques. One of the better instances of supervised learning is Google Photos. If you tag a person's name on a photo, Google Photos can detect that person's face and display all of their photos.

#### 1.2.4 Reinforcement Learning

Reinforcement learning differs significantly. This is the area where the system can work. You are awarded or punished depending on your actions. The system then changes the policy with recommended and prohibited behaviours. This process continues until you determine the best course of action for your scenario. Booster learning is commonly used by robots to learn how to walk.

#### **1.3 Deep Neural Network**

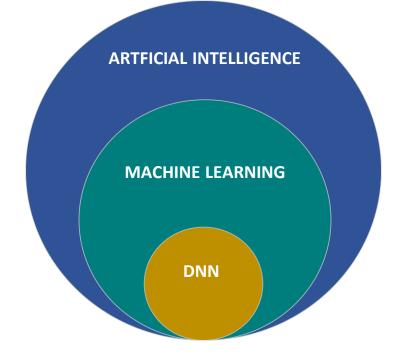

Many recent AI applications are built on the foundation of deep neural networks (DNNs). The number of applications using DNNs has exploded since the creative use of DNNs for image classification and speech recognition. DNNs are employed in a variety of applications, including selfdriving automobiles and cancer diagnosis. DNNs can now outperform humans in many of these domains. DNN's outstanding performance stems from its capacity to extract high-level features from raw sensory data after statistical training on vast volumes of data in order to efficiently represent the input space. This is in contrast to the prior approach, which relied on pre-made features or regulations. Higher DNN accuracy, on the other hand, increases computational complexity. Although general-purpose computers, particularly graphics processing units (GPUs), have long formed the backbone of DNN processing, there is growing interest in giving more specialized acceleration to DNN computers. D.N.N. (also known as deep learning) is a large branch of AI, science, and technology that aims to create intelligent machines that can attain human-made goals, according to computer scientist John McCarthy. Figure 1.1 depicts deep learning relationships with all artificial intelligence.

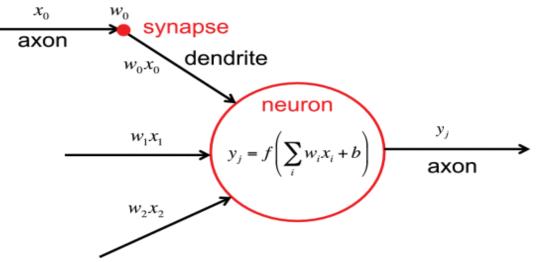

The brain is continually being studied by scientists. Neurons, on the other hand, are commonly recognized as the brain's primary computing component. The human brain has roughly 86 billion neurons on average. As illustrated in Figure 1.2, neurons are connected to multiple pieces called dendrites and contain output elements called axons. Neurons receive signals from the dendrites and process them in order to generate signals in the axons. Activation is the term for these inputs and outputs. Neuron axons spread out and connect to the dendrites of numerous other neurons. A synapse is the connection between the axon's branches and the dendrites. The typical number of synapses in the human brain is 1014 to 1015. The advantages of efficient machine learning algorithms are apparent. Instead of the laborious and random

Figure 1.1: Deep learning in the context of artificial intelligence [91]

way of creating one individual program to solve each problem in the domain, a single machine learning algorithm must learn how to handle each new problem through a process called learning. A branch of machine learning known as brain-inspired computing exists. Because the brain is the most wellknown "machine" for learning and problem solving, it's only reasonable to explore for machine learning techniques. Thus, brain-inspired computing is a program or algorithm that works in some way similar to how the brain works in its most basic form. This is not an attempt to build a brain; rather, the program seeks to simulate some parts of learning how the brain works.

The synapse's most important function is to modify the scale it goes through (xi), as seen in Figure 1.2. This evaluation actor may relate to weight (wi). It is thought that the brain learns through changes in synaptic pressure. As a result, different input responses correspond to different weights. The tissues in the brain (what we call programs) remain the same as learning regulates pressure in response to learning cues. This property makes the brain an excellent source of ideas for machine learning systems. Peak computing is a sub-domain of the brain-inspired computing paradigm. The interaction between dendrites and axons is analogous to nail stimulation, which provides inspiration for this sub-area. The information delivered is not exclusively dependent on the spine's amplitude. Instead, it relies on the pulse's time and the fact that the neuron's calculations are based on a single value and the time link between the pulse width and additional pulses. IBM True North [65] is an example of a brain game-inspired initiative.

Figure 1.2: Connections to a neuron in the brain.  $x_i$ , wi, f(), and b are the activations, weights, nonlinear function, and bias, respectively [91]

#### 1.3.1 Neural Networks and DNNs

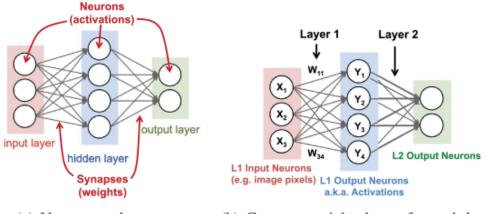

The idea of weighted inputs in neuron computations influenced neural networks. These weighted sums correspond to synaptic scaling values, which are then aggregated by neurons. Neurons only create weighted sums since the calculations involving the cascade of neurons are simple linear algebraic operations. Neurons, on the other hand, have functional operations that act on their combined inputs. This looks to be a nonlinear function, with neurons producing output only when the input exceeds a portion of the threshold. As a result, the neural network uses a nonlinear function that equals the weighted sum of the input values. A schematic example of a computational neural network is shown in Figure 1.3.

Finally, the user receives the final network output after the weighted amount is delivered from one or more hidden layers to the outgoing layer. The output of nerve cells is called activation to blend the brain-inspired phrase with a neural network. Activation/pressure designation is used in this article. In Figure 1.3 shows an example calculation at each level:  $y_j =$  $f(\sum_{i=1}^{3} W_{ij} * x_i + b)$ , where  $W_{ij}$ ,  $x_i$  and  $y_j$  are the weights, activate the input, activate the output. For simplicity, the phrase bias b has been removed from Figure 1.3.

Deep learning is a branch of neural networks in which the neural networks comprise three or more layers, i.e. two or more hidden layers. The number of network layers employed in deep learning today varies between 5 and over 1,000. The term Deep Neural Network (DNN) is used in this article to refer to neural networks typically employed in deep learning. DNNs can learn higher-level functions that are more complicated and abstracted than tiny neural networks. The usage of DNNs to process visual data is an example of this. Image pixels are fed into the DNN's first layer in such applications. The output of the layer can show different low-level image elements including lines and edges. These elements were blended at the next level based on the likelihood of the higher-level elements. Lines, for example, are blended into shapes, which are then combined into a set of shapes. Finally, given all of this data, the network is likely to contain specific objects or scenes. DNNs can achieve good performance in a variety of applications thanks to this deep layer of capability.

#### **1.4 Overview of DNNs**

Depending on the application, DNNs come in a range of shapes and sizes. Popular shapes and sizes are also continually evolving to improve precision and efficiency. The input to the DNN in both circumstances is a set of values that reflect the data to be evaluated by the network. Image pixels, sampling amplitudes for sound waves, or numerical representations of any system or game state are examples of these values.

Input processing networks are divided into two categories: feed and flatness. All calculations in the feedforward network are done as a sequence of actions on the previous output level. The final set of operations generates network output such as the likelihood that an image will contain a specific object, the likelihood that an audio sequence will contain a specific word, a bounding box around the object in the picture, or the steps that should be taken. The network in such a DNN has no memory. Regardless of the sequence of inputs previously delivered to the network, the input-output is always the same.

The circulatory neural network (RNN), also known as the short-term memory network (LSTM), on the other hand, has an internal memory where long-term dependency might affect outcomes. Some intermediate jobs are stored within these networks and generate values that are utilised as inputs to other input processing activities. The feed network will be the subject of this article since 1) the RNN's core calculation is still the weighted sum (i.e. matrix-vector multiplication) of the feed network. 2) Hardware acceleration of RNNs has received relatively little attention to far.

Only fully connected layers (FCs) [also known as multi-layer sensors (MLPs)] can be found in DNNs. Each output activation at the CC level comprises the sum of the weights of all input activations (i.e. all outputs are connected to all inputs). This necessitates a great deal of memory and bookkeeping. Fortunately, in many cases, the link between activations may be erased without impacting accuracy by setting the pressure to zero. As a result, a thin sticky coating is created. Bearings with thin contact.

Limit the number of weights that affect the outcome to make the calculation more efficient. Only if each output is a fixed size input window function can there be structural sparsity. Calculating each output with the same set of weights results in much improved efficiency. Weight sharing refers to the reuse of the same weight value and can greatly reduce balance sheet storage requirements.

Structured calculations in convolutions produce in a fashionable DNN layer with weight shared and windowed splitting, as shown in Figure 1.7. Only a small area of input activation is used to generate the weighted total for each output activation (i.e. all pressures out of range are set to zero). This area is also known as the "permitted area." Furthermore, all outputs use the same set of weights (e.g. the filter is an unchanged space). CONV stands for persuasion-based layers (Conv layers).

#### 1.4.1 **Convolutional Neural Networks**

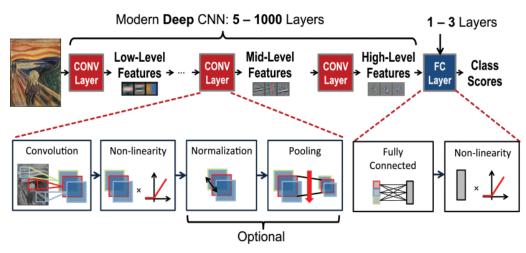

As shown in Figure 1.6, a Converged Neural Network (CNN) is a 10

common type of DNN made up of multiple CONV layers. Each layer in such a network produces a function map, which is a higher abstraction of input data (fmap). It saves crucial but unique data. Using very deep hierarchies, modern CNNs can achieve good performance. Image recognition [48], speech recognition [82], gaming [88], and robotics [55] are just a few of the areas where CNNs are employed.

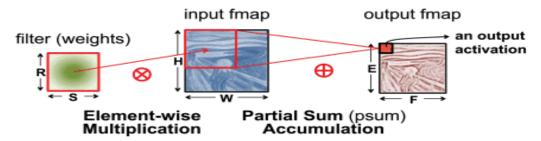

As demonstrated in Figure 1.7, each CONV layer in a CNN is mostly made up of multidimensional beliefs. The layer input operation in this calculation is made up of two-dimensional input function maps (ifmaps), each of which is referred to as a channel. Each channel is combined into a filter bank and a separate 2D filter. A single 3D filter is typically referred to as a collection of 2D filters. The conviction findings are summarized in each channel at each point. You can also give the filter results a one-dimensional offset. Some modern networks [34] do not allow them to be used in storage compartments. This calculation is the activation of the output data in the output function map., which forms a channel (ofmap).

Additional output channels for the same input can be formed using additional 3D filters. Finally, multi-input function maps can be combined into a package that reuses filter weights.

(a) 2-D convolution in traditional image processing

(b) High dimensional convolutions in CNNs

Figure 1.5: Dimensionality of convolutions. (a) 2-D convolution in traditional image processing. (b)High dimensional convolutions in CNN [91]

Figure 1.6: Convolutional neural networks

DNNs feature extra levels such as nonlinearity, aggregation, and normalization in addition to the CONV and CC levels. Each of these layers' functions and calculations are outlined below.

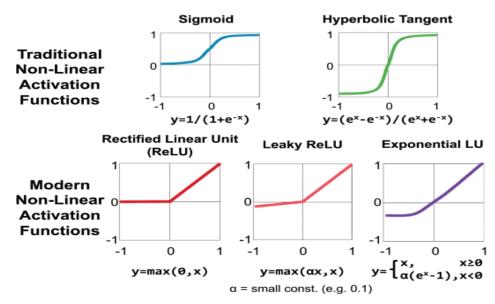

1) Nonlinearity: After each CONV or CC level, the nonlinear activation function is frequently used. Figure 1.7 shows how to introduce nonlinearities for DNNs using various nonlinear functions. Traditional nonlinear functions like sigmoid or hyperbolic tangent, as well as modified linear units (ReLU) [68], have recently gained prominence. Because of its simplicity and capacity to deliver quick learning, it has been popular throughout time. To increase accuracy, many ReLU variations such as ReLU leakage [62], parametric ReLU [35], and exponential LU [16] have been examined. Finally, in speech recognition difficulties, a nonlinearity known as max out, which takes the maximum value of two intersecting linear functions, is effective [107], [108]

2) Pooling: A unit is a calculation of variables that reduces the dimension of a function map. The network can endure slight changes and distortions because to individual channel bonding. Unions reduce the number of values in the receiving field by combining or matching them. It can be changed to fit the size of the receiving fields (e.g. 2x2) and join procedures indicated in Figure 1.10. (e.g. max or average). When blocks, not blocks, overlap, interconnection occurs (i.e. the steps are the same). Pool Dimensions) One or more summits are usually used, resulting in limited views (e.g. functional maps).

3) Normalization: Managing the distribution of input data across multiple layers can significantly speeding up training and increase accuracy. As a result, the layer's input activation distribution ( $\sigma$ ,  $\mu$ ) is normalized to have a mean value of 0 and standard deviation. In batch normalization (BN), the normalized values are shifted and scaled, as shown in the figure. Here the parameters ( $\gamma$ ,  $\beta$ )

Figure 1.7: Various forms of nonlinear activation functions

is learned during training. is a small constant to avoid numerical problems. In the past, local response normalization (LRN) was used, inspired by lateral neuroscience suppression. The nerve cells fired here (i.e., high-value activation) must weaken neighboring cells (i.e., stimulate low-value activation). However, BN is now considered standard practice in CNN design, while LRN is mainly out of date. LRN is usually done after the nonlinear function. However, BN is mainly done between the CONV or CC level and the nonlinear function. Suppose BN is implemented immediately after the CONV or CC level. In that case, its calculation can be combined with the CONV or CC level pressure without further calculation.

#### **1.5 DNN Development Resources**

Several deep learning frameworks have been developed to make DNN creation easier and to share trained networks from multiple sources. The DNN programming library is one of these open-source libraries. The University of California at Berkeley (UC Berkeley) [42] opened Caffe in 2014. C, C++, Python, and MATLAB are all supported. Google introduced Tensorflow in 2015, which supported C++ and Python. It is more flexible than Caffe and supports multiprocessors and GPUs, with computations described as dataflow charts to handle tensors (multidimensional matrices). Torch, created by Mozilla, is another prominent framework.

| 272 | poolin | y, sui |   |             |    |    |                      |    |    |  |

|-----|--------|--------|---|-------------|----|----|----------------------|----|----|--|

| 9   | 3      | 5      | 3 | Max pooling |    |    | ling Average pooling |    |    |  |

| 10  | 32     | 2      | 2 |             | 32 | 5  |                      | 18 | 3  |  |

| 1   | 3      | 21     | 9 |             | 6  | 21 |                      | 3  | 12 |  |

| 2   | 6      | 11     | 7 |             |    |    |                      |    |    |  |

2x2 pooling, stride 2

Figure 1.8: . Various forms of pooling [91]

#### 1.5.1 Frameworks

The existence of these Frameworks is beneficial not only to DNN researchers and developers. It is, nonetheless, critical for the development of high-performance or more efficient DNN computing processes. Because they make substantial use of a set of basic operations such as CONV level manipulation, frames can include optimised software or hardware accelerators. The frame user is unaware of the acceleration. Most frames, for example, can take advantage of Nvidia's cuvNN library to operate Nvidia GPUs quickly. Unique hardware accelerators can also be transparently integrated, as with the Eyeriss chip [11].

Finally, these Frameworks provide hardware researchers with a rich source of workload. It can create prototype projects for various workloads, profile various workloads, and investigate software and hardware trade-offs.

#### **1.5.2** Popular Data Sets for Classification

When comparing different DNN models, it's vital to keep the data complexity in mind. For example, in the MNIST dataset [51], writing numbers is significantly easier than assigning an object to one of the 1000 classes required in the ImageNet dataset [81]. (Figure 1.9). For complex tasks, the DNN size (number of weights) and number of MACs are predicted to be bigger than for simple computations, requiring more power and bandwidth. For instance, LeNet-5 [53] is intended for image classification, while AlexNet [48], VGG-16 [89], GoogLeNet [94], and ResNet [34] are intended for image classification.

There is a large amount of AI data accessible that may be used to assess the accuracy of a certain DNN. Comparing the accuracy of various methods requires public data sets. Classifying your images is the simplest and most common process. To put it another way, select the 1N class that the image belongs to. There is no location or way to locate it.

MNIST is a numerical classification system that was introduced in 1998 [51]. It has a handwritten number image of 28x28 pixels. There are ten lessons (10 digits), 60,000 instructional images, and 10,000 test images in all. When MNIST was originally introduced, LeNet-5 had a 99.05 percent accuracy rate. Drop Connect has improved neural network management accuracy to 99.79 percent [99] since then. As a result, MNIST is currently considered a fundamental data collection.

CIFAR is a 2009 dataset of 32 by 32-pixel colour photographs of a variety of things [47]. CIFAR is a subset of 80 million Tiny Images data [95]. CIFAR-10 has ten classifications that are mutually exclusive. 50,000 class photographs (5,000 per class) and 10,000 test photos are available (1,000 per class). When it was first introduced, the two-part deep belief network had a CIFAR-10 accuracy of 64.84 percent [46]. Since then, using fractional max join [67], the accuracy has been increased to 96.53 percent.

Figure 1.9: MNIST (10 classes, 60000 training, 10000 testing) versus ImageNet (1000 classes, 1.3 million training, 100000 testing) data set

ImageNet is a massive data set that was originally released in 2010. Dataset from 2012. It has 1000 classes and a 256 256-pixel colour picture. The basis for grouping synonyms and manipulating ambiguous words in the same object category is WordNet classification. That is, ImageNet categories are organized in a hierarchy. The ImageNet hierarchy has been divided into 1,000 classes to avoid any overlap. There are many subcategories in the ImageNet dataset, including 120 different dog breeds. I have 1.3 million command images (732-1300 per class), 100,000 test photos (100 per class), and 50,000 test images in total (50 per class). The ImageNet Challenge reports the accuracy of the picture categorization task using two measures: Top-5 and Top-1 error.

The top 5 error indicates that if one of the top 5-point categories is the correct one, the classification is correct. Top 1 must be the category with the highest score. In 2012, the ImageNet Challenge winner had an accuracy of 83.6 percent in the top five categories (much better than 73.8 percent, second place this year without using DNN). Among 2017, the best accuracy in the top five was 97.7%. MNIST is a rather basic data collection, as evidenced by the summary of the various picture categorization data sets. ImageNet is a large data set with a wide range of classes. As a result, while assessing the accuracy of a given DNN, it's critical to consider the amount of data being evaluated.

#### 1.6 Hardware of DNN Processing

Many current hardware systems offer particular features for controlling DNNs as a result of their popularity. The Intel Knights Mill processor, for example, has unique deep learning vector instructions [20], and the Nvidia PASCAL GP100 GPU offers 16-bit Pour Point Count (FP16), which speeds up deep learning computations by doing two FP16 operations on a single high-precision core. There are also systems created expressly to manage DNNs, such as the Nvidia DGX-1 server and a specialised Facebook Big Basin DNN server [18]. DNN pins have also been seen in programmable gate arrays and other chip embedded (SoC) systems as as Nvidia Tegra and Samsung Exynos (FPGAs). As a result, it's critical to understand how these platforms handle data and how application-specific DNN accelerators can be created to boost throughput and reduce energy consumption.

MAC (multiplication and accumulation operation), which may be easily parallelized, is the essential component of CONV and FC bearings. To achieve high performance, an extremely parallel data paradigm is frequently utilised, including temporal and spatial structures, as shown in Figure 1.12. The timing architecture is mostly implemented on the CPU or GPU, and it employs vector (SIMD) or parallel approaches to increase concurrency. Yarn (SIMT). The central control of many ALUs is used in this ad hoc architecture.

These ALUs can only receive data from other ALUs in the memory hierarchy and cannot communicate directly. The spatial architecture, on the other hand, employs data flow processing. In other words, the ALU can build a processing chain, allowing data to flow from one location to another. A memo file or registry file can be used to store control logic and local memory for each LA. The Processing Machine refers to an ALU with local memory (PE). In ASIC and FPGA designs, spatial architecture is frequently employed for DNNs. This section discusses various design concepts for efficient machining on various platforms without compromising precision (i.e. all methods in this section give the same result). We explore how the computational transformation of the core minimizes the amount of multiplications to boost throughput for ad hoc architectures like CPU's and GPU's.We examine how data streams improve energy consumption by enhancing the memory hierarchy's reuse of inexpensive memory data for spatial topologies utilized in accelerators.

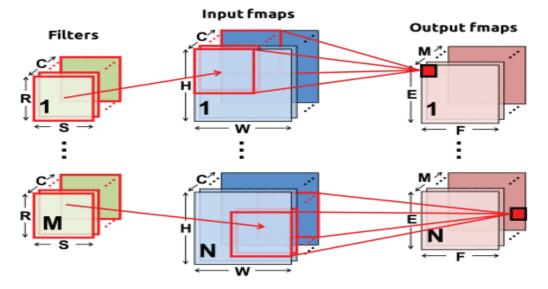

# **1.6.1** Accelerate Kernel Computation on CPU and GPU Platforms

Parallel technologies such as SIMD or SIMT are used to run MACs in parallel on the CPU and GPU. The same controls and memory are used by all LAs (registration file). The CC and CONV levels are frequently translated to matrix multiplication on various platforms (i.e. core computing). Matrix multiplication is shown in Figure 1.13 for NC layers. The number of 3D filters determines the filter matrix's height. The width is the number of weights per 3D filter [Input Channel (C) × Width (W) × Height (H), R = W andS = H are CC layers]; The height of the input function map matrix is the number of activations per 3D input function map (C × W × H). The width is the number of 3D input function maps [Figure 1.13]; Finally, the matrix height of the output function map is the number of channels in the output function maps. Each function here has a map function. CC layer dimension  $1 \times 1 \times$  number of output channels (M).

The CONV layer of the DNN can also be mapped to multiply the matrix with the weaker Toeplitz matrix depicted in the figure. 19. The input function map contains redundant data when matrix multiplication is used on the CONV layer. Figure 1.14 shows the matrix. This can result in inefficient storage or complicated memory access patterns.

The software library is optimised for matrix multiplication processors (such as Open-BLAS, Intel MKL, and GPUs) (e.g. cuBLAS, cuDNN, etc.). Matrix multiplication refers to the storage tier of these platforms, which is measured in megabytes at the highest level.

(a) Matrix Vector multiplication is used when computing a single output feature map from a single input feature map.

(b) Matrix Multiplications is used when computing N output feature maps from N input feature maps.

Figure 1.10: Mapping to matrix multiplication for fully connected layers(a) Matrix Vector multiplication is used when computing a single output feature map from a single input feature map. (b) Matrix Multiplications is used when computing N output feature maps from N input feature maps

(b) Extend Toeplitz matrix to multiple channels and filters

Chnl 2

Figure 1.11: Mapping to matrix multiplication for convolutional layers. (a) Mapping convolution toToeplitz matrix. (b) Extend Toeplitz matrix to multiple channels and filters

#### **1.7 Machine Learning Accelerators**

Machine learning algorithms, particularly Neural Networks, are processed or co-processed by ML accelerators. Earlier attempts at machine learning accelerators used digital signal processing to do pixel-to-pixel multiplication and accumulation. On computers, graphic processing units, or GPUs, provide acceleration. More specialized chips are being developed since the development of CNN. A quick explanation of various ML accelerator methodologies follows.

### 1.7.1 Heterogeneous Computing Platforms

Heterogeneous computing refers to a platform that combines many types of dedicated hardware, such as a CPU with GPU and DSPs. Over a single chip, an FPGA with a processor is embedded. Because the technique of ANN or CNN is similar to that of image processing, GPUs, which are built to handle image and video processing, are particularly efficient in implementing these algorithms. However, there are other trade-offs, including expense, area, and space. Because GPUs cannot be used as coprocessors in smartphone SoCs, the industry is collaborating with ASICs to integrate them into their platforms.

### **1.7.2** ASICs and FPGA

In the research field of ML accelerators, ASIC and FPGA are obvious alternatives. FPGAs are commonly utilised in servers and other applications. Furthermore, newer FPGA chips contain a processor, enabling for SW-HW co-design. Intel created Nervana and Movidius, two ASICs. NVIDIA has a division dedicated to smart vehicle hardware development. Novel Hardware for Artificial Neural Networks for FPGA or ASICs is discussed in the following chapters.

# **Chapter 2**

# **IN MEMORY COMPUTING**

The approach of performing computer calculations entirely in computer memory is known as **in-memory computation (or in-memory computing)** (e.g., in RAM). This word usually refers to large-scale, sophisticated calculations that necessitate specialized systems software to execute on multiple computers in a cluster. As part of a cluster, the computers pool their RAM so that the calculation is essentially done over multiple computers and takes advantage of the combined RAM space of all the machines.

In-Memory Computing permits for remarkable results (multiple times faster) and indeed the extent of never-ending amounts of data, but also greater accessibility to an increase in information sources. It provides real-time insights by backing up through RAM but also encoding it in parallel, allowing providers to connect immediate responses to events. This creates opportunities that could be used in descriptive and predictive programs that share the same technology platform, as well as transaction - oriented data management guided by legit analytics.

# 2.1 The Emergence of In-Memory Computing

In-memory computing, or IMC, is becoming increasingly prevalent. This is attributable to higher demand for accelerated big information processing and predictive analysis, the need to refine layout as the number of data references rises, and advancements in technology that are lowering TCO.

# 2.2 Objective of In-Memory Computing

To achieve a sustainable competitive advantage and fulfil present and future

needs for highest quality of service, manufacturers must cope with the steady increase in the efficiency statistics and the never-ending perceptions for faster and accurate performance.

As a result, In-Memory cloud services technologies are gaining traction. Because the primary objective of In-Memory computing is to acquire and scrutinize a vast amount of information in a brief period.

Traditional business intelligence (BI) programs, which are typically focused on disc storage and database systems which use the SQL database language, are impractical for today's BI requirements, that include super-fast query processing and reliable data scalability.

In-memory processing relies solely on data stored in RAM and eliminates all slow data accesses. By eliminating the latency that is common when accessing hard disc drives or SSDs, overall computing performance is considerably enhanced. The calculation as well as the data in memory are managed by software running on one or more computers, and in the event of multiple computers, the programme breaks the computation into smaller jobs that are sent to each computer to run in parallel. In-memory computing is frequently performed using in-memory data grids (IMDG). Hazelcast IMDG is one such example, which allows users to conduct sophisticated computations on massive data sets over a cluster of hardware servers at breakneck speed.

## **2.3 IMC's Fundamental Principles and Prominence**

Data storage and expandability — a software's, network's, or application's capacity to maintain consistently advancing amounts of information, or its potential to be elastically enhanced to accommodate that expansion — are the foundations of in-memory computing. This is accomplished using two major technologies: Parallelization and random-access memory (RAM).

Figure 2.1: Basic Principles and Significance of IMC

High Speed and Scalability: In-Memory Computer technology exhibits excellent functionality and reliability by gathering data in RAM and archiving it. This is more than 100 times faster than any other solution for data processing and querying, guaranteeing effective and unparalleled functionality for any task.

For scalability, In-Memory Computing hinges on parallelized distributed processing, which is vital for massive data processing. Distributed data transformation, as opposed to a single, centralized database managing and providing computing technology to all linked systems, is a computernetworking platform where several computers located in different locations share computing resources.

Real-time Insights: IMC incorporates business logic, predictive analysis, and collected from a range of source information (multi-model store). In this context, In-Memory Computing is so much more than just providing a faster analysis than before; but also, about becoming significant predictors during the analysis process!

By addressing massive amounts of broadcasting, hot, and historical data in real - time, IMC enables for real-time experienced data analysis and machine learning for quick perspectives that are instantaneously used by networked business logic with the memory fabric. Whenever something ends up happening that has the potential to impact company's operations, customer behaviour, regulatory compliance, and other factors, an instant acknowledgment of the effects and consequences is provided, allowing for quick reaction and decisionmaking.

Furthermore, consistent predictive modelling, which takes advantage of the opportunity to process and analyse millions of events per second, helps to minimize undesirable consequences such as equipment breakdown, customer churn, and computer hackers, among other things.

A Wide Range of Applications: Of course, in-memory computing is beneficial to companies that deal with large amounts of data, particularly those in consumer-facing sectors such as retail, financial sectors, insurance, transportation, telecommunications, and utilities. Risk and transaction management in financial institutions, payment and insurance fraud detection, consumer product trade promotion simulations, and real-time/personalized advertising are all examples. In-Memory Computing, on the other hand, can profit greatly any industry or market where proper analysis, perspectives, and predictions based on broadcasting and historical data deliver economic potential, such as geographic information analysis, preventive analytics, and network optimization in transportation.

Enabling Technology: Without the implementation of IMC, many of today's methods and services would not be possible. Applications that use blockchain based (which enables digital information to be distributed but not duplicated) or apps that use geospatial/GIS processing for transportation contain this enabling technology function (such as real-time direction on recommended route, traffic congestion and hazard).

## 2.4 SRAM Based IMC

Data transport consumes over a hundred times as much energy as math. As a result, data-movement overheads have significantly limited the performance of traditional "von-Neumann type" compute-centric processors. When using SRAM-IMC in pattern-matching applications, the automata state transitions take place entirely within the memory. This eliminates the expense of division mispredictions and unusual memory accesses in CPU-based processing. We can also use a connector with high fan-in and fan-out to connect an input vector with several candidate sequences. SRAM-IMC can thus provide significant parallelism. Operations can help with cryptographic techniques, graph indexing, and database applications. Executing search and comparison activities in memory can help compression, encrypting, and search engines. IMC-based logical procedures can help with cryptography, graph indexing, and database applications.

The IMC based on SRAM can use 6T, 8T, or 10T SRAM. However, there are serious concerns with read disturbance and read noise margin erosion. The next sections go over several SRAM architectures.

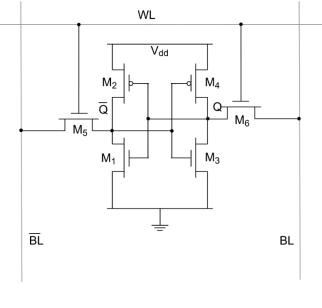

## 2.4.1 6T SRAM

SRAM known as static random-access memory and provides bistable latching circuitry to store each bit. The term "static RAM" distinguishes it from "dynamic RAM," which includes constant replenishment. SRAM can store data, but it is still volatile in the sense that data will be lost when the memory is turned off.

Fig 2.2 Schematic of 6T SRAM 27

Three modalities are available for the 6T SRAM cell: (1) Standby mode (2) Read Operation

(3) Write Operation

#### (1) Standby mode

Word line is not asserted in standby mode (word line=0), so the pass transistors M5 and M6, which connect the 6t cell to the bit lines, are disabled. This indicates that the cell can't be accessed. As long as the two cross-coupled inverters are connected to the supply, they will continue to feedback each other, and data will remain in the latch.

#### (2) Read Operation

In read mode, the word line (word line=1) is asserted, enabling both the access transistors that connect the cell to the bit lines. Values in nodes (Q and Q bar) are now moved to bit lines. Assume 1 is stored at node 'Q,' therefore the bit line bar will discharge through the driver transistor (M1) and is pulled up through the Load transistors (M2) toward VDD, resulting in a logical 1. SRAM cell design necessitates read stability (do not disturb data when reading).

#### (3) Write Operation

- Assume that the cell was originally set to store a 1 and that we want to change it to a 0. To do so, lower the bit line to 0V and elevate the bit bar to VDD, then pick the cell by elevating the word line to VDD.

- Inverter threshold is often fixed at VDD/2 since each inverter is designed to match PMOS and NMOS. M5 functions in saturation if we want to write 0 at node a. Its source voltage is set at 1 at first. M3's drain terminal is originally set to 1, but M5 pulls it down because M5 is a stronger access transistor than

M1. Now that M3 is on and M2 is off, a new value has been written, causing the bit line to be dropped to 0V and the bit bar to be set to VDD. To operate in write mode, SRAM must have write-ability, which is defined as the minimal bit line voltage required to flip a cell's state.

#### **Disadvantages of 6T SRAM**

Two separate back-to-back inverters (two pull-up PMOS and two pull-down NMOS transistors) and two NMOS connect transistors associated to the bitlines with the gates linked to the wordline can be seen in Figure 2.2. During read, the wordline has been stated, and the change in voltage between bitlines is detected by a sensing amplifier. In the read cycle, access transistors and pull-down transistors are being used. Greater pull-down transistors (PDL and PDR) and poorer access transistors enhance RSNM. On the other hand, WM is improved by better access transistors and poorer pull-up transistors. Because of the added capacity, the SRAM cell can implement at quite low supply voltages (i.e. low VDDmin) with negligible threshold voltage volatility, albeit at the cost of much more space. SRAM cell stability had already deteriorated markedly, particularly at lower voltages, as process variations through sub-100 nm technologies continue to grow.6T SRAM memory-based IMC solutions struggle with read disturb information leakage, restricting profitability for low-power or high-performance applications.

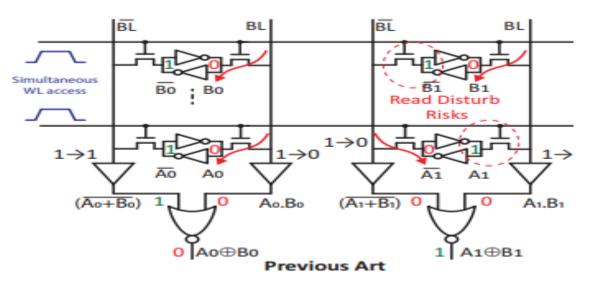

## 2.5 SRAM based IMC using local and global bit lines

Following a precharge phase to Vdd, IMC operations can be performed in standard SRAM memories by additively accessing two WLs. Based on the states of the available bitcells, either of the BLs are discharged, as shown in Figure 2.3. Finally, the outcome of an AND implementation is contained in the BL (or BL bar) (respectively NOR). These processes are the foundation of

bitline computing. As implemented to typical 6T bitcells in contrary states, the PMOS transistor of one bitcell seems to be poorer than that of the connectivity and pulldown transistors of all other bitcell, the cell may swap, associated with information corruption. This impact can indeed be illustrated using variation models, notably as in slowP-FastN CMOS corner.

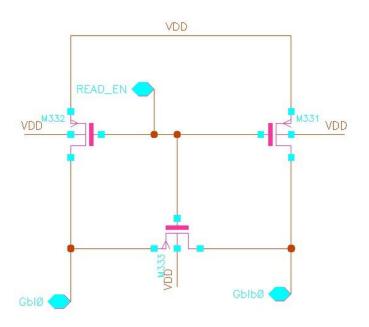

Fig 2.3: 6T SRAM based IMC schematic showing bitline computing

Fig2.4: Schematic of SRAM based IMC using local and global bit lines showing bitline computing.

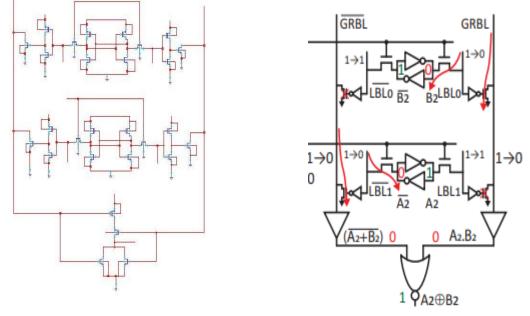

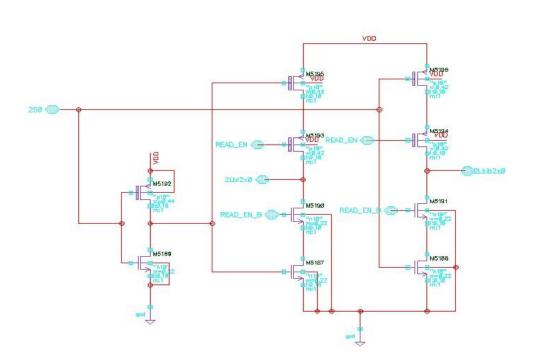

SRAM centered IMC utilizes local and global bit lines to perform bitline computing-based IMC activities with 6T SRAM bitcells while ignoring read disturb issues. The two major bitcells in this architecture have always been connected to multiple LBLs, as shown in fig 2.4, reducing the risk of bitcell shorting. Within an LBL, an IMC procedure is much like a conventional read. Both of the GRBLs then are discharged through the read ports, based on the states of the convenient bitcells. As earlier stated, the GRBL (resp. GRBL) presents the conclusion of an AND (resp. NOR) in between two operands. This method allows the WL to cover its entire dynamic voltage range while avoiding the use of 10T bitcells.

#### 2.5.1 Advantages of fast and reliable IMC design

With this innovative in-SRAM IMC design, you can perform bitwise, addition, shift, and copy activities in memory. It could be used to make a 28nm mass elevated CMOS technology PDK, and its functionality can be demonstrated utilising CMOS variance and layout aware simulations.