# B. TECH. PROJECT REPORT On PERFORMING MATHEMATICAL OPERATIONS AND PARALLELISING THEM ON FPGA

BY PALASH DURUGKAR SUNIL KUMAR PAL

DISCIPLINE OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE December 2017

# PERFORMING MATHEMATICAL OPERATIONS AND PARALLELISING THEM ON FPGA

# A PROJECT REPORT

Submitted in partial fulfillment of the requirements for the award of the degrees

of BACHELOR OF TECHNOLOGY in ELECTRICAL ENGINEERING

> Submitted by: PALASH DURUGKAR SUNIL KUMAR PAL

> > Guided by:

Dr. SRIVATHSAN VASUDEVAN, Faculty, Electrical Engineering DR. SATYA BULUSU, Faculty, Chemistry Department

# INDIAN INSTITUTE OF TECHNOLOGY INDORE December 2017

# **CANDIDATE'S DECLARATION**

We hereby declare that the project entitled "**Performing Mathematical Operations and Parallelizing Them in FPGA**" submitted in partial fulfillment for the award of the degree of Bachelor of Technology in 'ELECTRICAL ENGINEERING' completed under the supervision of **Dr. Srivathsan Vasudevan, Asst. Professor, Electrical Engineering** and **Dr. Satya Bulusu, Asst. Professor, Chemistry,** IIT Indore is an authentic work.

Further, I/we declare that I/we have not submitted this work for the award of any other degree elsewhere.

Signature and name of the student(s) with date

**Palash Durugkar**

Sunil Kumar Pal

## **CERTIFICATE by BTP Guide(s)**

It is certified that the above statement made by the students is correct to the best of my/our knowledge.

Signature of BTP Guide(s) with dates and their designation

Dr. S. Vasudevan

Asst. Professor, Electrical Engg.

**IIT INDORE**

Dr. S. Bulusu

Asst. Professor, Chemistry

**IIT INDORE**

# **PREFACE**

This report on "PERFORMING MATHEMATICAL OPERATIONS AND PARALLELISING THEM IN FPGA" is prepared under the guidance of Dr. Srivathsan Vasudevan, Professor, Electrical Engineering and Assistant Professor, Dr. Satya Bulusu, Professor, Chemistry Department.

Through this report we have tried to present the system and architecture for solving intensive high-level computation problems for various computational fields. The system is an effort towards making such computational fields realize the potential of application of FPGA based hardware designs and their optimizations for mathematical problem computations and data analysis.

We have tried to the best of our abilities and knowledge to explain the content in a lucid manner. We have also added designs and figures to make it more illustrative.

# PALASH DURUGKAR and SUNIL KUMAR PAL

B.Tech. IV Year Discipline of Electrical Engineering IIT Indore

# **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my supervisors Dr. Srivathsan Vasudevan and Dr. Satya Bulusu for providing their invaluable guidance, comments, suggestions and kind support throughout the course of the project.

It is through their help and support, due to which we became able to complete the design and technical report.

Without their support this report would not have been possible.

# PALASH DURUGKAR and SUNIL KUMAR PAL

B.Tech. IV Year Discipline of Electrical Engineering IIT Indore

# **ABSTRACT**

With the rise of Field Programmable Gate Array (FPGA) Programming, the application of hardware designing and implementation is becoming ubiquitous. FPGA can be used to design a controller in a single chip Integrated Circuit (IC). Most of the research oriented fields today, involve intensive high-level computation problems to be solved within minimum possible time frame and greatest of ease. This project on Performing of Mathematical Operations and parallelizing them in FPGA, is considered to be a key problem solver for such fields. Through this work, we aim to offer an architecture of a setup which could perform a pre-specified mathematical operation or a set of mathematical operations on large chunks of data packets within very low time frames. This paper deals with designing of a high speed UART using Verilog Hardware Description Language .The Universal Asynchronous Receiver Transmitter (UART) is a device used for serial communication between computers and other peripheral devices. Together combining the design structure and parallelizing techniques to reduce latency and optimization on FPGA, would be considered a new innovation idea in intensive high-level computational fields by providing a reprogrammable software that can demonstrate the potential of hardware development and FPGA programming.

# TABLE OF CONTENTS

- i. Candidate's Declaration

- ii. Supervisor's Certificate

- iii. Preface

- iv. Acknowledgements

- v. Abstract

- 1. Introduction

- 1.1. FPGAs-A Brief Introduction

- 1.2. Basys 3 Board

- 1.3. XILINX Vivado Design Suite

- 1.4. RealTerm Serial/TCP Terminal Software

- 2. Design Implementation Using HDLs(VHDL /Verilog)

- 3. Design Implementation using HLLs(C/C++)

- 4. Applications

- 5. Conclusion and Scope for Future Work

- 6. References

## LIST OF FIGURES

- Figure 1 Island Type View of FPGA Architecture

- Figure 2 FPGA Components

- Figure 3 Logic Cell

- Figure 4 Basys 3 Board Features

- Figure 5 USB-UART Connection on FPGA

- Figure 6 RealTerm Screen Capture

- Figure 7 Structure Overview

- Figure 8 Data Flow in the System

- Figure 9 Steps Followed in using the software

- Figure 10 Data Packet in UART

- Figure 11 Final Synthesised Design of System

- Figure 12 State Machine Representation of Control Module

- Figure 13 RTL level design of system

- Figure 14 I/O Planning

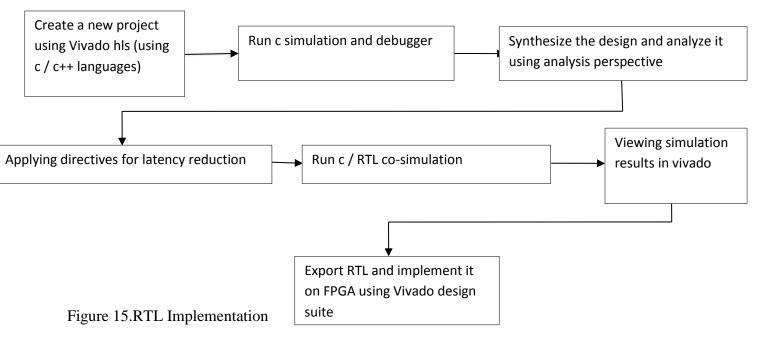

- Figure 15 RTL Implementation

- Figure 16 Directives

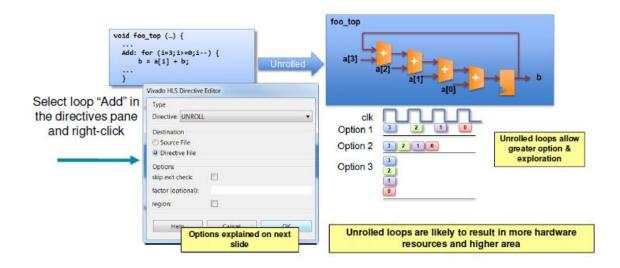

- Figure 17 Unrolled Loops with Latency

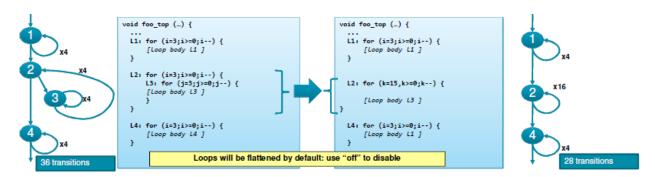

- Figure 18 Loop Flattening

- Figure 19 Perfect and Semi Perfect Loops

- Figure 20 Before Pipelining and Loop Unrolling

- Figure 21 After Pipelining

Figure 22 - After Loop Unrolling

Figure 23 - Final RTL Design

Figure 24 - timing diagram of operation

Figure 25 - GPU and CPU relationship to accelerate work

# **LIST OF TABLES**

- Table 1 Instruction executions in pipelined processor

- Table 2 Control Dependency

- Table 3 stallings in pipeline

Table 4 - Operand Forwarding

## 1.1 FPGAs – A Brief Introduction

The word digital has made a dramatic impact on our society. More significant is a continuous trend towards digital solutions in all areas – from electronic instrumentation, control, data manipulation, signals processing, telecommunications etc., to consumer electronics. Development of such solutions has been possible due to good digital system design and modeling techniques. Digital ICs have become universally standardized and have been accepted for use. Whenever a designer has to realize a digital function, he uses a standard set of ICs along with a minimal set of additional discrete circuitry. Field programmable Gate Arrays (FGPAs) are reconfigurable devices that can be electrically programmed to implement a wide variety of logic circuits. An FPGA consists of a uniform array of programmable logic structures that are interconnected by a configurable routing grid. Originally designed to serve as prototyping devices for testing and demonstrating the functionality of digital circuits, FPGAs are now an integral part of high performance systems that include digital, analog and RF components. The revolutionary success of these reconfigurable devices can be attributed to Flexibility in design implementation. The ability to instantly reprogram the FPGA with various circuits at no extra cost promotes reusability of the device, allows rapid design verification and reduces non-recurring expenditure.

- The availability of high performance FPGA based IP cores for popular applications. This allows FPGAs to function as plug and play devices in System on Chip (SoC) platforms.

- Enhanced performance due to the incorporation of specialized hardware like multipliers, high speed memories etc., into the FPGA. Additionally, the specialized blocks are also optimized for area and power which making the FPGA more competitive with custom chips.

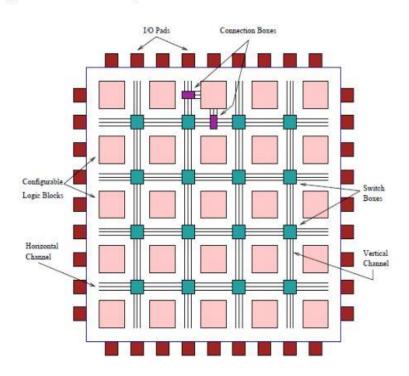

Figure 1 shows the island style of FPGA architecture.

Figure 1. FPGA Architecture [3]

As we mentioned at the beginning, FPGA is an integrated circuit. However the difference from the others is that they can be configurable as we wish. We can explain this as follows: In ordinary or standard ICs which cannot be programmable, there are fixed interconnections between the transistors. Unless they are burned or another unfortunate event does not come, they cannot be changed.

We may consider FPGAs as crude ICs of which their transistors were produced independently. Interconnections between transistors can be done according to the function we defined, then they perform the function we want. So theoretically, any operation that comes to our minds can be done by FPGAs, depending on the transistor capacity.

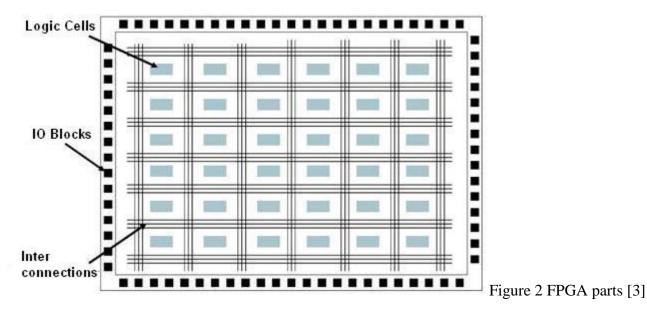

FPGA is basically consists of Logic Cells, I/O Blocks (Input/Output) and interconnections.

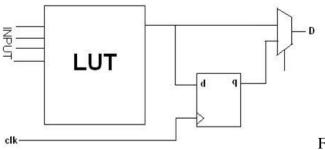

Logic Cells form the main structure of FPGAs. A Logic-Cell consists of one Lookup Table (LUT), one D-Flip Flop and one 2 to 1 Multiplexer.

Figure 3. Logic Cell [3]

LUTs are actually small memories (RAM) that fulfil logic operations... As a result of combination of thousands of Logic Cells, complex and large programs are created.

Interconnections of logic cells are provided by programmable switches and matrix formed data paths (according to the installed program FPGA).

FPGA design defines the set of connections between logic functions, by determining functions of each of the logic cells and status (open /closed) of programmable switches.

### **RAM Blocks**

In almost all of today's FPGAs, memory units called RAMs are allocated. They are used for temporary storage needs which occur during the operation of logic circuits. This RAMs can support single or multiple access. With multiple access, multiple applications can run read /write operations on the RAM. Multiple access is a good solution for transferring data between different process blocks that have different clocks. For great RAM needs, there are Block RAMs in FPGA. However there are small scattered (distributed) RAMs which are interspersed among the logic cells for small data storage needs.

One of the most important feature of FPGAs is the ability to do parallel processing. Ordinary ICs cannot do parallel processing, or they can do it limited. Whereas dozens of or perhaps thousands of parallel processing can be done simultaneously depending on the application with FPGAs. This makes FPGAs unique in applications that require parallel processing. If you use standard ICs like microprocessors, you start to get second frame after processing three operations (get, filter and send) for the first frame. If this process cannot be fast enough, you may miss the next frame. FPGAs do all these operations in parallel. That means while we processing of filtering the first frame, we might begin to take the second frame. And while us sending the first frame to the output, we begin to filter the second frame and get the third frame at the same time.

Furthermore, filtering process requires extensive multiplication process. With standard ICs, we have to do this process sequentially. Whereas this process can be done in parallel with an FPGA so it can be done very quickly.

In summary, FPGAs are hardware-programmable integrated circuits that provide us parallel processing capabilities and opportunity to change the internal structure and its function according to the desired application.

### **Intellectual Property (IP)**

Intellectual Property (IP) refers to the built-in functions that are optimised for speed and performance aspects according to a specific FPGA family. While simple functions are provided free by the manufacturer; more advanced functions are usually required to pay a certain fee.

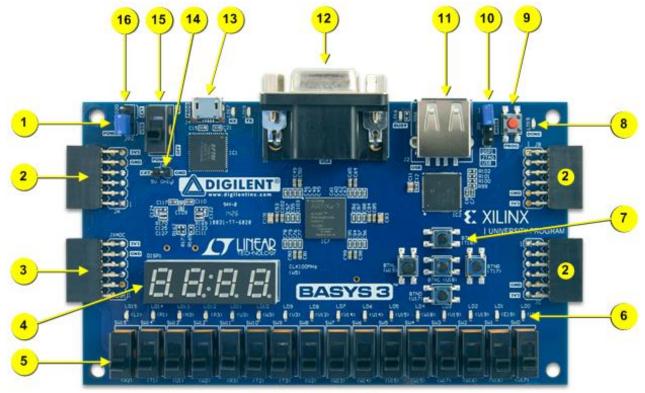

## 1.2 BASYS 3 Board

The Basys3 board is a complete, ready-to-use digital circuit development platform based on the latest Artix-7<sup>TM</sup> Field Programmable Gate Array (FPGA) from Xilinx. With its high-capacity FPGA (Xilinx part number XC7A35T-1CPG236C, low overall cost, and collection of USB, VGA, and other ports, the Basys3 can host designs ranging from introductory combinational circuits to complex sequential circuits like embedded processors and controllers. It includes enough switches, LEDs and other I/O devices to allow a large number designs to be completed without the need for any additional hardware, and enough uncommitted FPGA I/O pins to allow designs to be expanded using Digilent Pmods or other custom boards and circuits.

The Artix-7 FPGA is optimized for high performance logic, and offers more capacity, higher performance, and more resources than earlier designs. Artix-7 35T features include:

- 33,280 logic cells in 5200 slices (each slice contains four 6-input LUTs and 8 flip-flops);

- 1,800 Kbits of fast block RAM;

- Five clock management tiles, each with a phase-locked loop (PLL);

- 90 DSP slices;

- Internal clock speeds exceeding 450MHz;

- On-chip analog-to-digital converter (XADC).

The Basys3 also offers an improved collection of ports and peripherals, including:

- 16 user switches

- 16 user LEDs

- 5 user pushbuttons

- 4-digit 7-segment display

- Three Pmod ports

- Pmod for XADC signals

- 12-bit VGA output

- USB-UART Bridge

- Serial Flash

- Digilent USB-JTAG port for FPGA programming and communication

- USB HID Host for mice, keyboards and memory sticks

Figure 1, Basys3 board features

| Callout | Component Description               | Callout | Component Description           |

|---------|-------------------------------------|---------|---------------------------------|

| 1       | Powergood LED                       | 9       | FPGA configuration reset button |

| 2       | Pmod connector(s)                   | 10      | Programming mode jumper         |

| 3       | Analog signal Pmod connector (XADC) | 11      | USB host connector              |

| 4       | Four digit 7-segment display        | 12      | VGA connector                   |

| 5       | Slide switches (16)                 | 13      | Shared UART/ JTAG USB port      |

| 6       | LEDs (16)                           | 14      | External power connector        |

| 7       | Pushbuttons (5)                     | 15      | Power Switch                    |

| 8       | FPGA programming done LED           | 16      | Power Select Jumper             |

Figure 4. Basys 3 Board Features [4]

# 1.3 XILINX Vivado Design Suite

The Basys3 works with Xilinx's new high-performance Vivado ® Design Suite. Vivado includes many new tools and design flows that facilitate and enhance the latest design methods. It runs faster, allows better use of FPGA resources, and allows designers to focus their time evaluating design alternatives. The System Edition includes an on-chip logic analyzer, high-level synthesis tool, and other cutting-edge tools, and the free "Webpack" version allows Basys3 designs to be created at no additional cost.

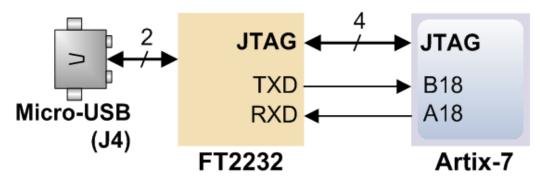

## **USB-UART Bridge (Serial Port)**

The Basys3 includes an FTDI FT2232HQ USB-UART bridge (attached to connector J4) that allows you to use PC applications to communicate with the board using standard Windows COM port commands. Free USB-COM port drivers, convert USB packets to UART/serial port data. Serial port data is exchanged with the FPGA using a two-wire serial port (TXD/RXD). After the drivers are installed, I/O commands can be used from the PC directed to the COM port to produce serial data traffic on the B18 and A18 FPGA pins.

Two on-board status LEDs provide visual feedback on traffic flowing through the port: the transmit LED (LD18) and the receive LED (LD17). Signal names that imply direction are from the point-of-view of the DTE (Data Terminal Equipment), in this case the PC.

The FT2232HQ is also used as the controller for the Digilent USB-JTAG circuitry, but the USB-UART and USB-JTAG functions behave entirely independent of one another. Programmers interested in using the UART functionality of the FT2232 within their design do not need to worry about the JTAG circuitry interfering with the UART data transfers, and vice-versa. The combination of these two features into a single device allows the Basys3 to be programmed, communicated with via UART, and powered from a computer attached with a single Micro USB cable. The connections between the FT2232HQ and the Artix-7 are shown in the below figure.

Figure 5. USB-UART Connection on FPGA [4]

# **1.4 RealTerm – Serial/TCP Terminal Software**

Realterm is an engineer's terminal program specially designed for capturing, controlling and debugging binary and other difficult data streams. It is the best tool for debugging comms.

| 🔁 RealTerm: Serial Capture Program 2.0.0.57                                                                                              |                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6173640D                                                                                                                                 |                                                                                                                                                                                                        |

| Display       Port       Capture       Pins       Send       Echo Port       I2C       I2C-2       I2CMisc       Misc         Display As | Image: Connected         Status           Connected         RXD (2)           TXD (3)         CTS (8)           DCD (1)         DSR (6)           Ring (9)         BREAK           Error         Error |

| Ctrl+Tab to step through tab sheets Char Count:0000000 CPS:0                                                                             | Port: 1 57600 8N1 None                                                                                                                                                                                 |

Figure 6. RealTerm Screen Capture [5]

**RealTerm** is a terminal software solution that enables network administrators to capture, manage or debug binary and other data streams. If you are looking for a tool that can debug dialling modems or BBS, you might need to keep on looking as RealTerm does not support such devices.

Its interface is meant to be as intuitive as possible, as each main function is detailed in its own tab

We can also modify the port, the parity and the data bits, so to come up with a configuration that best suits your needs.

One of the benefits of RealTerm is that it comes with support for hotkeys, which can help you save a lot of time when handling difficult data streams, thus allowing you to focus more on the debugging process than on operating the application.

All in all, RealTerm provides users with numerous functions that enable them to debug binary or other types of data streams, yet advanced skills are required in order to make the most of its features.

# **CHAPTER 2: HARDWARE DESIGN IMPLEMENTATION THROUGH HDLs**

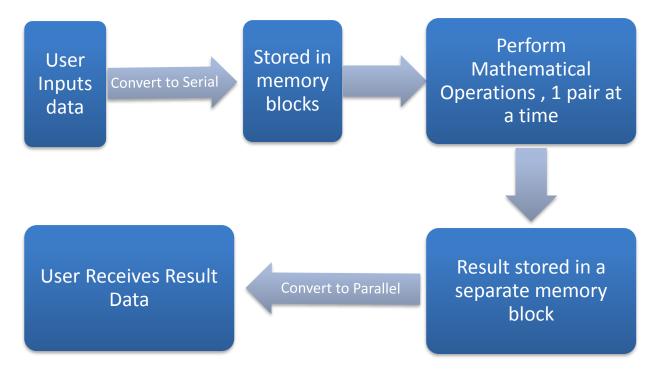

The main overview of the architecture could be explained as followed in the flow chart below:

# Figure 7. Structure Overview

Assuming that the user has decided a fixed number of input data/numbers (very large quantity of data) to be sent from a host PC and he/she wants that some mathematical operations or a set of mathematical operations to be performed on the numbers/data in a pre-defined fashion and the resulting data to be shown back to the user on the host PC.

Firstly, we need to be sure about the architecture of the process, how the data should be flowed from the PC, through the hardware FPGA, perform mathematical operations and the resultants to go through the hardware back to the host PC.

Secondly, we need to devise a way so that the hardware FPGA and the host PC could interact with each other, or communicate with each other for data flow.

The user inputs the data through the keyboard also enabling the hardware through switches and making it ready for incoming data and setting up the terminal software. Since, the main motive is to design a digital logic system, the data flowing will be binary (8-bit). We can use any of, serial or parallel communication for the data flow, but it is more feasible to use serial communication for the same because it is easier to use and understand, easier to implement on chip, low cost and placing space. Hence, Serial Communication is more preferable over the Parallel Communication Techniques.

The data is received by the receiver (first serial communication block) which then transmits the data further serially to be stored in two separate memory locations. These memory locations are designed to store large quantity of data at a place, and keep them stored until an instruction is given to remove data stored one at a time. We can set the depth of the memory according to the user preferences and needs and the fashion in which the data has to be stored (no. of bits).

Now that we have all the data stored, we can give instructions to remove data one at a time from the two memory locations and perform mathematical operations on the corresponding pairs of data/numbers and make the resultants to move further in another memory location. This final memory location would be containing all the resultant datas, which need to be sent back to the user.

The resultants move on to the transmission block (second serial communication block) one at a time, which converts these serial data back to parallel (back in the fashion in which they were input) and through some digital logic could be made available for the user to be seen back on the terminal software.

Figure 8. Data Flow in System

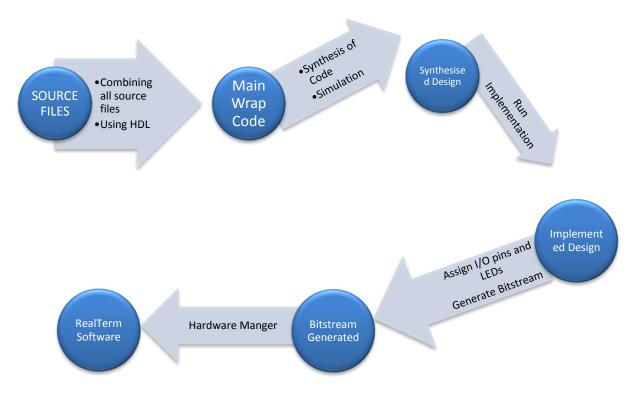

This whole process could be very well designed in XILINX Vivado Design Suite, given the knowledge of HDLs (Hardware Description Languages) like, Verilog or VHDL. These languages are specially designed for hardware programming. Since, FPGA is reprogrammable and we can possibly design the system for any type of mathematical operations using HDLs given its ease of understanding and structural flow, it gives us an advantage.

Also, the understanding of the serial communication protocol, the whole process where the conversion of parallel data from a controlling device like a CPU into serial form, its transmission in serial to the receiving block, which then converts the serial data back into parallel data for the receiving device, has been explained in detail in the later stages of the report.

We had certain source files available to us, mainly the transmission and reception files for data communication. The only problem lies in interconnecting all the modules and components through hardware programming without any errors and successful synthesis and implementation designs as well as the placing the I/O pins (switches and LEDs for the input and output ports respectively), to finally get a bitstream file for the entire project. We can easily design a VHDL/Verilog code for the same, which has been shown in the later stages of the report.

Below mentioned are the various stages that we need to go through while designing in XILINX Vivado Design Suite:

#### Figure 9. Steps using the softwares

## SERIAL COMMUNICATION PROTOCOL $\rightarrow$ UART COMMUNICATION

#### Parallel vs. Serial

Parallel interfaces transfer multiple bits at the same time. They usually require **buses** of data - transmitting across eight, sixteen, or more wires. Data is transferred in huge, crashing waves of 1's and 0's.Serial interfaces stream their data, one single bit at a time. These interfaces can operate on as little as one wire, usually never more than four. Think of the two interfaces as a stream of cars: a parallel interface would be the 8+ lane mega-highway, while a serial interface is more like a two-lane rural country road. Over a set amount of time, the mega-highway potentially gets more people to their destinations, but that rural two-laner serves its purpose and costs a fraction of the funds to build.

Parallel communication certainly has its benefits. It's fast, straightforward, and relatively easy to implement. But it requires many more input/output (I/O) lines.So, we often opt for serial communication, sacrificing potential speed for pin real estate.

*Asynchronous* serial communication means that data is transferred **without support from an external clock signal**. This transmission method is perfect for minimizing the required wires and I/O pins, but it does mean we need to put some extra effort into reliably transferring and receiving data.

# SERIAL COMMUNICATION PROTOCOL (UART COMMUNICATION)

While USB has almost completely replaced those old cables and connectors, UARTs are definitely not a thing of the past. You'll find UARTs being used in many DIY electronics projects to connect GPS modules, Bluetooth modules, and RFID card reader modules to your Raspberry Pi, Arduino, or other microcontrollers.

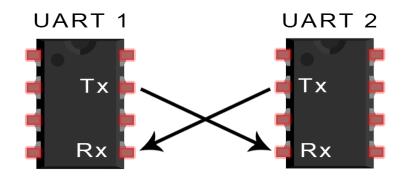

UART stands for Universal Asynchronous Receiver/Transmitter. It's not a communication protocol like SPI and I2C, but a physical circuit in a microcontroller, or a stand-alone IC. A UART's main purpose is to transmit and receive serial data.

One of the best things about UART is that it only uses two wires to transmit data between devices.

In UART communication, two UARTs communicate directly with each other. The transmitting UART converts parallel data from a controlling device like a CPU into serial form, transmits it in serial to the receiving UART, which then converts the serial data back into parallel data for the receiving device. Only two wires are needed to transmit data between two UARTs. Data flows from the Tx pin of the transmitting UART to the Rx pin of the receiving UART.

UARTs transmit data *asynchronously*, which means there is no clock signal to synchronize the output of bits from the transmitting UART to the sampling of bits by the receiving UART. Instead of a clock signal, the transmitting UART adds start and stop bits to the data packet being transferred. These bits define the beginning and end of the data packet so the receiving UART knows when to start reading the bits.

When the receiving UART detects a start bit, it starts to read the incoming bits at a specific frequency known as the *baud rate*. Baud rate is a measure of the speed of data transfer, expressed in bits per second (bps). Both UARTs must operate at about the same baud rate. The baud rate between the transmitting and receiving UARTs can only differ by about 10% before the timing of bits gets too far off.

Both UARTs must also must be configured to transmit and receive the same data packet structure.

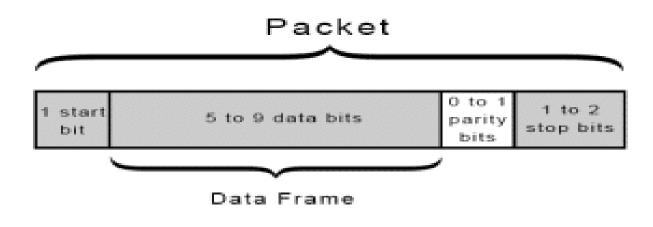

UART transmitted data is organized into *packets*. Each packet contains 1 start bit, 5 to 9 data bits (depending on the UART), an optional *parity* bit, and 1 or 2 stop bits:

Figure 10. Data Packet in UART [6]

#### **START BIT**

The UART data transmission line is normally held at a high voltage level when it's not transmitting data. To start the transfer of data, the transmitting UART pulls the transmission line from high to low for one clock cycle. When the receiving UART detects the high to low voltage transition, it begins reading the bits in the data frame at the frequency of the baud rate.

#### DATA FRAME

The data frame contains the actual data being transferred. It can be 5 bits up to 8 bits long if a parity bit is used. If no parity bit is used, the data frame can be 9 bits long. In most cases, the data is sent with the least significant bit first.

#### PARITY

Parity describes the evenness or oddness of a number. The parity bit is a way for the receiving UART to tell if any data has changed during transmission. Bits can be changed by electromagnetic radiation, mismatched baud rates, or long distance data transfers. After the receiving UART reads the data frame, it counts the number of bits with a value of 1 and checks if the total is an even or odd number. If the parity bit is a 0 (even parity), the 1 bits in the data frame should total to an even number. If the parity bit is a 1 (odd parity), the 1 bits in the data frame should total to an odd number. When the parity bit matches the data, the UART knows that the transmission was free of errors. But if the parity bit is a 0, and the total is odd; or the parity bit is a 1, and the total is even, the UART knows that bits in the data frame have changed.

## **STOP BITS**

To signal the end of the data packet, the sending UART drives the data transmission line from a low voltage to a high voltage for at least two bit durations.

## ADVANTAGES AND DISADVANTAGES OF UARTS

No communication protocol is perfect, but UARTs are pretty good at what they do. Here are some pros and cons to help you decide whether or not they fit the needs of your project:

## ADVANTAGES

- Only uses two wires

- No clock signal is necessary

- Has a parity bit to allow for error checking

- The structure of the data packet can be changed as long as both sides are set up for it

- Well documented and widely used method

## DISADVANTAGES

- The size of the data frame is limited to a maximum of 9 bits

- Doesn't support multiple slave or multiple master systems

- The baud rates of each UART must be within 10% of each other

## **WORKING AND FINAL DESIGN**

#### COMPONENTS INVOLVED IN THE DESIGN

- 1. First In First Out (FIFO) Memory Block

- 2. UART Serial Communication Blocks Receiver and Transmission Block

- 3. Clock Divider Module

- 4. Selection Module

- 5. Adder Block

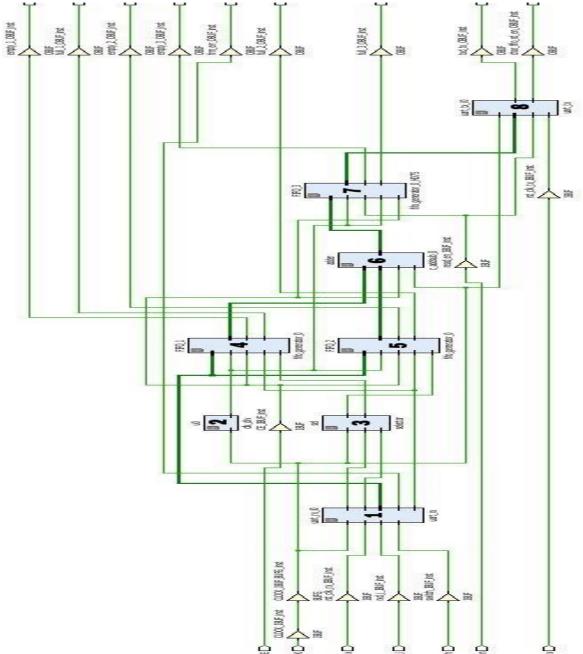

Figure 11. Final Synthesized Design of System

## ► FIRST IN FIRST OUT (FIFO) MEMORY BLOCK

As the name suggests, FIFOs are a special kind of memory blocks for any digital logic system, whatever be the depth of this memory block (the no. of data entries that it can store), whichever number was the first to be entered will be the first one to come out of the block when given certain instruction.

The FIFO Generator core is a fully verified first-in first-out memory queue for use in any application requiring ordered storage and retrieval, enabling high-performance and area-optimized designs. The core provides an optimized solution for all FIFO configurations and delivers maximum performance (up to 500 MHz) while using minimum resources. This core can be customized using the Vivado IP customizers in the IP catalog as a complete solution with control logic already implemented, including management of the read and write pointers and the generation of status flags.

For this project, we have used FIFO as an in-built IP (Intellectual Property) from the IP Catalog available in the software, which is customizable according to user needs.

Here, the FIFO memory block is being used to store large data in groups, for example, a FIFO with a write depth of 16 and write width of 8, would be able to store 16 eight- bit numbers in it. This can be changed in the customization settings while designing the IP.

Also, another variation that has been used is the Independent Clocks Block RAM (which enables us to choose different clocks for both read and write operations simultaneously). This is necessary to improve the performance of the system on a whole. We cannot have slower clocks for writing the data into the FIFO if the depth is very much.

The key components/ports of the FIFO memory block being:

- read clock clock followed when reading data from the FIFO

- write clock clock followed when writing data into the FIFO

- read enable tells the FIFO when to read

- write enable tells the FIFO when to write

- data input port data input through this port (our case 8-bit binary numbers)

- data output port data output through this port (our case 8-bit binary numbers)

- full flag indicates when the FIFO memory is complete and cannot take any more entries

- empty flag indicates when the FIFO memory is completely empty

#### > UART SERIAL COMMUNICATION BLOCKS

- UART TRANSMISSION BLOCK

- Metastability Hardener

- Baud Generator

- Control Module

## • UART RECIVER MODULE

- Baud Generator

- Control Module

<u>Metastability Hardener</u> -- This is a basic meta-stability hardener; it double synchronizes an asynchronous signal onto a new clock domain.

Metastability is a phenomenon that can cause system failure in digital devices, including FPGAs, when a signal is transferred between circuitry in unrelated or asynchronous clock domains. If the data output signal resolves to a valid state before the next register captures the data, then the metastable signal does not negatively impact the system operation. But if the metastable signal does not resolve to a low or high state before it reaches the next design register, it can cause the system to fail. Continuing the ball and hill analogy, failure can occur when the time it takes for the ball to reach the bottom of the hill (a stable logic value 0 or 1) exceeds the allotted time, which is the register's tCO plus any timing slack in the path from the register. When a metastable signal does not resolve in the allotted time, a logic failure can result if the destination logic observes inconsistent logic states, that is, different destination registers capture different values for the metastable signal. [Refer appendix (1)]

**Baud Generator** -- Generates a 16x Baud enable. This signal is generated 16 times per bit at the correct baud rate as determined by the parameters for the system clock frequency and the Baud rate. This is essential for the sampling of bits incoming into both UART blocks for communication.

The Baud Generator generates a signal which ticks 16 times per bit at the baud rate of 9600 bps. This signal is essential for the sampling of data bits and to decide whether the data flowing is valid or not. [Refer appendix (2)]

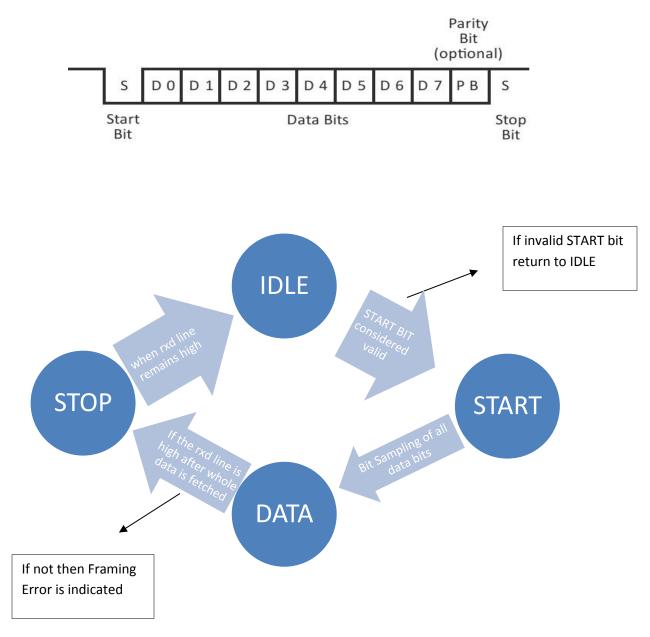

**CONTROL MODULE for Input** -- Implements the state machines for doing RS232 reception. Based on the detection of the falling edge of the synchronized rxd input, this module waits 1/2 of a bit period (8 periods of baud\_x16\_en) to find the middle of the start bit, and resamples it. If rxd is still low it accepts it as a valid START bit, and captures the rest of the character, otherwise it rejects the start bit and returns to idle. After detecting the START bit, it advances 1 full bit period at a time (16 periods of baud\_x16\_en) to end up in the middle of the 8 data bits, where it samples the 8 data bits. After the last bit is sampled (the MSbit, since the Lsbit is sent first), it waits one additional bit period to check for the STOP bit. If the rxd line is not high (the value of a STOP bit), a framing error is signaled. Regardless of the value of the rxd, though, the module returns to the IDLE state and immediately begins looking for the start of the next character. The total cycle time through the state machine is 9 1/2 bit periods (not 10) – this allows for a mismatch between the transmit and receive clock rates by as much as 5%.

Figure 12. State Machine Representation of Control Module

**CONTROL MODULE for Output--** Implements the state machines for doing RS232 transmission. Whenever a character is ready for transmission (as indicated by the empty signal from the character FIFO), this module will transmit the character. The basis of this design is a simple state machine. When in IDLE, it waits for the character FIFO to indicate that a character is available, at which time, it immediately starts transmission. It spends 16 baud\_x16\_en periods in the START state, transmitting the START condition (1'b0), then transitions to the DATA state, where it sends the 8 data bits (Lsbit first), each lasting 16 baud\_x16\_en periods of the STOP state for 16 periods, where it transmits the STOP value (1'b1). On the last baud\_x16\_en period of the last data bit (in the DATA state), it issues the POP signal to the character FIFO. Since the SM is only enabled when baud\_x16\_en is asserted, the resulting pop signal must then be ANDed with baud\_x16\_en to ensure that only one character FIFO is inspected; if asserted, the STOP state, the empty indication from the character FIFO is inspected; if asserted, the SM returns to the IDLE state, otherwise it transitions directly to the START state to start the transmission of the next character. There are two internal counters – one which counts off the 16 pulses of baud\_x16\_en, and a second which counts the 8 bits of data. The generation of the output (txd\_tx) follows one complete baud\_x16\_en period after the state machine and other internal counters.

// Assert the rd\_en to the FIFO for only ONE clock period

#### assign char\_fifo\_rd\_en = char\_fifo\_pop && baud\_x16\_en;

It is a similar finite state machine as previous one, the only addition is the logic through which every character is popped out to be seen on the terminal screen.

#### > CLOCK DIVIDER MODULE

This module is essential because the read operations for the FIFO require a slower clock and since, on the Basys 3 Board there is a single clock of 100 MHz available to us, we need to reduce the clock frequency to much lower values for successful read operations. For our case, we have reduced the available clock frequency of 100MHz to 1Hz. [Refer appendix (3)]

#### SELECTION MODULE

This module is necessary because it enables us to decide about the latest input data entry, that, where among the 2 FIFOs it should be stored, because the mathematical operations have to be performed between a pair of data entries. On the FPGA, the input is given through switch, if low, then FIFO1, if high, then FIFO2.

[Refer appendix (4)]

#### > INVERSION MODULE

This module is necessary because through this we can decide when the transmission of the result data starts. On the FPGA, it is incorporated through a switch. [Refer appendix (5)]

## > ADDER BLOCK

This is the module where the main mathematical operation is taking place – the addition of 8-bit binary numbers. It has the 2 inputs connected to the data output ports of both FIFOs and an enable port which decides when the operation takes place. It passes on the 8-bit binary sum ahead to the result storing FIFO, after performing each successive operation.

This block is being implemented as an in-built Intellectual Property (IP) in the XILINX Vivado software. It is always customizable according to user needs.

Combining all these components we obtained the final design of the complete architecture of the system to Perform Mathematical Operations with Interaction between the Hardware FPGA and host PC. Next, we will look at the main design wrapper (the main code which connects all these modules together).

#### MAIN PROGRAM CODE AND WORKING

Given below is the main structural code for the whole system which involves all of the above mentioned modules to obtain the final design of the system.

#### `timescale 1ns / 1ps

#### module main(

| input  | CLOCK,                                                          |  |  |  |  |

|--------|-----------------------------------------------------------------|--|--|--|--|

| input  | <b>rst_clk_rx,</b> // Active HIGH reset - synchronous to clk_rx |  |  |  |  |

| input  | rxd_i, // RS232 RXD pin - Directly from pad                     |  |  |  |  |

| output | frm_err, // The STOP bit was not detected                       |  |  |  |  |

| output | full_1,                                                         |  |  |  |  |

| output | empty_1,                                                        |  |  |  |  |

| output | full_2,                                                         |  |  |  |  |

| output | empty_2,                                                        |  |  |  |  |

| output | full_3,                                                         |  |  |  |  |

| output | empty_3,                                                        |  |  |  |  |

| input  | <b>rst_clk_tx,</b> // Active HIGH reset - synchronous to clk_tx |  |  |  |  |

| output | char_fifo_rd_en, // Pop signal to the char FIFO                 |  |  |  |  |

| output | txd_tx, // The transmit serial signal                           |  |  |  |  |

| input  | switch,                                                         |  |  |  |  |

| input  | CE,                                                             |  |  |  |  |

| input  | read_en                                                         |  |  |  |  |

| );     |                                                                 |  |  |  |  |

parameter BAUD\_RATE = 9600; // Baud rate

parameter CLOCK\_RATE = 100000000;

parameter sys\_clk = 100000000; // 100 MHz system clock

parameter clk\_out = 1; // 1 Hz clock output

```

// Wire Declarations

wire c;

wire write_clk;

wire w1;

wire w2;

wire write_en;

wire [7:0] data_out1;

wire [7:0] data_out2;

wire [7:0] sum;

wire [7:0] data_in;

wire [7:0] data_out3;

wire fifo3_empty;

wire trans_start;

// Code

```

inv i0(.a(read\_en) , .b(trans\_start));

clk\_div #( .sys\_clk(100000000) , .clk\_out(1) , .max(50000000)) u0 (.Clk\_in(CLOCK) , .Clk\_out(c));

```

uart_rx uart_rx_i0(

.clk_rx (CLOCK),

.rst_clk_rx (rst_clk_rx),

.rxd_i (rxd_i),

.rxd_clk_rx (write_clk),

.rx_data (data_in),

.rx_data_rdy (write_en),

.frm_err (frm_err)

```

```

selector sel(

.switch(switch),

.data(write_en),

.Clock(CLOCK),

.Out1(w2),

.Out2(w1)

);

```

```

fifo_generator_0 FIFO_1 (

```

```

.wr_clk(write_clk), // input wire wr_clk

.rd_clk(c), // input wire rd_clk

.din(data_in), // input wire [7 : 0] din

.wr_en(w2), // input wire wr_en

.rd_en(CE), // input wire rd_en

.dout(data_out1), // output wire [7 : 0] dout

.full(full_1), // output wire full

.empty(empty_1) // output wire empty

);

```

```

fifo_generator_0 FIFO_2 (

```

```

.wr_clk(write_clk), // input wire wr_clk

.rd_clk(c), // input wire rd_clk

.din(data_in), // input wire [7 : 0] din

.wr_en(w1), // input wire wr_en

.rd_en(CE), // input wire rd_en

.dout(data_out2), // output wire [7 : 0] dout

.full(full_2), // output wire full

.empty(empty_2) // output wire empty

);

```

```

c_addsub_0 adder (

```

```

.A(data_out1), // input wire [7 : 0] A

.B(data_out2), // input wire [7 : 0] B

.CLK(CLOCK), // input wire CLK

```

.CE(CE), // input wire CE .S(sum) // output wire [7 : 0] S

);

## fifo\_generator\_0 FIFO\_3 (

.wr\_clk(c), // input wire wr\_clk

.rd\_clk(c), // input wire rd\_clk

.din(sum), // input wire [7 : 0] din

.wr\_en(CE), // input wire wr\_en

.rd\_en(read\_en), // input wire rd\_en

.dout(data\_out3), // output wire [7 : 0] dout

.full(full\_3), // output wire full

.empty(empty\_3) // output wire empty

);

```

uart_tx uart_tx_i0(

.clk_tx(CLOCK),

.rst_clk_tx(rst_clk_tx),

//.baud_x16_en(baud_x16_en),

.char_fifo_empty(trans_start),

.char_fifo_dout(data_out3),

.char_fifo_rd_en(char_fifo_rd_en),

.txd_tx(txd_tx)

);

```

#### endmodule

We have taken a simple exam of 8-bit binary addition mathematical operation, even more complex mathematical operations can be achieved, and we just have to design a module in HDL for that specific operation or a set of operations.

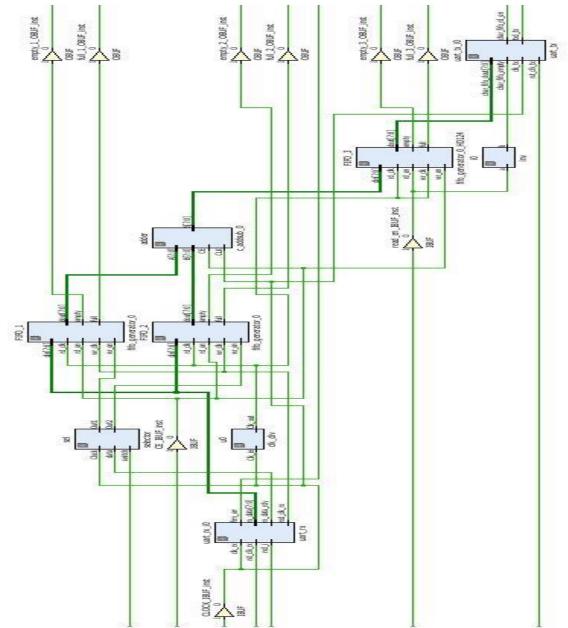

Shown next is the elaborated RTL level design of the system after executing the main wrapper (main code) Figure 13. RTL level design of system

The user inputs the data through the keyboard also enabling the hardware through switches and making it ready for incoming data and setting up the terminal software. It flows through the UART Block 1 as it receives parallel data and changes it to serial fashion. The input can now go towards any of the 2 FIFOs storing input datas, the path would be decided by the state of the selection module. The process continues until both the FIFOs are full.

We have a common enable signals for the first 2 FIFOs and the adder enable. All of them go high together.

Now that we have all the data stored, we can give read enable signals to remove data one at a time from both the memory locations and perform mathematical operations on the corresponding pairs of data/numbers.

First the operation between a pair of numbers takes place and the result goes on to the result storing FIFO. Only after that the next operation on the next pair of numbers takes place. This process goes on until both the input FIFOs get empty, and the result storing FIFO gets full.

This final memory location would be containing all the resultant datas, which need to be sent back to the user. The read enable ensures that the data moves out one by one, through the UART Block 2 for transmission, the serial data now is converted back to parallel fashion and popped one character at a time for the result to be shown on the terminal software.

After synthesis of the main Verilog code, we have to designate the I/O ports with appropriate switches and LEDs, a screen capture of the same is also shown below, which is obtained by using the I/O Planning option in the software.

| Flow Navigator ? «                      | Synt            | thesized Design - synth 1   xc7a35tcpg2 | 36.1 (active)   |                  |                      |               |             |   |       |        |                              |   |          | 7)      |

|-----------------------------------------|-----------------|-----------------------------------------|-----------------|------------------|----------------------|---------------|-------------|---|-------|--------|------------------------------|---|----------|---------|

| Q. 🖾 🏨                                  |                 |                                         | and a formately |                  |                      |               |             |   |       |        |                              |   |          |         |

| Report Noise                            | Contract States | Ports                                   |                 |                  |                      |               |             |   |       |        |                              |   | ? - 6    |         |

|                                         |                 | Name                                    | Direction       | Board Part Pin   | Board Part Interface | Neg Diff Pair | Package Pin |   | Fixed | Bank   | I/O Std                      |   | Vcco Vre | f Drive |

| Report Utilization                      |                 | W All ports (16)                        |                 |                  |                      |               |             |   |       |        |                              |   |          | 1       |

| Report Power                            | 1               | 🕀 🙀 dk_intf_21064 (1)                   | IN              |                  |                      |               |             |   |       |        | 34 LVCMOS33*                 | • | 3.300    |         |

| Schematic                               | B               | Scalar ports (1)                        |                 |                  |                      |               |             |   | _     |        |                              |   |          |         |

|                                         |                 | -B CTOCK                                | IN              |                  |                      |               | W5          | * |       |        | 34 LVCMOS33*                 |   | 3.300    |         |

| Implementation                          |                 | E G FIFO_READ_4750 (2)                  | (Multiple)      |                  |                      |               |             |   |       | (Multi | ple) LVCMOS33*               | * | 3.300    | (Mult   |

|                                         | 22              | 🖻 🥑 Scalar ports (2)                    | OUT             |                  |                      |               | N3          |   | -     |        |                              |   |          |         |

| Implementation Settings                 |                 |                                         | IN              |                  |                      |               | UI          |   |       |        | 35 LVCMOS33*<br>34 LVCMOS33* |   | 3.300    | 12      |

| Run Implementation                      |                 | FIFO_READ_53839 (1)                     | OUT             |                  |                      |               | 01          |   | NN    |        | 34 LVCMOS33*<br>35 LVCMOS33* |   | 3.300    | 12      |

| 4 🔄 Implemented Design                  | V               | G (2) Scalar ports (1)                  | 001             |                  |                      |               |             |   |       |        | 35 LVCMU533*                 |   | 3.300    | 12      |

| Sconstraints Wizard                     |                 | empty_2                                 | OUT             |                  |                      |               | P1          |   | 12    |        | 35 LVCMOS33*                 |   | 3.300    | 12      |

|                                         |                 | E G FIFO_READ_54031 (1)                 | OUT             |                  |                      |               |             |   | NN    |        | 35 LVCMOS33*                 |   | 3.300    | 12      |

| 🚵 Edit Timing Constrain                 |                 | Scalar ports (1)                        |                 |                  |                      |               |             |   | 2     |        |                              |   | 01000    |         |

| Report Timing Summa                     |                 | g empty_1                               | OUT             |                  |                      |               | L1          |   |       |        | 35 LVCMOS33*                 | * | 3.300    | 12      |

| Report Clock Networ                     |                 | FIFO_WRITE_4750 (1)                     | OUT             |                  |                      |               |             |   | Ø     |        | 34 LVCMOS33*                 |   | 3.300    | 12      |

|                                         |                 | G Scalar ports (1)                      |                 |                  |                      |               |             |   | -     |        |                              |   |          |         |

| Report Clock Interac                    |                 | ful_3                                   | OUT             |                  |                      |               | W3          |   |       |        | 34 LVCMOS33*                 | - | 3.300    | 12      |

| Report Methodology                      |                 | G FIFO_WRITE_53839 (1)                  | OUT             |                  |                      |               |             |   |       |        | 34 LVCMOS33*                 |   | 3.300    | 12      |

| Report DRC                              |                 | G Scalar ports (1)                      |                 |                  |                      |               |             |   |       |        |                              |   |          |         |

|                                         |                 |                                         | OUT             |                  |                      |               | U3          |   |       |        | 34 LVCMOS33*                 |   | 3.300    | 12      |

| Report Noise                            |                 | FIFO_WRITE_54031 (1)                    | OUT             |                  |                      |               |             |   |       |        | 35 LVCMOS33*                 | • | 3.300    | 12      |

| Report Utilization                      |                 | G Scalar ports (1)                      |                 |                  |                      |               |             |   |       |        |                              |   |          |         |

| Report Power                            |                 | ful_1                                   | OUT             |                  |                      |               | P3          | • |       |        | 35 LVCMOS33*                 | * | 3.300    | 12      |

| -                                       |                 | E Scalar ports (8)                      |                 |                  |                      |               |             |   | -     |        |                              |   |          |         |

| Program and Debug                       |                 | - ₽ CE                                  | IN              |                  |                      |               | V17         | • |       |        | 14 LVCMOS33*                 |   | 3.300    | -       |

| Bitstream Settings                      |                 |                                         | OUT             |                  |                      |               | U16<br>E19  |   |       |        | 14 LVCMOS33*                 |   | 3.300    | 12      |

| 2 · · · · · · · · · · · · · · · · · · · |                 | - d frm_err                             | IN              |                  |                      |               | V16         |   |       |        | 14 LVCMOS33*<br>14 LVCMOS33* |   | 3.300    | 12      |

| Cenerate Bitstream                      |                 | - Brst_dk_rx<br>- Brst_dk_tx            | IN              |                  |                      |               | W16         |   |       |        | 14 LVCM0533*<br>14 LVCM0533* |   | 3.300    |         |

| 4 📕 Hardware Manager                    |                 | - Rend i                                | IN              |                  |                      |               | B18         |   | -     |        | 16 LVCM0533*                 |   | 3.300    | _       |

| Dpen Target                             |                 | - R switch                              | IN              |                  |                      |               | W17         |   |       |        | 14 LVCM0533*                 |   | 3.300    |         |

| -                                       |                 | Ch hand has                             | OUT.            |                  |                      |               | A 10        | - | E     | -      | ***********                  |   | 2 200    |         |

| Program Device                          | - Ingenerate    | <                                       |                 |                  |                      |               |             |   |       |        |                              |   |          | >       |

| 🕸 Add Configuration M 🗸                 | 1               | 📑 Tcl Console 🛛 💬 Messages 🔄 Log        | Reports Desi    | gn Runs 🛛 🔎 Padi | age Pins D I/O Por   | ts 👌 Timing   |             |   |       |        |                              |   |          |         |

Figure 14. I/O Planning

The Baud Rate is set at 9600 bps, both UARTs must operate at the same Baud Rate for the communication to be successful.

| 🖣 📲 RealTerm: Serial Captur                 | e Program 2.0.0.70                              |                              | -                  |                                     |

|---------------------------------------------|-------------------------------------------------|------------------------------|--------------------|-------------------------------------|

| (Reep)                                      |                                                 |                              |                    |                                     |

| ]                                           |                                                 |                              |                    |                                     |

| (2)(2)                                      |                                                 |                              |                    |                                     |

| 2                                           |                                                 |                              |                    |                                     |

| 2005<br>2005                                |                                                 |                              |                    |                                     |

|                                             |                                                 |                              |                    |                                     |

| Ciac<br>Ciac                                |                                                 |                              |                    |                                     |

|                                             | ns Send Echo Port I2C   12C-2   12CMisc   Misc  |                              | <u>\n</u> Clear Fr | reeze ?                             |

| Baud SEO0 - Port 4                          | <u>Open</u> Spy     Change                      | <b>v</b>                     |                    | Status<br>Connected                 |

| Parity Data Bits S<br>• None • 8 10 0       | top Bits Software Flow Control                  |                              |                    | _ RXD (2)<br>_ TXD (3)<br>_ CTS (8) |

| C Odd C 7 bits<br>C Even<br>C Mark C 6 bits | ardware Flow Control None C RTS/CTS             |                              |                    | DCD (1)                             |

| Blase C Space C 5 bits (                    | C DTR/DSR C RS485-tts C Raw                     |                              |                    | Ring (9)<br>BREAK                   |

|                                             | window before you can type any cha Char Count:0 | CPS:0 Port: 4 57600 8N1 None |                    | Error                               |

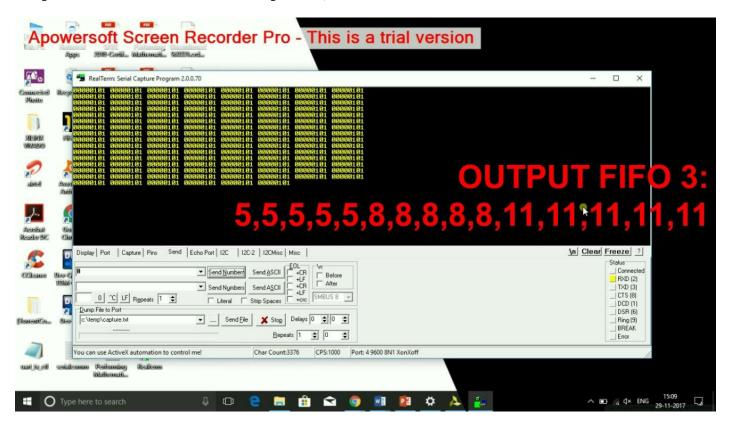

User Input in FIFO 1 (write depth-16, write width – 8bits) - 1,1,1,1,1,2,2,2,2,2,3,3,3,3,3

**User Input in FIFO 2 (write depth-16, write width – 8bits)** – 4,4,4,4,6,6,6,6,6,8,8,8,8,8

| 2 <sub>0</sub> | 9          | RealTerm: Serial Capture Program 2.0.0.70                                                                  | - 0                  | ×                  |              |

|----------------|------------|------------------------------------------------------------------------------------------------------------|----------------------|--------------------|--------------|

| aitai<br>Ro    | Beege      |                                                                                                            |                      |                    |              |

|                |            |                                                                                                            |                      |                    |              |

| 1              |            |                                                                                                            |                      |                    |              |

| 100            | (FIER      |                                                                                                            |                      |                    |              |

| 90             |            | INPU                                                                                                       |                      |                    |              |

| ,              | 2          |                                                                                                            |                      |                    |              |

| 41             | AVAT       |                                                                                                            |                      |                    |              |

|                | 2100       | 111112222                                                                                                  | 231                  |                    |              |

|                |            | 1,1,1,1,1,2,2,2,2,                                                                                         | 2,0,0                | <b>,</b> 4         | <b>,  ,</b>  |

| izaji          | E Ciak     |                                                                                                            | 1.00                 |                    |              |

| URC .          | Cite       |                                                                                                            |                      |                    |              |

|                |            | isplay   Port   Capture   Pins Send   Echo Port   12C   12C-2   12CMisc   Misc                             | <u>In</u> Clear Free | ze ?               |              |

| •              |            | Send Numbers Send ASCII - CR 4,4,4,4,6,6,6,6,6,6                                                           | 6 8 3                | onecte             |              |

| INCO 1         | Utilitie T | Send Numbers Send ASCII - CR Alter , +, +, +, +, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,                    | 0,0,0                | XD (S)             | <b>, O</b> , |

|                | Πİ         | 0 °C LF Repeats 1 C Literal Ship Spaces +cr SMBUS 8                                                        |                      | CTS (8)            |              |

|                |            | Dump File to Port                                                                                          |                      | OCD (1)<br>OSR (6) |              |

| iC.e.          | Bleef      | c:\temp\capture.bt 🔹 Send File 🗶 Stop Delays 0 호 0 호                                                       |                      | Ring (9)<br>BREAK  |              |

|                | _          | <u>R</u> epeats 1 € 0 €                                                                                    |                      | Inor               |              |

| 7              | C          | n be chars, python backslash sequences, hex or decimal bytes v Char Count:0 CPS:0 Port: 4 9600 8N1 XonXoff |                      |                    |              |

**Output to User from FIFO3 (write depth -16 , write width- bits)** – 5,5,5,5,5,8,8,8,8,8,11,11,11,11,11

| Арс                   | owersoft Screen Recorder Pro - This is a trial version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|                       | 😋 🚡 RealTerm: Serial Capture Program 2.0.0.70 — 🗆 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |

| Connected)<br>Pieto   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |

| SHEERS<br>WALLES      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |

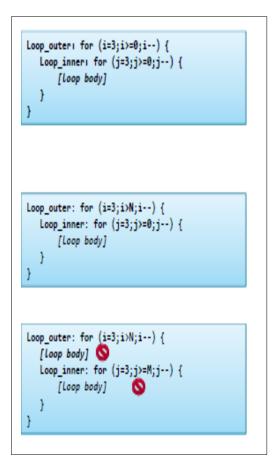

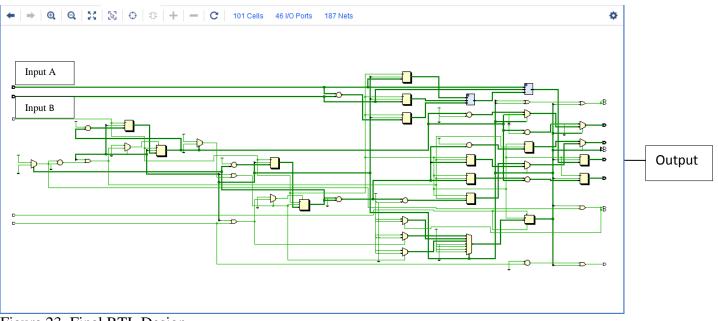

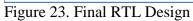

| 2                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.               |