# Hardware-Software Co-Design for Edge AI Accelerator: A Hardware-Centric Perspective

#### A Thesis

Submitted in partial fulfillment of the requirements for the award of the degree

of

Master of Technology (VLSI Design & Nanoelectronics)

by

OMKAR RAJESH KOKANE

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE MAY 2025

## INDIAN INSTITUTE OF TECHNOLOGY INDORE

#### CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the thesis entitled Hardware-Software Co-Design for Edge AI Accelerator: A Hardware-Centric Perspective in the partial fulfillment of the requirements for the award of the degree of Master of Technology in VLSI Design & Nanoelectronics and submitted in the Department of Electrical Engineering, Indian Institute of Technology Indore, is an authentic record of my own work carried out during the time period from July 2023 to May 2025 under the supervision of Dr. Santosh Kumar Vishvakarma, Professor, Indian Institute of Technology Indore, Indore, India.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other institute.

Signature of the Student

(Omkar Rajesh Kokane)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

Signature of the Supervisor of M.Tech. Thesis with Date

(Prof. Santosh Kumar Vishvakarma)

Omkar Rajesh Kokane has successfully given his M.Tech. Oral Examination held on 05/05/2025

Signature of Supervisor of M.Tech. Thesis

Date: 19/05/2025

Saptarshi Ghosh

Signature of Convener, DPGC

${\rm Date:} \quad 19\text{-}05\text{-}2025$

#### ACKNOWLEDGEMENTS

I am immensely grateful to my M.Tech. thesis supervisor and mentor, Prof. Santosh Kumar Vishvakarma, for consistently encouraging and supporting me in my research. His unwavering belief in my abilities and his invaluable guidance have served as constant motivation, pushing me to exceed my own limits. I would also like to extend my sincere appreciation to all of my thesis evaluation committee members. Their impartial evaluations and thought-provoking questions have contributed significantly to expanding my research perspective.

I am immensely thankful to my family for their unyielding support throughout my master's studies. Their confidence in me and their love, sacrifices, and constant encouragement have been instrumental in my academic success. I will forever be grateful for their guidance, and their faith in me will continue to propel me towards greater accomplishments.

My friends has played a major role in supporting my research work throughout the course of my master's . They have always boosted my confidence and always motivated me to push my limits. I will always be grateful to them for all their guidance, love and sacrifices. Their faith in me has brought me this far, and it will drive me further, as well, to achieve greater things in future.

I deeply appreciate the Nanoscale Devices, VLSI Circuit and System (NSDCS) Lab research group, especially Dr. Gopal Raut and Mr. Mukul Lokhande and Prof. Adam Teman form Bar-Ilan University in Ramat Gan, Israel and a co-Director of the Emerging Nanoscaled Circuits and Systems (EnICS) Labs and Dr. Ratko Pilipović from University in Ljubljana Faculty of Computer and Information Science for their unwavering support and guidance in both my technical and personal development. I also appreciate the camaraderie and encouragement of my friends Mr. Sapan Kushwah, Mr. Athava Limaye, Mr. Ashreta Sahay, Mr. Abu Said Parvej Alam, Mr. Amit Singh and labmates, Mrs. Neha Maheshwari, Mr. Sonu Kumar, Mr. Shashank Singh Rawat, Mr. Vikash Vishwakarma, Mr. Ankit Tenwar, Mr. Vijay Sharma, Mrs Akansha Jain, Mr. Anoop R., Mr. Mohamad Faisal and my M. Tech. seniors Ms.

Komal Gupta, and Mr. Sagar Patel, Mr. Radheshyam Sharma whose friendship made my time at the institute truly remarkable...

$Omkar\ Rajesh\ Kokane$

$This \ The sis \ is \ Dedicated \\ to$

Science, Family, Friends and the Almighty God

#### ABSTRACT

This thesis presents a comprehensive co-design of hardware-efficient components tailored for edge-AI accelerator, focusing on three key innovations: the Plus-One Adder (P1A), the Logarithmic Posit-enabled Reconfigurable Engine (LPRE), and the CORDIC-based Reconfigurable Processing Engine (RPE).

First, we propose a novel Plus-One Adder (P1A), designed as an incremental unit within a ripple-carry adder (RCA) chain. It integrates a full adder with an excess-1 generator alongside inputs A, B, and Cin. The output is approximated to 2-bit values to reduce hardware complexity, significantly improving resource efficiency. The P1A is evaluated in the context of Two's complement subtraction and rounding-to-even operations, with a detailed analysis of error distance versus area and power metrics using CMOS 28nm technology. Extending this, we introduce the Hybrid Overestimating Approximate Adder (HOAA(n, m)), which enables dynamic reconfigurability between a (n-m)-bit RCA and an m-bit P1A block, based on workload requirements. This architecture achieves up to 1.33× area reduction and 0.79× power savings, making it a promising component for performance-optimized processing engines.

To address the limitations of edge-AI deployments in bandwidth-constrained environments, we propose LPRE, a Logarithmic-Posit-enabled Reconfigurable Engine that delivers high throughput with minimal resource usage. Leveraging time-multiplexed, single-layer reconfigurable hardware, LPRE supports efficient execution of multi-layer perceptrons and convolutional neural networks. Experimental results on LeNet-5 using the MNIST dataset show that LPRE achieves 4× throughput enhancement at 8-bit precision, with negligible accuracy degradation compared to the FP32 baseline. Moreover, it reduces resource utilization by up to 80% versus fixed-point designs and 50% compared to state-of-the-art accelerators, demonstrating its suitability for low-power, real-time applications such as number plate recognition and scalable IoT edge inference.

Finally, we introduce a CORDIC-based Reconfigurable Processing Engine (RPE)

that supports both linear MAC computations and nonlinear iterative activation functions such as tanh, sigmoid, and softmax. The architecture is implemented as a pipelined, systolic array-based engine, with runtime reconfigurability and precision scaling. The design incorporates five linear CORDIC stages for MAC and additional stages for activation, enabling efficient reuse of hardware. Through pruning strategies (up to 40%), the RPE achieves up to 4.64× throughput gain, with area and power reductions of 4.06× and 5.02×, respectively, on CMOS 28nm, and 2.5× resource and 3× power savings on FPGA. The SYCore (Systolic CORDIC Engine for Reconfigurability and Enhanced throughput) employs an output-stationary dataflow and is managed by a CAESAR control engine, enabling execution of diverse AI workloads including Transformers, RNNs/LSTMs, and DNNs. Use cases span image detection, LLMs, and speech recognition, validating the scalability and energy efficiency of the proposed edge-AI accelerator design.

Together, these co-designed architectural elements form a robust foundation for next-generation edge-AI accelerators, addressing key challenges in area, power, throughput, and configurability without compromising accuracy—making them well-suited for deployment in mobile, IoT, and embedded AI systems.

## Contents

|   | Abs  | Abstract |                                                    |      |  |  |  |

|---|------|----------|----------------------------------------------------|------|--|--|--|

|   | List | of Fig   | gures                                              | iv   |  |  |  |

|   | List | of Ta    | bles                                               | vii  |  |  |  |

|   | List | of Ab    | breviations                                        | vii  |  |  |  |

| 1 | Intr | roducti  | ion                                                | 1    |  |  |  |

|   | 1.1  | Introd   | luction                                            | . 2  |  |  |  |

|   |      | 1.1.1    | Background & Motivation                            | . 3  |  |  |  |

|   | 1.2  | Resear   | rch Objectives                                     | . 9  |  |  |  |

|   | 1.3  | Organ    | nization of Thesis                                 | . 10 |  |  |  |

| 2 | НО   | AA: H    | ybrid Overestimating Approximate Adder for Enhance | d    |  |  |  |

|   | Per  | formaı   | nce Processing Engine                              | 12   |  |  |  |

|   | 2.1  | Propo    | sed Architecture                                   | . 16 |  |  |  |

|   |      | 2.1.1    | Proposed P1A Design                                | . 16 |  |  |  |

|   |      | 2.1.2    | Proposed HOAA Design                               | . 17 |  |  |  |

|   | 2.2  | Metho    | odology & Results Discussion                       | . 18 |  |  |  |

|   |      | 2.2.1    | Case-I: Subtraction                                | . 20 |  |  |  |

|   |      | 2.2.2    | Case-II: Rounding-to-even                          | . 21 |  |  |  |

|   |      | 2.2.3    | Case-III: Configurable activation function         | . 22 |  |  |  |

| 3 | LPRE:Logarithmic Posit-enabled Reconfigurable edge-AI Engine 2 |         |                                                                |            |  |  |

|---|----------------------------------------------------------------|---------|----------------------------------------------------------------|------------|--|--|

|   | 3.1                                                            | Propo   | sed Design                                                     | 25         |  |  |

|   | 3.2                                                            | Metho   | odology & Results                                              | 28         |  |  |

| 4 | CO                                                             | RDIC    | is All You Need                                                | 33         |  |  |

|   |                                                                | 4.0.1   | Why is the Need                                                | 39         |  |  |

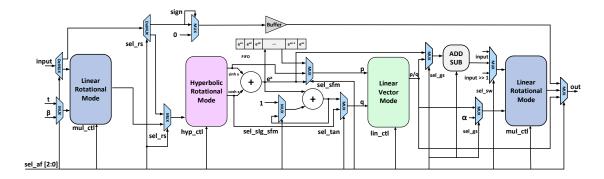

|   | 4.1                                                            | Propo   | sed Neuron Architecture (RPE)                                  | 41         |  |  |

|   |                                                                | 4.1.1   | CORDIC algorithm                                               | 43         |  |  |

|   |                                                                | 4.1.2   | Proposed 5+2 RPE Architecture                                  | 48         |  |  |

|   |                                                                | 4.1.3   | Details of Data and Control Signals and and State Machine      |            |  |  |

|   |                                                                |         | for Neuron Engine                                              | 50         |  |  |

|   |                                                                | 4.1.4   | Optimizations for Next-Generation Workloads: DA-VINCI          | 52         |  |  |

|   | 4.2                                                            | Param   | neterized and Modular Systolic Accelerator Architecture        | 54         |  |  |

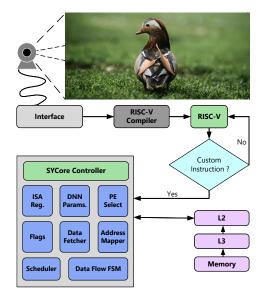

|   |                                                                | 4.2.1   | Host Interfacing                                               | 56         |  |  |

|   |                                                                | 4.2.2   | Design and System Architecture Overview                        | 58         |  |  |

|   |                                                                | 4.2.3   | Dataflow and Functioning of the array                          | 61         |  |  |

|   | 4.3                                                            | Evalua  | ation                                                          | 63         |  |  |

|   |                                                                | 4.3.1   | Experimental Setup and Validation                              | 64         |  |  |

|   |                                                                | 4.3.2   | Software-Based Evaluation and Validation of Inference Accuracy | 65         |  |  |

|   |                                                                | 4.3.3   | Pareto Analysis of RPE Design Parameters: Pipeline Stages,     |            |  |  |

|   |                                                                |         | Bit-Precision, and Integer Bits, etc. other design parameters  |            |  |  |

|   |                                                                |         | (MAC level comparison and Pareto)                              | 66         |  |  |

|   |                                                                | 4.3.4   | Hardware Implementation and Comparative Performance Anal-      |            |  |  |

|   |                                                                |         | ysis (Architectural Level of analysis)                         | 68         |  |  |

|   |                                                                | 4.3.5   | Evaluating Hardware Parameters for Optimal deep neural         |            |  |  |

|   |                                                                |         | network (DNN) Performance                                      | 69         |  |  |

| 5 | Cor                                                            | nclusio | n & Future Scope                                               | <b>7</b> 3 |  |  |

| 6 | List                                                           | of Pu   | blications                                                     | 75         |  |  |

## List of Figures

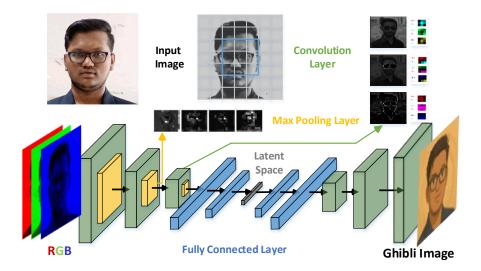

| 1.1 | Overview of the neural network architecture for generating Ghibli-style |    |

|-----|-------------------------------------------------------------------------|----|

|     | RGB images from input images via latent space transformation            | 3  |

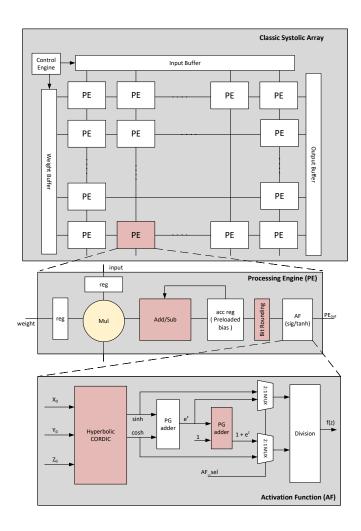

| 1.2 | Classic 2D systolic array architecture with PE highlighting the regions |    |

|     | to be improved.                                                         | 4  |

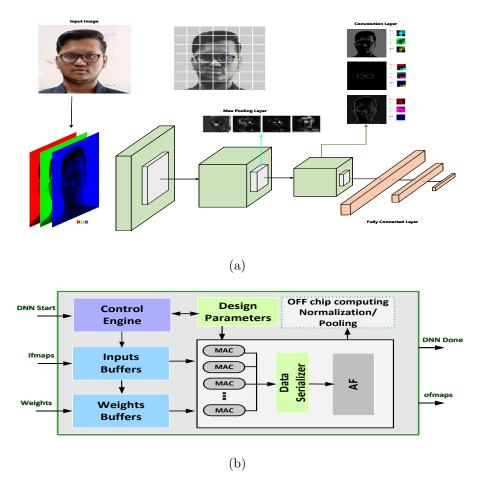

| 1.3 | Deep Neural Networks (a) A typical DNN model, (b) A classic DNN         |    |

|     | accelerator architecture show<br>casing data control and interface      | 6  |

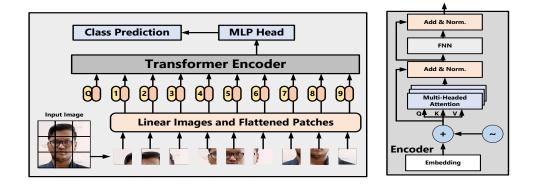

| 1.4 | Typical demonstration of Transformers model, depicted intermediate      |    |

|     | layers such as Conv, Pooling, MHA, and FFNN                             | 8  |

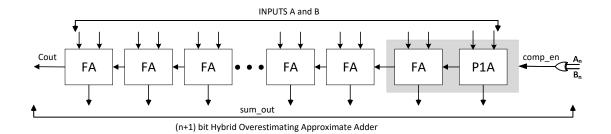

| 2.1 | N - Bit Re-Configurable Adder, (n+1) bit HOAA                           | 13 |

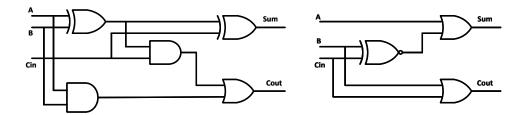

| 2.2 | 1-bit Schematic of a) Conventional Full Adder b) Plus One Adder         | 18 |

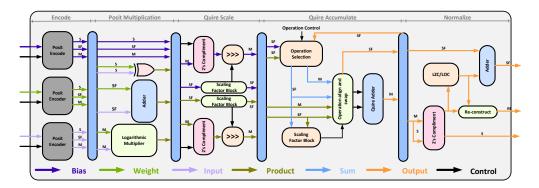

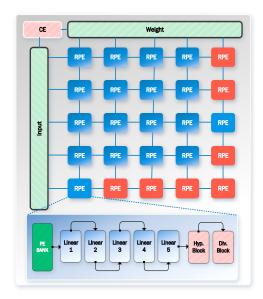

| 3.1 | The detailed microarchitecture of 5-stage Logarithmic Posit Quire       |    |

|     | Processing Engine (PQRE)                                                | 25 |

| 3.2 | Proposed Logarithmic Posit-Enabled Reconfigurable edge-AI Engine        |    |

|     | architecture                                                            | 26 |

| 3.3 | Inference accuracy evaluation with the proposed Logarithmic Posit       |    |

|     | Quire Processing Engine compared to the baseline FP [1] and SoTA        |    |

|     | INT/FxP [2, 3] accuracy. (a) LeNet-5 on MNIST (b) AlexNet on            |    |

|     | CIFAR-10                                                                | 29 |

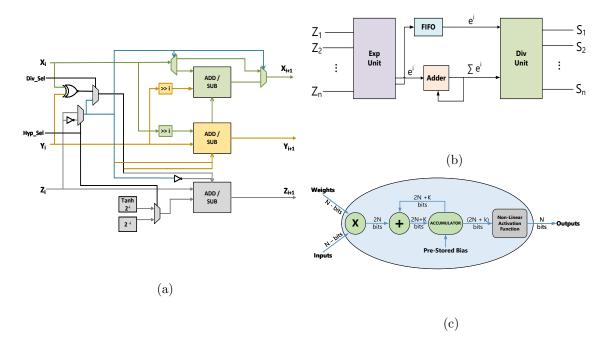

| 4.1 | a) CORDIC Stage-1 fundamental element b) Reconfigurable Activation      |    |

|     | function using RPE c) Conventional Processing Engine                    | 42 |

| 4.2 | Reconfigurable Activation function using RPE                            | 45 |

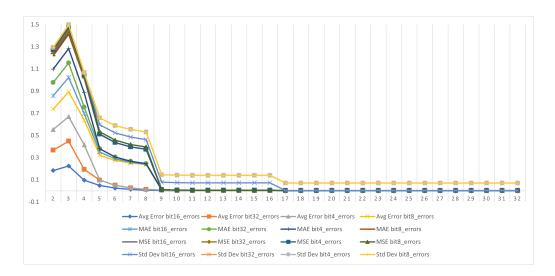

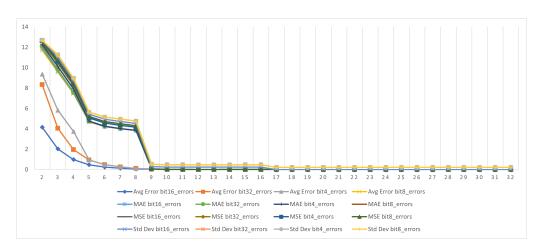

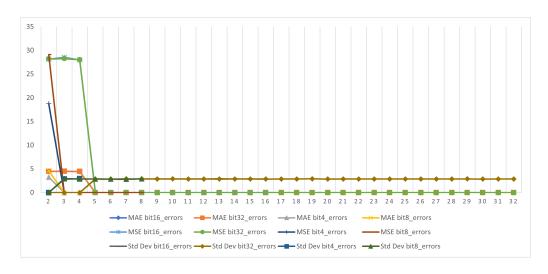

| 4.3  | Pareto Analysis of sigmoid for various error plot                                              | 47 |

|------|------------------------------------------------------------------------------------------------|----|

| 4.4  | Pareto Analysis of tanh for various error plot                                                 | 47 |

| 4.5  | Pareto Analysis of softmax for various error plot                                              | 47 |

| 4.6  | $\label{thm:configurable} Dynamically-configurable activation function supporting GeLU, SeLU,$ |    |

|      | Swish, ReLU, Tanh, Sigmoid and Softmax                                                         | 54 |

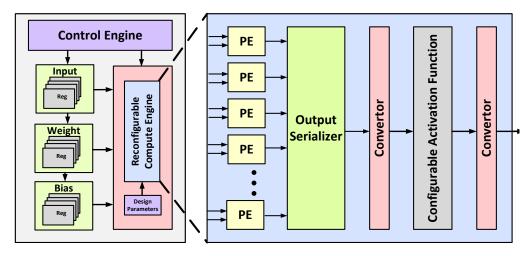

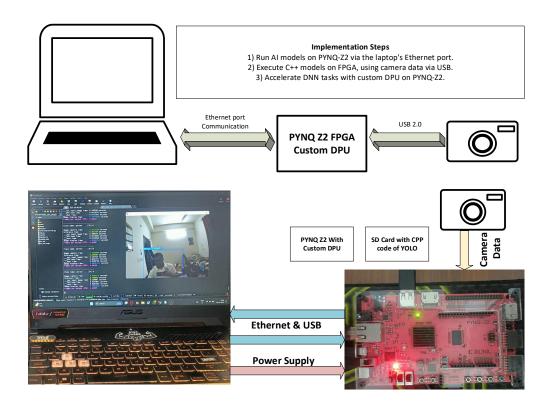

| 4.7  | Host Interfacing                                                                               | 58 |

| 4.8  | Systolic Array                                                                                 | 58 |

| 4.9  | Pynq Z2 Custom DPU Prototype Implementation                                                    | 60 |

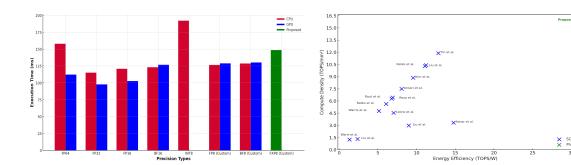

| 4.10 | Accuracy at Several Deep Neural Nets                                                           | 66 |

| 4.11 | Execution time for different precision at CPU and GPU platforms                                |    |

|      | compared to proposed model                                                                     | 69 |

| 4.12 | Performance analysis at CMOS 28 nm and comparison with SOTA                                    |    |

|      | works                                                                                          | 69 |

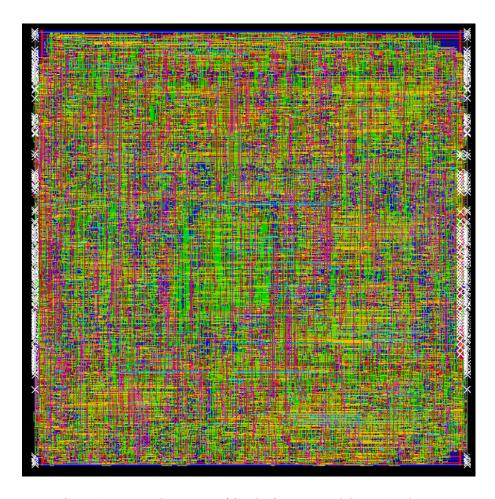

| 4.13 | Graphic Data System II(GDSII) image of Systolic Array design using                             |    |

|      | Cadence Innovus                                                                                | 71 |

## List of Tables

| 1.1 | State-of-the-art approximate adders and their implications on neural    |    |

|-----|-------------------------------------------------------------------------|----|

|     | network inference accuracy                                              | 5  |

| 1.2 | State-of-the-art precision and their impact on Hardware Accelerators    |    |

|     | for neural network inference                                            | 7  |

| 2.1 | Truth table for accurate and approximate P1A adder designs, including   |    |

|     | all input combinations, output sum, and carry bits                      | 17 |

| 2.2 | Error metrics evaluation for 8-bit HOAA design $\ast$ All values are in |    |

|     | percentage scale                                                        | 20 |

| 2.3 | Physical Design Parameters at CMOS 28 nm, VDD 0.9V, frequency           |    |

|     | 100 MHz                                                                 | 21 |

| 3.1 | Comparison of FPGA Resource Utilization for proposed PQRE with          |    |

|     | SIMD FP MAC Unit [1] and SoTA MAC works [2–4]                           | 28 |

| 3.2 | Hardware Utilization Report for Various Architectures with CORDIC-      |    |

|     | based FxP MAC and Our PQRE                                              | 30 |

| 3.3 | Comparison of FPGA Resource Utilization in Different Precision and      |    |

|     | Datatype $[3,5,6]$ with Proposed Posit AF                               | 31 |

| 4.1 | State-of-the-art AI Models and their corresponding multiply-and-        |    |

|     | accumulate (MAC) Units and parameters with the necessity for Hard-      |    |

|     | ware Optimization                                                       | 39 |

| 4.2 | Detailed CORDIC equations: general, linear and hyperbolic               | 43 |

| 4.3  | Detailed mapping and scheduling for VGG-16/CIFAR-100 with Pro-  |    |  |  |  |  |  |

|------|-----------------------------------------------------------------|----|--|--|--|--|--|

|      | posed RISC-V Enabled SYCore Architecture                        | 59 |  |  |  |  |  |

| 4.4  | FPGA MAC comparison                                             | 64 |  |  |  |  |  |

| 4.5  | ASIC MAC comparison on 28 nm                                    | 64 |  |  |  |  |  |

| 4.6  | ASIC MAC comparison on 7 nm                                     | 64 |  |  |  |  |  |

| 4.7  | Hardware Implementation Report with Proposed Systolic Array Ar- |    |  |  |  |  |  |

|      | chitecture and State-of-the-Arts DNN Designs                    | 68 |  |  |  |  |  |

| 4.8  | FPGA Resources Utilization, compared with prior works           | 70 |  |  |  |  |  |

| 4.9  | ASIC Resources Utilization, compared with prior works           | 70 |  |  |  |  |  |

| 4.10 | Comparative cost performance analysis with SOTA solution        | 72 |  |  |  |  |  |

### List of Abbrevations

DL - Deep Learning

ML - Machine Learning

AI - Artificial Intelligence

DNN - Deep Neural Network

SRAM - Static Random Access Memory

RCA - Ripple carry adder

CSkA - Carry skip adder

SoC - System-on-Chip

ASIC - Application Specific Integrated Circuit

STA - Static Time Analysis

IC - Integrated Circuits

P1A - Plus One Adder

PE - Processing Engine

AF - Activation Function

PQRE - Logarithmic Posit Quire Processing Engine

MAC - Multiply and Accumulate

LPRE - Logarithmic Posit-enabled Reconfigurable edge-AI Engine

SA - Systolic Array

CORDIC - Coordinate Rotation Digital Compute

HOAA - Hybrid Overestimating Approximate Adder

LUT - Look-Up-Table

FPGA - Field-Programmable Gate Arrays

SoTA - State of the Art

RPE - Reconfigurable Processing Engine

## Chapter 1

## Introduction

#### 1.1 Introduction

Artificial Intelligence and Machine Learning (AI/ML) have been extensively implemented and embraced across various technological domains as shown in Fig. 1.1. Among the myriad algorithmic frameworks, **DNNs** have captured significant attention due to their vast applicability in fields like science, engineering, agriculture, healthcare, etc. DNNs have revolutionized image classification, audio recognition, and natural language processing [7]. DNNs are structured with multiple layers, starting from the input, passing through several hidden layers, and concluding with the output layers. During inference, these layers form a directed acyclic graph with nodes and edges leading to neurons in subsequent layers. Each node, or neuron, executes two core tasks: First, it employs a Multiply, Add and Accumulate (MAC) unit to aggregate the weighted input features and second, it applies the Activation Function(AF) to the resulting sum. A deep neural network (DNN) is a type of Artificial Neural Network (ANN) that consists of multiple hidden layers between the input and output, typically structured as either a Convolutional Neural Network (CNN) or Fully Connected (FC). Researchers have focused on developing specialized hardware solutions, including Application-Specific Integrated Circuits (ASICs), Graphics Processing Units (GPUs), Field-Programmable Gate Arrays (FPGA), and multi-threaded CPUs [8–10], to enhance the efficiency of DNN implementations.

Deep Neural networks (DNN) have become ubiquitous in edge-AI devices, powering applications like facial recognition, object detection in computer vision, chatbots for human-like interactions, sentiment analysis in online shopping, social media, etc. In recent years, the models have grown exponentially in size and complexity [?], contributing to improved prediction accuracy and effectiveness, potentially raising significant concerns for hardware platforms that are used for real-time inference. Software-level techniques like quantization and pruning help to provide smaller models for smooth inference [11]. However, to provide the best user experience, the need for hardware accelerators has rapidly evolved for resource-constrained environments [11, 12]. The edge accelerator must have special computing blocks to

Figure 1.1 Overview of the neural network architecture for generating Ghibli-style RGB images from input images via latent space transformation.

efficiently process various Convolution, Pooling, and Fully connected Layers. At the circuit level, the fundamental parallel components are Multiply-and-Accumulate (MAC) [13] operations and Non-linear Activation Functions (AF) [12]. However, as the main processor offloads these tasks to the accelerator, the need to support less frequent operations like Subtraction, Rounding, and Pooling operations has also arisen. Otherwise, these smaller workloads would contribute to more power consumption as these operations would need to be processed by a general-purpose processor and involve significant data movement. Understanding the trade-off between the NN performance vs physical parameters of hardware resources aids in accelerating the efficient acceleration of DNN solutions. Researchers [14–16] have explored architectural optimization at various abstraction levels, including fixed-point (FxP) arithmetic, hardware reuse/reduction, and approximation.

#### 1.1.1 Background & Motivation

#### 1.1.1.1 Hybrid Overestimating Approximate Adder (HOAA)

The article has discussed one fundamental digital block binary adder. The adders are widely adapted in ALUs (addition, subtraction) in microprocessors, Shift-Add-based MAC units, Coordinate Rotation Digital Computer (CORDIC) based

transcendental functions, etc. The conventional accurate adders [14, 15] involve Ripple Carry Adders (RCA), Carry Look-Ahead Adders (CLA), Carry Bypass Adders (CBA), Carry Select Adders (CSA), Tree Adders, Serial Adders, Brent Kung Adders (BKA), Kogge Stone Adders (KSA), etc. However, The last decade has seen the rise of approximate adders by modifying the carry chain, half adder (HA), full adder (FA), compressor or reducing logic gates.

**Figure 1.2** Classic 2D systolic array architecture with PE highlighting the regions to be improved.

The authors [15,16] discussed the Area-Precision, Power-Precision, and Delay-Precision trade-off points for some of the approximate adders such as Almost Correct Adder (ACA-I/II), Quality-area optimal low-latency approximate Adder (QuAd), Equal Segmentation Adder (ESA), Error-Reduced Carry Prediction Approximate

full Adder (ERCPAA), Generic Accuracy configurable adder (GeAr), Area-Power Efficient approximate adder (APEx), Error-Tolerant Adder (ETA-I/II), Lowest-cost Imprecise Adders (LIA) with error induced in the diverse application scenarios. ACA-I, ACA-II, and QuAd are designed to exploit the area-accuracy tradeoff by targeting less significant parts of an adder in an error-controlled manner. ESA, ERCPAA, and ETA-II focus on the decreasing critical path with less accurate computations while maintaining accuracy. ESA, GeAr allows the processing of additions in equal segments, configurable as per application requirements, and illustrates the basic principle behind HOAA concept. APEx, LIA focuses on the reduction of power for applications where exact results are not critical. Considering the error resiliency of neural networks, the techniques mentioned above may not affect output accuracy up to a certain point; however, beyond this threshold, enhancing physical design parameters often involves sacrificing accuracy, highlighting the importance of evaluating ideal trade-offs.

Table 1.1 State-of-the-art approximate adders and their implications on neural network inference accuracy

| Adder Unit | # of gates | Hardware Efficiency | % Improvement | Accuracy             |

|------------|------------|---------------------|---------------|----------------------|

|            |            | (Area-Power-Delay)  |               | ${\rm Overhead}(\%)$ |

| FA         | 40         | N/A                 | N/A           | 0                    |

| HADD       | 32         | Area, Power         | 50            | -1.5                 |

| LOA        | 25         | Area, Power, Delay  | 60            | -3                   |

| ACA        | 32         | Power               | 45            | 0                    |

| AMA        | 20         | Power               | 70            | N/A                  |

# 1.1.1.2 Logarithmic Posit-enabled Reconfigurable edge-AI Engine (LPRE):

The rapid development of AI applications in Mobile and IoT devices has elevated a strong need for efficient data processing, as new edge computing devices suffer

**Figure 1.3** Deep Neural Networks (a) A typical DNN model, (b) A classic DNN accelerator architecture showcasing data control and interface.

from many challenges when running AI workloads due to the memory wall and resource constraints [17]. To address the challenges, researchers have focused on deep neural network (DNN) accelerators to achieve speed, power, and performance improvements [18]. High-performance computing platforms, such as TPU, GPU, and ASIC/FPGA accelerators, are utilized rather than CPU-based serial execution. Significant research has been carried out in hardware-software co-design [19], architectural optimizations [3, 20], parameter reduction [21], and evolution of diverse number systems [1, 22] and data types [23].

DNNs rely heavily on billions of multiply-accumulate (MAC) operations, especially in convolutional and multi-layer perceptron layers. A typical DNN model with accelerator architecture is shown in Figure 1.3(a). Thus, optimizing the MAC units

is critical for improving system performance without creating bottlenecks in other components, including activation functions (AF), normalization layers (NORM), and pooling layers (POOL) [24]. State-of-the-art (SoTA) solutions, such as Systolic accelerators [25–27] and reconfigurable accelerators [5, 28, 29] typically focus on the resources consumed by MAC computations, while ensuring optimal data flow. Software optimization techniques, such as quantization [21,26], pruning [30], and using custom precision formats (e.g., fixed-point (FxP) [3,27], posit [4], logarithmic [22], BF16, and TF32 [1,6]) help significantly reduce hardware demands for efficient execution. However, these techniques may lead to accuracy degradation in some applications, thus affecting system performance [3, 5]. A comparison of SoTA methodologies (precision) with their impact on inference hardware is provided in Table 1.2.

**Table 1.2** State-of-the-art precision and their impact on Hardware Accelerators for neural network inference

| Precision | Data format          | Max normal                 | Min normal                   | Subnormal | Resource Overhead | Accuracy Loss | Throughput |

|-----------|----------------------|----------------------------|------------------------------|-----------|-------------------|---------------|------------|

| FP32      | 1, 8, 23             | $3.4028235 \times 10^{38}$ | $1.17549435 \times 10^{-38}$ | Yes       | High              | None          | Low        |

| FP16      | 1, 5, 10             | 65504                      | $6.1035156 \times 10^{-5}$   | Yes       | High              | Minor         | Medium     |

| FP8       | 1, 4, 3              | 240                        | 0.015625                     | Yes       | Low               | Moderate      | Medium     |

| INT32     | 1,31                 | $2.147 \times 10^{9}$      | $-2.147 \times 10^{9}$       | No        | Medium            | Minor         | Low        |

| INT16     | 1, 15                | 32767                      | -32768                       | No        | Low               | Moderate      | Medium     |

| INT8      | 1,7                  | 127                        | 128                          | No        | Low               | Moderate      | High       |

| POSIT32   | 1, r, es, (n-r-es-1) | $1.84467 \times 10^{19}$   | $5.42101 \times 10^{-20}$    | No        | Medium            | None          | Medium     |

| POSIT16   | 1, r, es, (n-r-es-1) | $4.29 \times 10^{9}$       | $2.33 \times 10^{-10}$       | No        | Low               | None          | High       |

| POSIT8    | 1, r, es, (n-r-es-1) | 65536                      | $1.526 \times 10^{-5}$       | No        | Low               | Minor         | High       |

This work majorly focuses on a Logarithmic Posit-based arithmetic reconfigurable architecture, which maintains application accuracy (compared to baseline FP32) while saving significant hardware resources. An input-output multiplexing scheme and sparsity exploitation further enhance the memory bandwidth and computation efficiency.

#### 1.1.1.3 CORDIC-Neuron

ASICs are specialized hardware optimized for a specific task, sacrificing the adaptability of a reconfigurable architecture for improved power efficiency compared to platforms such as FPGAs and GPUs. These latter platforms, while more versatile

and capable of executing a variety of tasks, tend to have higher power consumption [31, 32. FPGAs provides cost efficiency, and flexibility, with limited on-chip memory and resources [32]. Thus, innovative design methodologies are required to manage the area, complexity, and reconfigurability challenges in DNNs. Additionally, a DNN comprises various layers, including CNN, feed-forward, normalization, longterm short-term memory (LSTM), Gated Recurrent Unit (GRU), pooling, and activation layers like Rectified Linear Unit(ReLU), tanh, and sigmoid [8,33]. The core components of a DNN model are the Processing Engines (PEs), or artificial neurons. These involve multiplication and accumulation processes followed by a nonlinear AF. Multiplication and accumulation operations, handled by MAC units through complex adder and compressor design, are computationally intensive. The output is then subjected to nonlinear transformations using AFs such as sigmoid, tanh, and ReLU, commonly employed in DNNs [34]. Activation functions are crucial in DNN architectures to enable features like model size reduction and prevention of overfitting issues [35]. Various methods, including LookUp-Tables (LUT), COordinate Rotation DIgital Computer (CORDIC), and PieceWise Linear (PWL), can implement these Activation Functions. While some designs are resource-intensive in terms of area and power, the CORDIC design is praised for its area and power efficiency; however, a considerable limitation is its low throughput.

Figure 1.4 Typical demonstration of Transformers model, depicted intermediate layers such as Conv, Pooling, MHA, and FFNN

Prior AI accelerator designs prioritize area and power efficiency and focus on the

CORDIC computational algorithm [33,36–38]. This design comprises fundamental logic components, including a shift register, adder/subtractor circuits, multiplexers, and some memory elements that facilitate a range of arithmetic operations while consuming less power. CORDIC algorithm, introduced by Jack E. Volder in 1959, has the adaptability to conduct several arithmetic operations. Mathematically, it achieves linear convergence with minimal resource use [34]. Through shift and add-sub operations, the CORDIC architecture can execute numerous tasks, such as trigonometric, hyperbolic, and logarithmic functions via vector rotation [39]. We employ CORDIC in rotation mode to achieve the tanh and sigmoid functions, akin to computing hyperbolic functions as exponential terms. Moreover, CORDIC can determine square roots and more. The widely used SoftMax function can also be implemented through CORDIC hardware, which is crucial for various classification tasks and is predominantly used in transformer architectures and capsule networks.

#### 1.2 Research Objectives

The primary objective of this research is to investigate and develop a novel AI accelerator architecture for Edge AI applications. The specific research objectives include:

- Designing a HOAA-enabled CORDIC PE, with a focus on improving speed, energy efficiency, and area efficient compared to conventional SoTA designs.

- Developing efficient posit engine designs and performance tradeoff to boost computation within Vector Engine, leveraging the AI workload characteristics (sparsity).

- Implementing a architecture CORDIC-based RISC-V enabled Systolic array:

AI SoC and conducting comprehensive performance evaluations to validate the

effectiveness of the proposed architecture in real-world scenarios.

- Exploring the potential applications and practical implications for various computing tasks, such as neural networks, and AI inference.

#### 1.3 Organization of Thesis

This thesis is organized into several chapters, each focusing on different aspects of the research conducted on AI accelerator architectures for resource efficient edge AI acceleration. The chapters are structured as follows:

Chapter 1: This chapter provides the background and motivation for the research, highlighting the increasing demands of data-intensive applications and the need for high-speed, energy-efficient solutions.

The literature review offers a comprehensive overview of DNN, including existing accelerator implementations and various types. This chapter sets the stage for the novel contributions of this research by discussing the limitations of current technologies and the potential improvements with CORDIC circuit. It introduces Systolic array architectures required for the data-intensive applications. The chapter concludes with the research objectives and a brief overview of the thesis organization.

Chapter 2: This chapter details the design and implementation of HOAA-optimized PE design to enhance the performance. The work covers the structure of the novel HOAA, its operation, incorporation into CORDIC-PE including an its PPA impacts.

Chapter 3: This chapter details the design and implementation of PQRE to incentivize the posit-based MAC, AF operations. The work covers the structure of the novel compute unit and its incorporation into LPRE structure, including an analysis of the its impacts and a performance evaluation at the FPGA prototype.

Chapter 4: This chapter details the design and implementation of resource-constrained CORDIC PE design to enhance the performance of systolic array. The work covers the structure of the novel PE, its operation, incorporation into systolic array structure and integration with RISC-V, including an performance evaluation for the edge applications.

Chapter 5: The final chapter summarizes the key findings and contributions of the research. It discusses the implications of the novel HOAA-enabled PE, LPRE and CORDIC-based systolic array design with RISC-V integration. Additionally, it outlines potential directions for future research to further enhance the performance and applicability.

## Chapter 2

HOAA: Hybrid Overestimating

Approximate Adder for Enhanced

Performance Processing Engine

Figure 2.1 N - Bit Re-Configurable Adder, (n+1) bit HOAA.

There has been a sudden rise in the development of edge AI chips due to the high demand for running complex models and the need for optimized GEMM operations, which dominate the inference time. For instance, Google's Tensor Processing Unit (TPU) comprises 64K MAC units, and Samsung's Neural Processing Unit (NPU) has 6K MAC units [?,16]. The DNN workloads LeNet, AlexNet, ResNet-50, and VGG-16 require 0.34M, 724M, 3.9B, and 15.5B MAC units [?,11,12]. The processing element (PE) is the basic compute unit in a Convolutional Neural Network (CNN) accelerator, contributing to 90% of energy efficiency. The PE comprises a multiplier followed by an adder, combined as MAC and AFs like Sigmoid/Tanh. The fundamental block in the shift-add/sub-based CORDIC implementation [12] of PE is an adder. The equation 2.1 calculates the Sum and Carry in conventional FA.

$$Sum = A \oplus B \oplus C_{in}$$

$$Cout = (A \cdot B) + (C_{in} \cdot (A \oplus B))$$

(2.1)

Various Adders have been proposed with different FA and HA combinations to fit the appropriate power, performance, and area trade-offs as shown in Table. 1.1 according to various application scenarios. RCAs involve sequential carry propagation of parallel carry determination in CLA [12]. CBA selectively bypasses critical carry to optimize delay while CSA uses MUX to parallelize carry, showcasing area-speed tradeoff. While serial adders are suitable for low-power applications, Tree adders support distributed arithmetic with a hierarchical structure. BKA and KSA leverage parallel prefix carry computations suitable for high-performance, scalable applications. Further, Given the inherent error-tolerant nature of CNNs,

approximate computing methods have been explored widely for high hardware efficiency in implementing accelerators. Approximation is a vital element in enhancing physical design parameters and simplifying complex architecture by exploiting natural irregularities in real-time systems. The approach addresses resource management, with efficient circuits and helps for achieving faster and reduced computational demands. The design of approximate circuits involves using Majority-logic, modifying or removing logic gates from accurate circuits, or simplifying the Karnaugh map (K-map). From the initial application of approximate adders to boost the clock frequency of microprocessors in 2004, the AC applications have been automated with various innovative designs like the almost correct adder (ACA), the errortolerant adder (ETA), the equal segmentation adder (ESA), and the approximate mirror adder (AMA), etc. The inherent redundancy in neuron computations and minimal degradation due to approximation errors open opportunities for trade-offs in energy efficiency, and compute density, making them ideal for resource-constrained environments like edge-AI devices. Additionally, the use of approximate adders can improve speed and throughput, leading to faster response time. Though beyond a certain error threshold, the performance of neural networks degrades noticeably, the approximation shall be tuned for efficient inference across diverse applications. A hybrid combination of conventional adders for MSBs and approximate adders for LSBs ensures minimum accuracy degradation (less than 5%) with the equations provided in 2.2. This also ensures significant hardware efficiency in multi-bit fixed-point precision adders.

$$Sum = (A + Cin) \oplus B$$

$$Carry = (A + Cin) \cdot B$$

(2.2)

PE has been pivotal for the efficiency of the DNN accelerator as it contributes to 90% operations. Despite huge efforts put in to enhance the performance, the PE encounters major performance fallback linked with the +1 operation. In **Signed MAC units**, +1 operation is crucial during Two's complement subtraction. In the quantization, **Rounding to even** technique employed within PE requires

+1, contributing to one cycle delay. Configurable Activation Function with CORDIC methodology involves frequent +1 operation affecting the performance of overall PE and, subsequently, the entire systolic array DNN accelerator. The overhead would typically be the delay of one clock cycle in serial adders or area overhead in parallel adders, along with huge power consumption, depending on the bit precision of operands involved. An approximate P1A has been proposed to address the limitation, which performs the +1 operation within the same processing cycle. Therefore, the associated area or latency could be reduced by trading off slight accuracy in the runtime. We further analyzed the impact as well. Further dynamically reconfigurable P1A within the RCA chain has been proposed as novel HOAA. Hybrid approach-based HOAA ensures the runtime reconfigurability between FA and P1A enabling future scope for OEA. Different bit-width segments can be utilized with an approximate multiplier based on an error-controllable mechanism, fundamentally improving accuracy loss due to logarithmic MAC operations.

The Chapter talks about an n-bit Hybrid Overestimating Approximate Adder to simplify advanced arithmetic operations with minor area overhead. The principal contributions of this work are:

- 1. Resource efficient Plus One Adder (P1A): An incremental approximate adder is proposed that can be incorporated into the RCA chain, which provides excess-1 output. The design approximates certain outputs to reduce hardware overhead; Hence, corresponding error metrics are also evaluated.

- 2. **Dynamically Re-configurable HOAA:** HOAA adder architecture is proposed to be capable of runtime interchangeability by replacing the m-LSB FAs of RCA with P1A. This saves one clock cycle and supports multiple arithmetic operations with the same hardware blocks.

- 3. Evaluations for versatile test cases: The proposed design is evaluated on Two's complement subtraction, Rounding-to-even and Configurable AF. Monte Carlo-based error distance calculations are provided. The ASIC physical design performance parameters are evaluated at CMOS 28nm.

#### 2.1 Proposed Architecture

We discuss the implementation of a P1A adder and extend it to HOAA architecture. We also evaluated the error analysis for the use cases with corresponding error metrics to demonstrate resource-efficient design. [29]

#### 2.1.1 Proposed P1A Design

Signed MAC operations use an RCA chain with FAs in the accumulator stage. Tradition FA 2.1 uses five logic gates are used to compute the sum and carry. However, reusing the adder as Two's complement-based subtraction typically consumes two-cycle latency and power consumption for N-bit operation. We identified the necessity of a +1 adder to address the issue and proposed the circuitry based on a modified truth table 2.1 with the Karnaugh Map technique. Further, to obtain the approximate P1A, we evaluated the error metrics and corresponding hardware costs. The accurate +1 adder and approximate P1A equations are shown in Eq. 2.3, 2.4 respectively. Compared to FA, the proposed P1A uses only three logic gates, highlighting hardware efficiency. The incorrect outputs are highlighted in Table 2.1. The truth table shows two errors in sum and carry-bit. Further, the error rate analysis is provided to justify the proposed approximations.

$$Sum = A \cdot C_{in} + B \cdot A + B \cdot C_{in} + \overline{A} \cdot \overline{B} \cdot \overline{C_{in}},$$

$$Carry = A + B + C_{in}.$$

(2.3)

The circuit modifies with circuitry around to provide two modes with the same HOAA(N,m) to support both operations. The FAs are utilized during normal addition while keeping the P1A block disabled with PG for normal addition. Conventional N-bit RCA was modified typically by replacing the LSB adder with P1A for subtraction operation as illustrated in Fig. 2.1, which also ensures the direct addition of excess-1 to LSB position and faster subtraction operation within the same cycles as that of addition. Notably, with increased adder size, the error introduced by P1A vanishes, approaching better suited for scalable architectures with minimal static

**Table 2.1** Truth table for accurate and approximate P1A adder designs, including all input combinations, output sum, and carry bits

| A | В | Cin | Accurate P1A Output |      |       | Approx. P1A Output |      |

|---|---|-----|---------------------|------|-------|--------------------|------|

| A |   |     | Sum                 | Cout | Cout2 | Sum                | Cout |

| 0 | 0 | 0   | 1                   | 0    | 0     | 1                  | 0    |

| 0 | 0 | 1   | 0                   | 1    | 0     | 0                  | 1    |

| 0 | 1 | 0   | 0                   | 1    | 0     | 0                  | 1    |

| 0 | 1 | 1   | 1                   | 1    | 0     | 1                  | 1    |

| 1 | 0 | 0   | 0                   | 1    | 0     | 1*                 | 0*   |

| 1 | 0 | 1   | 1                   | 1    | 0     | 1                  | 1    |

| 1 | 1 | 0   | 1                   | 1    | 0     | 1                  | 1    |

| 1 | 1 | 1   | 0                   | 0    | 1     | 1*                 | 1*   |

power consumption.

#### 2.1.2 Proposed HOAA Design

We evaluated two approaches to fit the proposed P1A into the adder design to support subtraction within the same processing cycle adaptively. The first approach was based upon Reconfigurable Approximate CLA, which would provide the reconfigurable ability to switch between approximate and accurate modes with MUX. The second approach involved using (N,m) adders as a combination of conventional and approximate adders, which has also been standard practice for hardware efficiency with minimal accuracy degradation. The runtime selection signal comp\_en has been generated based on MSBs of both operands for the selection between P1A and HA. This enables generalization and provides a template for a scalable architecture. Further, the approximate adders could be power gated when

Figure 2.2 1-bit Schematic of a) Conventional Full Adder b) Plus One Adder.

not required; however, this has not been evaluated in this work. [5]

$$Sum = A + \overline{B \oplus Cin}$$

$$Cout = B + Cin$$

(2.4)

Delay is one of the important parameters in PPA analysis. Even the SOTA studies highlight the importance of varied propagation delay per individual logic gates' properties. The propagation delay analysis for the sum and carry-bit of 1 bit P1A can be found in equations 2.5. The further analysis of (N,m) HOAA follows the methodology per HADD/LOA adders. The equation 2.4 highlights linear area savings as the number of gates increases with bit-precision. Compared to the conventional adder, this would be an additional reduction in delay for any n-bit precision operation due to P1A.

$$T_{sum} = T_{xnor} + T_{or}$$

$$T_{carry} = T_{or}$$

(2.5)

#### 2.2 Methodology & Results Discussion

The Conventional full adder (FA) truth table was modified by directly adding +1 to the Cout, Sum outputs while calculating the P1A equations. This modified truth table was then converted to Boolean equations using Karnaugh maps (K-maps), producing accurate equations 2.3. However, the decision to introduce approximation was made due to the increased hardware cost of the equation. After evaluating numerous cases of the proposed addition and the corresponding accuracy loss, an

approximate +1 adder was proposed, as per equation 2.4 and error analysis is mentioned in Table 2.2. The timing analysis can be done for a single P1A as per equation 2.5, replacing the combinational delay for a particular HA within RCA. Compared to conventional FA (28T), P1A requires only 16 transistors, significantly saving the CMOS area.

The proposed design has been validated with hardware-software co-design emulation flow for the experimental analysis. Google Colab Notebook with Python v3.0 has been utilised for error metrics calculations as per [12, 15, 16]. The functional emulation for the proposed hardware architecture was done with the of Python v3.0 and the error metrics were calculated as shown in Table 2.2. The quantitative measurement of error introduced due to approximation, and its impact on performance, and quality of approximate neural networks, further to assist designers in understanding the more suitable trade-offs for particular applications, error metrics are essential. The error metrics to evaluate the accuracy loss incurred include Mean Square Error (MSE), Normalised Mean Error Distance (NMED), and Mean Relative Error Distance (MRED) [12,15]. MSE provides overall error magnitude, as in the average squared difference between exact and approximate results. The MSE less than 2\% shows the efficiency of design for all the test cases. NMED and MRED give a relative measure of error and indicate error scaling with architecture. MRED and NMED around 6% show the comparison of errors across different scale and application scenarios. Further, The Verilog RTL code for the proposed Adder was written and functionally validated using Xilinx Vivado 2023.2 for hardware implementation. During ASIC analysis, the 8-bit HOAA is synthesized with Synopsys Design Compiler using CMOS 28nm PDK at a power supply of 0.9V for the configurations shown in Table 2.3. The physical parameters were evaluated at the HPC+ node, considering the better compute density, reduced area-power-dealy, and industry-adopted solution for resource-constrained scenarios. Monte-Carlo simulations for uniformly distributed  $2^{n+1}$  times random input pattern variable. For the calculation of error metrics 2.2, the simulations were computed on random inputs and were compared with true outputs from Python Numpy. Approximation trade-offs were evaluated to check the

Table 2.2 Error metrics evaluation for 8-bit HOAA design

\* All values are in percentage scale

| Error Metrics | Case-I  | Case-II | Case-III |

|---------------|---------|---------|----------|

| MSE           | 0.02444 | 0.02406 | -0.06766 |

| NMED          | 0.02444 | 0.02406 | 0.06766  |

| MRED          | 0.06834 | 0.06729 | 0.06759  |

accuracy and compare the adder architectures. The proposed adder signifies minimal accuracy loss compared to LOA while absolute gains in PPA design parameters relative to FA, AMA, HADD, and SESA-I. P1A shows an improvement of around 5% in area compared to HADD [13] and AMA [40], while consuming approximately 15% less power than HADD [13] and SESA-I [41]. Additionally, P1A demonstrates a 21% reduction in area and a 33% reduction in power consumption compared to the conventional FA. The slack calculation is performed with a period of 10ns or an operating frequency of 100 MHz, and the value reflects a smaller improvement in timing margins compared to FA and hence, a higher operating frequency. The count and placement of reconfigurable P1A in HOAA can be error-controlled while the decision to choose HOAA can be made on the evaluation of MSE, NMED, and MRED (Refer to Table 2.2) vs physical parameters (Refer to Table 2.3). However, while the error metrics are preliminary factors, a thorough analysis should be carried out for real-world DNN workloads.

#### 2.2.1 Case-I: Subtraction

Two's complement-based subtraction in signed computer arithmetic is the simplest and most efficient methodology followed. It simplifies subtraction between two binary numbers by modifying into the addition problem, which is convenient from a reconfigurable hardware implementation perspective and overflow handling. Negative numbers are represented with two's complement format by calculating one's complement/simply reverting the number, followed by adding one to LSB, which is a

**Table 2.3** Physical Design Parameters at CMOS 28 nm, VDD 0.9V, frequency 100 MHz

| Attributes  | $Area(\mu m^2)$ | $\mathrm{Power}(\mu W)$ | Slack(ns) |  |

|-------------|-----------------|-------------------------|-----------|--|

| FA          | 8.736           | 1.164                   | 1.87      |  |

| HADD [13]   | 7.392           | 0.649                   | 1.91      |  |

| SESA-1 [41] | 6.384           | 0.921                   | 1.93      |  |

| LOA [42]    | 4.032           | 0.567                   | 1.98      |  |

| AMA [40]    | AMA [40] 6.552  |                         | 1.93      |  |

| P1A         | 6.888           | 0.782                   | 1.93      |  |

two-cycle process. The effective computational resources required for the process are two-cycle latency and power consumption of N-bit adders, where the second cycle is just utilized for adding "1". P1A can be effectively used to reduce the design complexity and enhance the throughput for such operations in Edge-AI applications.

The differences between accurate and approximate computations have been measured with error metrics like MSE, NMED and MRED and reported in the table 2.2. It is also noteworthy that overall computational accuracy ain't much affected for 8-bit due to the introduction of P1A in LSB of HOAA and is reflected in overall better results. Hence, it can be concluded that the proposed HOAA can be a good choice for designing reconfigurable subtraction hardware.

## 2.2.2 Case-II: Rounding-to-even

In neural network computations, MAC units sum up the products of numbers, increasing precision. To support the limited precision requirement at Edge-AI, the numbers are often required to undergo quantization, resulting in rounding errors. Regular rounding accumulates the statistical bias due to long sequence operations in DNN, either in a positive direction or negative direction. Hence, the IEEE754-2008

roundTiesToEven technique is more suitable as rounding errors are canceled due to adding 1 when odd numbers are rounded down. However, the two-cycle process is more hardware-intensive due to the presence of shifters in two cycles, where one cycle is wasted simply for adding 1. This can be effectively optimized by introducing P1A, which results in the further reduction of computational resources. Our results from Table 2.2, 2.3 highlight the energy efficiency of the design with minimal accuracy loss, even less than 1% error.

### 2.2.3 Case-III: Configurable activation function

$$e^{Z} = \cosh(Z) + \sinh(Z)$$

$sigmoid(Z) = \frac{e^{Z}}{e^{Z} + 1}$

$$(2.6)$$

DNN inference models rely heavily on Non-linear AF to characterize input-output relationships. The hardware implementation methodologies for the implementation of reconfigurable activation functions are resource-intensive, and popular ones like sigmoid and tanh often require huge optimizations for Edge-AI applications. Iterative CORDIC-based methodology has been proven hardware resource-efficient yet affects critical delay. The runtime reconfigurable choice between sigmoid and tanh has been provided with AF-sel signal. The CORDIC approach involves the computation of hyperbolic sine (sinh(Z)) and cosine (cosh(Z)), requiring two-stage adders before division operation to derive the sigmoid function as shown in Eq. 2.6. Our HOAA approach could easily enhance throughput by minimizing adding 1. Furthermore, Table 2.3 discusses the impact of approximation introduced by P1A, which is negligible. Case III also demonstrates the scalability of our approach for fixed-point arithmetic, broadening P1A's applicability beyond the integer computations discussed earlier.

# Chapter 3

LPRE:Logarithmic Posit-enabled Reconfigurable edge-AI Engine Conventional edge-AI accelerators, based on systolic dataflow [25, 26], excel at convolutional operations but often suffer throughput loss for multi-layer perceptrons or recurrent neural network layers. Thus, reconfigurable accelerators [3,5,20] have been proposed, but these works are limited to fully connected layers. These architectures can be extended to convolutional layers with control engine and data flow modifications. It can benefit more from software-exploited sparsity than runtime pruning [30]. Sequential execution with time-multiplexed reconfigurable single-layer hardware enhances resource efficiency in resource-constrained environments in a resource-constrained environment, while hardware reuse (AF, POOL) [5,26] improves compute-density (TOPS/mm<sup>2</sup>).

As an example, VGG-16 requires substantial 15.5 billion MAC operations to process a single 224 X 224 image. Optimising resource distribution (e.g., dynamic channel pruning [18, 30]) significantly improves edge-AI systems to reduce MAC workloads without affecting accuracy. While fixed-point or logarithmic computations [2,3] are power/area-efficient for hardware implementations, reducing precision degrades output accuracy severely.

Logarithmic [22] and Posit [19,23] arithmetic present promising choices, delivering BF16/FP16-level accuracy at 8-bit and FP32 accuracy at 16-bits [1]. This reduction in data width also enables SIMD computation for enhancing the throughput [4]. The Logarithmic-Posit (LP) arithmetic unit [43] offers a formidable solution for on-device learning. Integrating a PQRE accelerator with RISC-V [29] or any general processor efficiently enhances hardware-software codesign [19] and improves existing edge-AI solutions.

The principal contributions of this work are as follows:

- Logarithmic Posit Quire Processing Engine (PQRE): The proposed PQRE utilises Posit arithmetic to reduce hardware resources without affecting computational accuracy. Furthermore, bit-width reduction and SIMD computations are applied, enhancing throughput by up to 4×.

- Time Multiplexed Reconfigurable edge-AI engine: This architecture

Figure 3.1 The detailed microarchitecture of 5-stage Logarithmic Posit Quire Processing Engine (PQRE).

improves compute efficiency and bandwidth by time-multiplexing the reconfigurable single-layer hardware and input-outputs by a factor of (N-1). It dynamically configures by layer to exploit sparsity and AF-reuse techniques, effectively enhancing the execution of N-layer MLPs in resource-constrained environments.

# 3.1 Proposed Design

The optimization of edge-AI accelerators often focuses on the design of the MAC unit. This work presents the Logarithmic Posit Quire Processing Engine designed to reduce hardware resources without compromising computational accuracy. The proposed LPRE utilizes the Posit number format, which is represented using sign, regime, exponent, and fraction, as follows:

$$-1^s \times 2^{e+k \times 2^{es}} \times (1.m), \tag{3.1}$$

where s is the sign bit, e is the exponent, k is the number of regime bits, es is the maximum exponent size, and m is the mantissa. The scaling factor  $(2^{e+k\times 2^{es}})$  ensures a wide dynamic range with dynamic scaling from the regime and exponent values. Furthermore, Quire accumulation can be applied during intermediate stages to ensure output precision with the Quire Size calculated as follows:

Quire

$$Size = 1 + cg + 2^{es} \times (n-2),$$

(3.2)

Figure 3.2 Proposed Logarithmic Posit-Enabled Reconfigurable edge-AI Engine architecture.

where cg are accumulation bits for preventing overflow.

Figure 3.1 depicts a 5-stage datapath designed to support 32-bit SIMD Quire MAC operations while allowing runtime switching between a single 32-bit operation, two 16-bit or four 8-bit parallel operations. The Posit arithmetic encode/decode logic block includes logic for dynamic exponent configuration with dynamic vector mode, supporting parallel computations in lower mode with output sign calculated via XOR of sign bits. The output of the preceding stage is sign-extended, while the leading zero counter (LZC) decodes the bit length of the regime. The multiply stage implements an adjustable parallel or iterative logarithmic multiplier based on overall area overhead. Run-time configurable precision and/or vectorization can be enabled with a variable Carry Propagate/Look-Ahead (CPLA) adder and configurable logarithmic barrel shifters for parallel accumulation.

The Quire Scale and Quire Accumulate stages align outputs from Quire-fixed-point format with vector shifter while preventing overflow due to accumulated bits (cg). The Normalise stage handles exception flags, converts Quire to unsigned values, and renormalizes output via zero/one counts (LZAC). The enhanced PQRE facilitates 4 X SIMD computations at reduced-bit width, following detailed previous work [4]. This allows more resources to be dynamically allocated for major parallel workloads, boosting application performance.

Our proposed PQRE improves accuracy loss from fixed-point-based accelerators [3, 5] without any additional area overhead. We incorporated our logarithmic-posit arithmetic-based PQRE into a layer-multiplexed accelerator and extended the work to support the convolutional layer using im2col software data rearrangement. The control engine dynamically allocates MAC units for a single reconfigurable layer based on data flow and can be configured at runtime based on the Neuron-count parameter. The other design parameters include the number of layers in the DNN model, image size  $(N \times M)$ , kernel size  $(k \times k)$ , stride, pooling type, etc. For instance, the first layer of LeNet-5 requires 576 MAC units for a single 5 X 5 kernel on a 28 X 28 image, followed by Max pooling.

The architecture efficiently manages the data flow through dedicated input and weight buffers, as shown in Figure 3.2. Workloads are mapped into a onedimensional PQRE array, and the input-multiplexing scheme maximizes bandwidth utilization while fetching the input-weight feature maps to on-chip memory via AXI. Enhanced throughput PQRE significantly reduces latency, with outputs serialised to a configurable AF. To reduce area overhead and support the variable needs of different AI workloads, we incorporated a CORDIC-based runtime-configurable ReLU/Sigmoid/Tanh activation function. The dual-path architecture, a Posit-to-Fixed-Point converter compatible with CORDIC-based FxP AF and Posit-based AF, allows dynamic execution per workload type. CORDIC-based fixed-point AFs are proven to be hardware efficient [6], while Posit AFs are less explored. We incorporated AF-reuse methodology within the reconfigurable layer to reduce the area overhead since most AI workloads characterize AF operations less frequently than MAC operations. This approach saves resources consumed by (N-1) layers and (N-1) activation functions within a layer compared to Systolic-based computations. This methodology also helps us achieve better tiling opportunities whenever necessary. For larger workloads, an iterative tiling mechanism triggers the execution of the next tile via the Compute\_Done signal. After completion of the FC/Conv layer, the Layer\_Done flag is generated, and after execution of all layers, DNN\_Done reports the completion of the AI workload to the master processor. Additionally, we explored

**Table 3.1** Comparison of FPGA Resource Utilization for proposed PQRE with SIMD FP MAC Unit [1] and SoTA MAC works [2–4]

| Data Type   | LUT  | Reg  | Op. Freq (MHz) |

|-------------|------|------|----------------|

| FP32        | 8065 | 1072 | 250            |

| Posit(32,2) | 6813 | 806  | 125            |

| BF16        | 3670 | 324  | 200            |

| FP16        | 2226 | 1062 | 357            |

| Posit(16,1) | 2083 | 528  | 230            |

| Int/FxP32   | 1356 | 208  | 153            |

| FP8         | 645  | 255  | 434            |

| Posit(8,0)  | 467  | 175  | 372            |

| Int/FxP16   | 326  | 32   | 345            |

| Int/FxP8    | 86   | 16   | 424            |

50% dynamic channel pruning [18] with modified dataflow to reduce MAC workloads by half and further enhance throughput. The overall architecture offers significant improvement over state-of-the-art works, particularly in resource-constrained edge AI accelerators, with reconfiguration, hardware reuse, and removal of redundant computations.

# 3.2 Methodology & Results

The critical requirements for edge-AI devices include quick event-triggered response, superior energy efficiency, and optimized compute density across diverse application scenarios. Key metrics, such as power consumption, latency, operating frequency, hardware utilisation, and accuracy, were evaluated to determine the efficiency of the proposed LPRE accelerator. The LPRE replaces conventional fixed-point or floating-point arithmetic-based processing engines with quantization-aware LP computations to validate the application accuracy and hardware performance at the edge node.

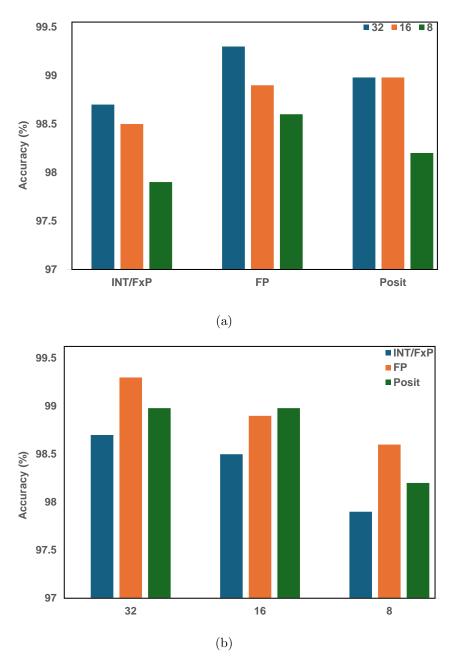

Inference accuracy for the proposed PQRE was compared with SoTA work [3]

**Figure 3.3** Inference accuracy evaluation with the proposed Logarithmic Posit Quire Processing Engine compared to the baseline FP [1] and SoTA INT/FxP [2,3] accuracy. (a) LeNet-5 on MNIST (b) AlexNet on CIFAR-10.

**Table 3.2** Hardware Utilization Report for Various Architectures with CORDIC-based FxP MAC and Our PQRE

| 8-bit precision      | Integer/Fixed-Point Arithmetic |               |                   | RAMAN       | Pruning       | Posit Arithmetic |              |       |

|----------------------|--------------------------------|---------------|-------------------|-------------|---------------|------------------|--------------|-------|

| Arch. Type DNN-Layer | DNN-Fully                      | FC Reused [2] | Reconfig-         | Sparse-     | DNN-Layer     | DNN- Fully       | Proposed     |       |

| Arch. Type           | Reused [3]                     | Parallel [5]  | Layer-Multiplexed | Sparse [25] | Systolic [30] | Reused [3]       | Parallel [5] | Work  |

| LUT                  | 112654                         | 207908        | 19834             | 37200       | 40780         | 139561           | 261703       | 17539 |

| FF                   | 113648                         | 306874        | 12081             | 8600        | 45250         | 163231           | 316406       | 14827 |

| BRAM                 | 32                             | 53            | 13                | 61          | 257           | 24               | 57           | 16    |

| Power (W)            | 1.097                          | 4.07          | 0.78              | 0.137       | 1.4           | 1.05             | 2.08         | 0.93  |

and Tensorflow-based models [2] across 8/16/32 bit-precision using LeNet-5 on the MNIST dataset and AlexNet on the CIFAR-10 dataset, as depicted in Figure 3.3(a). The proposed PQRE achieves minimal accuracy loss at 8-bit and no accuracy loss at 16-bit compared to the FP32 baseline, demonstrating better adaptability for edge-AI applications with improved hardware efficiency. Posit arithmetic also significantly improves accuracy for larger networks, such as VGG-16, ResNet-18, and Inception-v3 [23]. Thus, further evaluations were not conducted in this work.

We implemented the PQRE, configurable AF and LPRE design on a Xilinx Virtex-7 FPGA Board to further analyse performance. SoTA designs were also re-implemented on the same board to maintain similar parameters for a fair comparison. The performance parameters include the LUTs and FFs of the FPGA board, showcasing the resources used while operating frequency is evaluated with a focus on the response time of the edge application. The resource utilization for the proposed PQRE and SoTA MAC architectures are presented in Table 3.1. Similar evaluations for activation functions are compared with [5,6] as presented in Table 3.3. The results show a substantial reduction in hardware resources, as compared to SoTA works [2,3,25], with enhanced throughput (4 X at 8-bit, 2 X at 16-bit). The Posit-to-Int/FxP conversion utilises 325 LUTs and 300 LUTs for Int/FxP-to-Posit conversion. Thus, the area overhead showcasing the Posit activation function seems an easier and more viable way. These outcomes showcase runtime-reconfigurability and enhanced compute efficiency of the proposed PQRE across different precisions. To ensure a fair comparison, We re-implemented the state-of-the-art fully parallel architecture [5], DNN-layer reused architecture [3], and proposed architecture with fixed-precision based QuantMAC [2] and Posit-arithmetic-based PQRE. Figure 3.2 depicts the

**Table 3.3** Comparison of FPGA Resource Utilization in Different Precision and Datatype [3,5,6] with Proposed Posit AF

| AF          | Sigmoid |       |        | Tanh |       |        |  |

|-------------|---------|-------|--------|------|-------|--------|--|

| Precision   | LUT     | Freq  | Power  | LUT  | Freq  | Power  |  |

|             |         | (MHz) | (W)    |      | (MHz) | (W)    |  |

| FP32        | 5101    | 9.12  | 0.121  | 4298 | 17.64 | 0.13   |  |

| FP16        | 1853    | 16.45 | 0.118  | 1530 | 29.3  | 0.124  |  |

| BF16        | 1856    | 22.39 | 0.083  | 1513 | 26.35 | 0.083  |  |

| TF32        | 2436    | 16.16 | 0.117  | 1990 | 23.6  | 0.118  |  |

| FxP8        | 156     | 262   | 0.0395 | 156  | 262   | 0.0395 |  |

| FxP16       | 267     | 238   | 0.0483 | 267  | 238   | 0.0483 |  |

| FxP32       | 478     | 154   | 0.0649 | 478  | 154   | 0.0649 |  |

| Posit(16,1) | 2275    | 16.38 | 0.098  | 1879 | 26.27 | 0.089  |  |

| Posit(8,0)  | 1468    | 21.4  | 0.089  | 1548 | 29.8  | 0.078  |  |

LeNet-5 hardware architecture to demonstrate the proposed approach on a working FPGA prototype. The proposed architecture was implemented with 64 PQREs and a runtime reconfigurable control engine supporting LeNet-5 execution. The LPRE utilised approximately 50% of the resources required by SoTA-works [25, 30] and 80% less than [3, 5].

The design does not incur much power overhead compared to SoTA-works [5,30], maintaining similar battery life for edge devices. The proposed accelerator achieves an inference time of 184 mili-seconds (42.3 GOPS), compared to 772 mili-seconds (4.95 GOPS) for DNN-Layer reused architecture [3] on Xilinx Virtex-7 FPGA Board and 226 mili-seconds (34.38 GOPS) on Jetson Nano at 8-bit precision with an accuracy of 95%. Thus providing an efficient trade-off between available hardware resources and throughput latency. The detailed modeling for computation time (in

#clock cycles) for DNN execution using SoTA architecture (L\_P) [5] and proposed architecture (L\_R) can be expressed with:

$$Latency\_parallel(L\_P) = \sum_{k=1}^{L-1} m(k) + L - 1$$

(3.3)

$$Latency\_proposed(L\_R) = \sum_{k=1}^{L} m(k) + 2L - 3, \qquad (3.4)$$

where L refers to the total layers of the DNN model, and m(k) is the count of PQRE utilised in the  $k^{th}$  layer. This is crucial for understanding the application inference time at edge nodes.

Overall, the LPRE consumes similar power while offering a trade-off in bandwidth and resource utilization, highlighting the efficiency of accuracy-critical IoT devices. Our design, adapted for vehicle number plate detection (facilitating automated gate control), showcases performance improvement compared to FP and Int/FxP precision-based edge-AI accelerators. This justifies our solution as better suited for resource-constrained edge-AI applications than SoTA works.

# Chapter 4

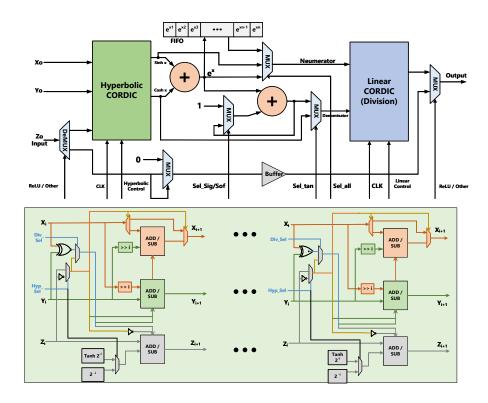

# CORDIC is All You Need

Enhancing the efficiency of hardware accelerators involves several techniques to increase throughput while minimizing power usage and latency. These techniques include Quantization, Pruning, Sparsity, Power and Clock Gating. Quantization entails lowering the precision of data from a higher to a lower bit-width, which helps reduce the size of adders and multipliers in both weights and inputs, ultimately decreasing delay and power consumption. This process employs methods such as Truncation and Round-to-earest-even, although such methods can compromise precision, resulting in diminished accuracy on a larger scale. Research on eliminating quantizing errors is available in sources like [44, 45]. Pruning entails minimizing computational data according to its significance, a method utilized by NVIDIA in their GPUs to enhance throughput [46–48]. Adjusting lower-valued inputs or weights to zero based on the pruning ratio effectively reduces computational requirements. Pruning coordinates with Sparsity, which converts data matrices into sparse formats by removing zeros. Although pruning can affect accuracy, it can be recovered through model fine-tuning, possibly doubling throughput gains. Some of the Latest design also Performs a Hierarchical pruning-sparsity increasing the ratio up to 3:4 reducing the 75% computation [49]. Sparsity, while complicating data flow, minimizes redundant calculations. At a more fundamental level, Power and Clock Gating are used to conserve energy by disabling power to unused logic blocks; in power gating, a transistor is placed on the power nets to effectively act as an enable pin. Clock gating reduces switching power loss by controlling the clock's frequency to certain devices. These strategies are integral to the Physical Design process during ASIC Chip Fabrication. Though in these optimization techniques, some are applicable at PE whereas some are applicable and more optimal in architecture design.

The proliferation of edge devices—from smart sensors, including intelligent cameras and soil quality sensors, to autonomous vehicles and data mining—necessitates efficient AI accelerators capable of handling complex computations. These Edge-AI Accelerators are vital for enabling real-time decision-making while minimizing latency, curbing bandwidth demands, and upholding data privacy. Contrary to cloud-based AI, edge computing reduces dependency on external servers, thereby becoming

crucial for applications with stringent latency or privacy requirements. Advances in AI and computation accelerators have been significant, particularly in systolic arrays, CORDIC processors, and neural network hardware accelerators. Data flow optimization techniques, such as data reuse and row-wise weight or output stationary flows, enhance throughput and lower computational demands. Enhanced Control Engine (CE) designs, along with design-level improvements in PE, have contributed significantly. SOTA hardware accelerators and high-performance computing (HPC) emphasize performance, albeit with substantial area and power costs, thus favouring cloud environments.