## Design Optimization of pMOS only eDRAM Macro Cell at 28 nm Node

#### M.Tech. Thesis

### By ABU SAID PARVEJ ALAM

## DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE

May 2025

## Design Optimization of pMOS only eDRAM Macro Cell at 28 nm Node

#### **A THESIS**

Submitted in partial fulfillment of the requirements for the award of the degree of

Master of Technology

ABU SAID PARVEJ ALAM

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE May 2025

#### INDIAN INSTITUTE OF TECHNOLOGY INDORE

#### CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the thesis entitled **Design Optimization of pMOS only eDRAM Macro Cell at 28 nm Node** in the partial fulfillment of the requirements for the award of the degree of **MASTER OF TECHNOLOGY** and submitted in the **DEPARTMENT OF ELECTRICAL ENGINEERING, Indian Institute of Technology Indore**, is an authentic record of my own work carried out during the time period from July 2024 to May 2025. Thesis submission under the supervision of Prof. Abhinav Kranti, IIT Indore.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other institute.

Signature of the student with date (ABU SAID PARVEJ ALAM)

-----

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

22/05/2025 Signature of the Supervisor of

M.Tech. thesis (with date)

(Prof. Abhinav Kranti)

ABU SAID PARVEJ ALAM has successfully given his M.Tech. Oral Examination held on May 5, 2025.

signature of Supervisor of M.Tech. thesis

Date: 22/05/2025

Convener, DPGC Date: 22-05-2025

Saptarshi Ghosh

.....

#### **ACKNOWLEDGEMENTS**

First and foremost, I would want to sincerely thank Prof. Abhinav Kranti, my project supervisor, for the guidance and encouragement during the M.Tech. thesis research work. His motivation and mentorship played a crucial role in the successful completion of my M.Tech. project.

I am deeply grateful to IIT Indore for providing the necessary infrastructure and research environment to carry out this work. I also thank the Department of Electrical Engineering, IIT Indore. I am grateful to the Ministry of Education, Government of India, and IIT Indore for financial support in the form of stipend during my M.Tech. program.

I would like to thank Dr. Manish Gupta, BITS Pilani, K.K. Birla Goa Campus, for allowing access to the TCAD simulation tools. I am especially thankful to my senior, Mr. Rohit Kumar Nirala, for his continuous support, guidance, and assistance in the laboratory. I also appreciate the help and support provided by Mr. Aman Chandrakar during this work.

I express my heartfelt gratitude to my parents, Mr. Oliul Islam Mandal and Mrs. Firoja Bibi, for their unconditional love and support. I also want to thank my fellow classmates for their support, friendship, and the priceless memories we made together while we were in Indore.

Abu Said Parvej Alam

Dedicated to my family

#### **Abstract**

### Design Optimization of pMOS only eDRAM Macro Cell at 28 nm Node

Embedded DRAM (eDRAM) architectures have been driven by growing need for energy-efficient and high-density memory. The 2-Transistor 0 Capacitor (2T0C) Gain Cell (GC) appears as compact logic-compatible substitute for traditional 1T1C DRAMs. However, a main drawback of the 2T0C GC is its low Data Retention Time (DRT), which is primarily degraded due to capacitive coupling and leakage currents at advanced technology nodes.

This thesis explores an effective approach to enhance DRT by using Double Gate (DG) topology with 2T pMOS-only GC structure at the 28 nm technology node. DG transistors offer better electrostatic control over the channel, boost driving current and reduced leakage current, and tunable threshold voltages through independent gate operation, all of which are crucial for GC. Important contribution of this thesis includes a two-step DRT enhancement approach. First, minimizing capacitive coupling by independent gate bias operation to allow a larger voltage difference ( $\Delta V$ ) between to logic levels. Second, suppressing leakage by write bit line (WBL) bias tuning to significantly lower the data degradation rate. The thesis work also analyses the effects of high temperature operation and supply voltage downscaling on DRT.

#### **Table of Contents**

| TITLE PAGE        | I   |

|-------------------|-----|

| DECLARATION PAGE  | II  |

| ACKNOWLEDGEMENT   | III |

| DEDICATION PAGE   | IV  |

| ABSTRACT          | V   |

| TABLE OF CONTENTS | VI  |

| LIST OF FIGURES   | X   |

| LIST OF TABLES    | XIV |

| NOMENCLATURE      | XV  |

| ACRONYMS          | XVI |

#### **Contents**

| Chapto | er 1  | Introduction                                           | 1    |

|--------|-------|--------------------------------------------------------|------|

| 1.1    | Ove   | erview of Memory                                       | 1    |

| 1.1    | 1.1   | Static Random-Access Memory (SRAM)                     | 2    |

| 1.1    | 1.2   | Dynamic Random-Access Memory (DRAM)                    | 3    |

| 1.1    | 1.3   | Gain Cell Embedded DRAM (GC-eDRAM)                     | 4    |

| 1.2    | Eva   | duation of Gain Cells (GCs)                            | 5    |

| 1.3    | Dif   | ferent Types of GC Topology                            | 8    |

| 1.3    | 3.1   | 2T Gain Cell                                           | 8    |

| 1.3    | 3.2   | 3T Gain Cell                                           | 9    |

| 1.3    | 3.3   | 4T Gain Cell                                           | . 10 |

| 1.3    | 3.4   | 5T Gain Cell                                           | . 11 |

| 1.4    | Fea   | tures and Applications of Gain Cells                   | . 12 |

| 1.5    | Mo    | tivation for 2T pMOS-only GC                           | . 14 |

| 1.6    | Cor   | nclusion                                               | . 15 |

| 1.7    | Org   | ganization of The Thesis                               | . 16 |

| Chapto | er 2  | Operation of 2T0C DRAM                                 | 17   |

| 2.1    | Wo    | rking of Gain Cell                                     | 17   |

| 2.1    | 1.1   | Write Operation                                        | 18   |

| 2.1    | 1.2   | Hold Operation                                         | . 19 |

| 2.1    | 1.3   | Read Operation                                         | . 20 |

| 2.2    | Dat   | a Retention Time (DRT)                                 | 20   |

| 2.2    | 2.1   | Importance of DRT                                      | 22   |

| 2.2    | 2.2   | Method to estimate DRT                                 | . 23 |

|        | 2.2.2 | .1 Method 1 - Threshold Voltage of Read Transistor (MR | 23   |

|        | 2.2.2 | .2 Method 2 - 200 mV Differential Method               | . 24 |

| 2.     | 2.3   | Improving DRT                                          | . 26 |

| 2.3    | Cor   | nclusion                                               | 28   |

| Chapt | ter 3 | Double Gate based 2T pMOS-only GC                                | 29    |

|-------|-------|------------------------------------------------------------------|-------|

| 3.1   | Do    | uble Gate (DG) p-type MOSFET                                     | 29    |

| 3.2   | Do    | uble Gate 2T pMOS-only Gain Cell                                 | 33    |

| 3.    | 2.1   | Introduction to DG 2T pMOS-only GC                               | 33    |

| 3.    | 2.2   | Working of DG 2T pMOS-only GC                                    | 34    |

|       | 3.2.2 | .1 Write Operation                                               | 34    |

|       | 3.2.2 | .2 Hold Operation                                                | 36    |

|       | 3.2.2 | .3 Read Operation                                                | 37    |

|       | 3.2.2 | .4 Timing Diagram                                                | 38    |

| 3.    | 2.3   | Capacitive Coupling (CC)                                         | 39    |

| 3.3   | Ap    | proach to Enhance DRT                                            | 43    |

| 3.    | 3.1   | Motivation                                                       | 43    |

| 3.    | 3.2   | Two-Step Approach to Enhance DRT                                 | 44    |

|       | 3.3.2 | .1 Step 1 - Maximize the voltage difference (ΔV)                 | 44    |

|       | 3.3.2 | .2 Step 2 - Lowering the data degradation slope ( $dV_{SN}/dt$ ) | ). 45 |

| 3.4   | Enl   | nancing DRT – Bias optimization                                  | 46    |

| 3.    | 4.1   | Optimizing WWL node bias                                         | 46    |

| 3.    | 4.2   | Optimizing WBL node bias                                         | 51    |

| 3.    | 4.3   | Optimizing RWL and RBL node biases                               | 54    |

| 3.5   | Ber   | nchmarking                                                       | 54    |

| 3.6   | Coı   | nclusion                                                         | 55    |

| Chapt | ter 4 | Impact of Supply Voltage and Temperature                         | 57    |

| 4.1   | Imp   | oact of V <sub>DD</sub> scaling on DRT                           | 57    |

| 4.2   | Imp   | pact of higher temperature on DRT                                | 60    |

| 4.3   | Imp   | pact of V <sub>DD</sub> scaling at 358 K                         | 63    |

| 4.4   | Coi   | nclusion                                                         | 64    |

| Chapt | ter 5 | Conclusion and Future Work                                       | 65    |

| 5.1   | Coı   | nclusion                                                         | 65    |

| 5.2   | Fut   | ure Work                                                         | 66    |

| References | 6 | <b>)</b> | 7 |  |

|------------|---|----------|---|--|

|------------|---|----------|---|--|

#### **List of Figures**

| Figure Title |                                                                                                                                           | Page No |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| No.          |                                                                                                                                           |         |  |

| Fig. 1.1     | Schematic diagram of a 6T SRAM bitcell.                                                                                                   | 2       |  |

| Fig. 1.2     | Schematic diagram of a 1T1C DRAM bitcell.                                                                                                 | 3       |  |

| Fig. 1.3     | Basic configuration of GC-eDRAM macrocell.                                                                                                | 4       |  |

| Fig. 1.4     | Schematic diagram of a 2T0C DRAM macrocell.                                                                                               | 6       |  |

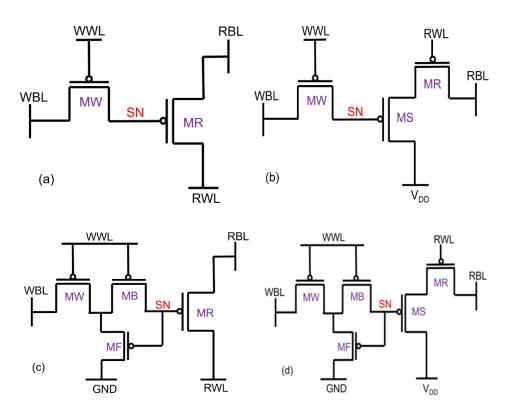

| Fig. 1.5     | Schematic representation of (a) 2T Gain Cell, (b) 3T Gain Cell, (c) 4T Gain Cell, and (d) 5T Gain Cell.                                   | 7       |  |

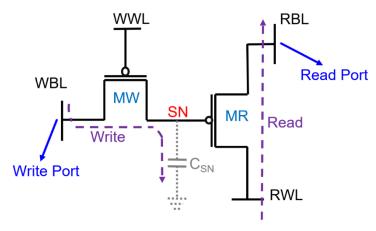

| Fig. 1.6     | Schematic representation of 2T GC showing write and read port.                                                                            | 12      |  |

| Fig. 1.7     | Overview of 2T gain implementation options: (a) All pMOS Cell, (b) Mixed pMOS-nMOS Cell, (c) Mixed nMOS-pMOS Cell, and (d) All nMOS Cell. | 14      |  |

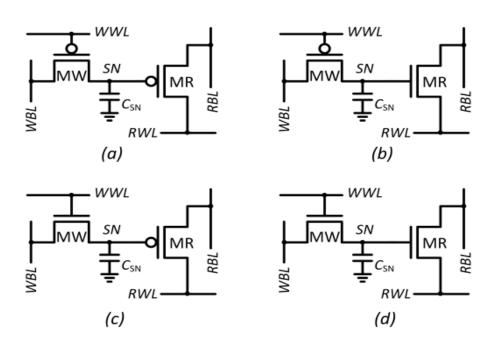

| Fig. 2.1     | Two transistor gain cell implementation options including the schematic waveforms.                                                        | 18      |  |

| Fig. 2.2     | Three types of leakages that can destroy stored data in a conventional 2T gain cell.                                                      | 21      |  |

| Fig. 2.3     | Storage node voltage $(V_{SN})$ degradation of 2T GC after write operation.                                                               | 22      |  |

| Fig. 2.4        | Storage node voltage (V <sub>SN</sub> ) degradation | 23 |

|-----------------|-----------------------------------------------------|----|

|                 | of an arbitrary pMOS-only GC after write            |    |

|                 | operation and DRT estimation using 1st              |    |

|                 | method.                                             |    |

| Fig. 2.5        | Storage node voltage $(V_{SN})$ degradation         | 25 |

|                 | of an arbitrary pMOS-only GC after write            |    |

|                 | operation and DRT estimation using 2nd              |    |

|                 | method.                                             |    |

| <b>Fig. 2.6</b> | Impact of leakage and capacitive coupling           | 26 |

|                 | on storage node voltage $(V_{SN})$                  |    |

|                 | degradation.                                        |    |

| Fig. 2.7        | Reported DRT values of Si GC-eDRAM                  | 27 |

|                 | at different technology nodes.                      |    |

| Fig. 3.1        | Schematic diagram of a DG-MOSFET.                   | 29 |

| Fig. 3.2        | Transfer characteristics of DG-pMOS.                | 31 |

| Fig. 3.3        | Schematic representation of double gate             | 33 |

|                 | 2T pMOS only gain cell.                             |    |

| Fig. 3.4        | Schematic representation of DG 2T                   | 34 |

|                 | pMOS-only GC showing write and read                 |    |

|                 | paths.                                              |    |

| Fig. 3.5        | Bias representation of DG 2T pMOS-only              | 35 |

|                 | GC during write operation.                          |    |

| <b>Fig. 3.6</b> | Bias representation of DG 2T pMOS-only              | 36 |

|                 | GC during hold operation.                           |    |

| <b>Fig. 3.7</b> | Bias representation of DG 2T pMOS-only              | 37 |

|                 | GC during read operation.                           |    |

| Fig. 3.8        | Timing diagrams demonstrating DG 2T                 | 38 |

|                 | pMOS-only GC operations.                            |    |

| <b>Fig. 3.9</b> | Impact of capacitive coupling (CC) on               | 39 |

|                 | storage node voltage $(V_{SN})$ at the              |    |

|                 | beginning of hold state.                            |    |

| Fig. 3.10 | Schematic of a 2T GC with the coupling                   | 40 |

|-----------|----------------------------------------------------------|----|

|           | capacitances between SN, WWL, RBL,                       |    |

|           | and RWL.                                                 |    |

| Fig. 3.11 | Impact of capacitive coupling on storage                 | 41 |

|           | node voltage during transitions of control               |    |

|           | node biases.                                             |    |

| Fig. 3.12 | Timing diagrams demonstrating                            | 42 |

|           | capacitive coupling in 2T GC.                            |    |

| Fig. 3.13 | Reported DRT values of 2T GC eDRAM                       | 43 |

|           | at different technology nodes.                           |    |

| Fig. 3.14 | Approach to enhance DRT - (a) a typical                  | 45 |

|           | $V_{\text{SN}}$ degradation with lower voltage           |    |

|           | difference ( $\Delta V$ ), (b) $V_{SN}$ degradation with |    |

|           | increased voltage difference ( $\Delta V$ ), (c) a       |    |

|           | pre-optimized $V_{\text{SN}}$ degradation with           |    |

|           | higher slope, and (d) an optimized $V_{SN}$              |    |

|           | degradation plot having reduced                          |    |

|           | degradation slope along with increased                   |    |

|           | voltage difference ( $\Delta V$ ).                       |    |

| Fig. 3.15 | Impact of back gate bias $(V_{BG})$ on                   | 47 |

|           | threshold voltage $(V_{Th})$ .                           |    |

| Fig. 3.16 | Pre optimized $V_{SN}$ degradation of DG 2T              | 48 |

|           | pMOS-only GC following write                             |    |

|           | operation.                                               |    |

| Fig. 3.17 | Schematic of a DG 2T pMOS-only GC                        | 49 |

|           | with the coupling capacitances between                   |    |

|           | $SN$ , $WWL_1$ , $WWL_2$ , $RBL$ , and $RWL$ .           |    |

| Fig. 3.18 | $V_{SN}$ degradation with optimized WWL                  | 50 |

|           | node bias.                                               |    |

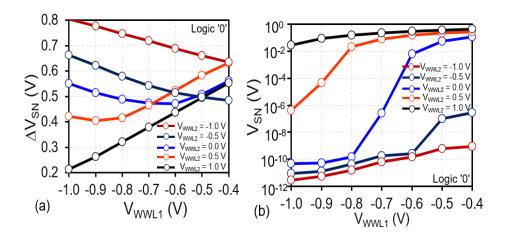

| Fig. 3.19 | (a) Change in storage node voltage at the 50        |    |  |

|-----------|-----------------------------------------------------|----|--|

|           | beginning of hold operation under                   |    |  |

|           | different bias, and (b) Written voltage             |    |  |

|           | level for logic '0' on storage node under           |    |  |

|           | different bias conditions.                          |    |  |

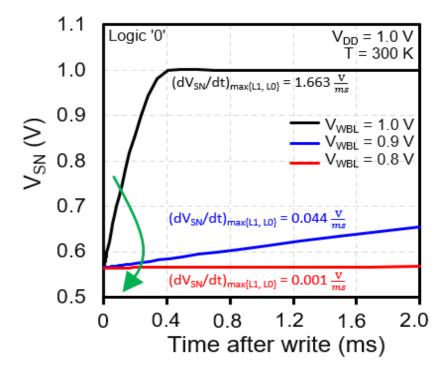

| Fig. 3.20 | V <sub>SN</sub> degradation of logic '0' with three | 52 |  |

|           | fixed WBL node bias.                                |    |  |

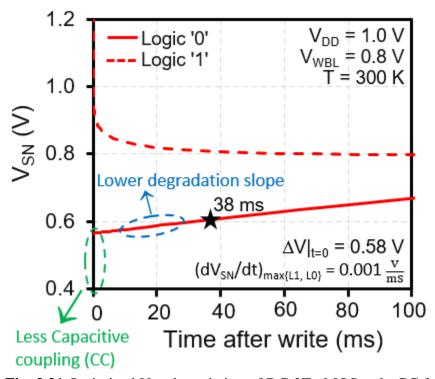

| Fig. 3.21 | Optimized $V_{SN}$ degradation of DG 2T             | 53 |  |

|           | pMOS-only GC following write                        |    |  |

|           | operation.                                          |    |  |

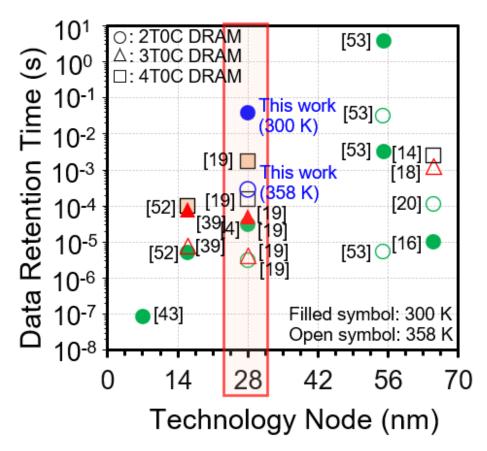

| Fig. 3.22 | Benchmarking of reported Si GC-                     | 55 |  |

|           | eDRAM at different technology nodes.                |    |  |

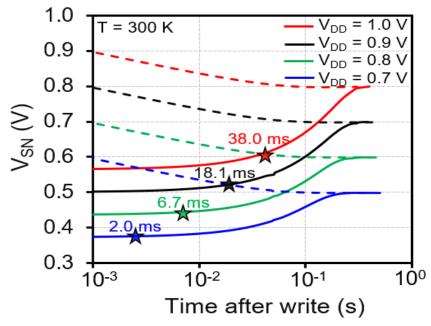

| Fig. 4.1  | $V_{SN}$ degradation at four different supply       | 58 |  |

|           | voltages at 300 K.                                  |    |  |

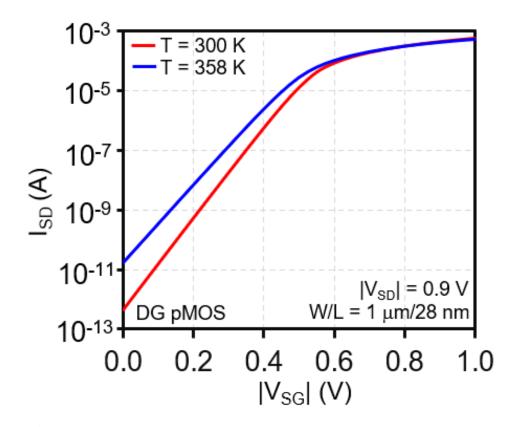

| Fig. 4.2  | Transfer characteristics of DG pMOS at              | 60 |  |

|           | different temperatures.                             |    |  |

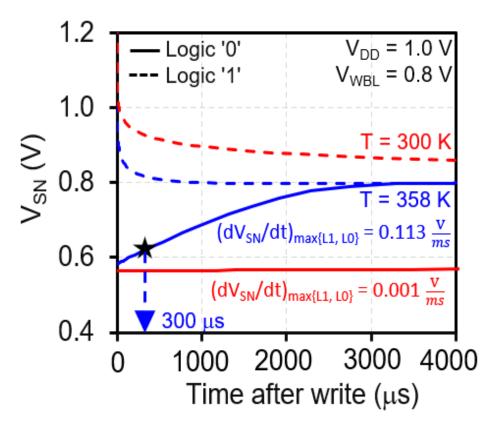

| Fig. 4.3  | Optimized $V_{SN}$ degradation of DG 2T             | 61 |  |

|           | pMOS-only GC at two different                       |    |  |

|           | temperatures.                                       |    |  |

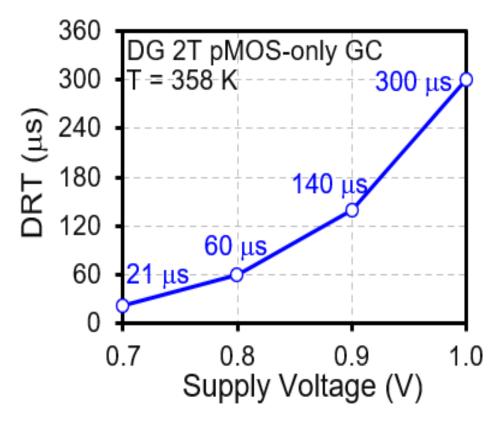

| Fig. 4.4  | Impact of supply voltage scaling on DRT             | 63 |  |

|           | at 358 K.                                           |    |  |

#### **List of Tables**

| Table     | Table Title                                                     | Page No. |

|-----------|-----------------------------------------------------------------|----------|

| No.       |                                                                 |          |

| Table 1.1 | Comparison of SRAM, DRAM and GC-eDRAM.                          | 5        |

| Table 1.2 | Comparison of different types of GC topology                    | 11       |

| Table 3.1 | Dimensions of DG-pMOS used in this work.                        | 30       |

| Table 4.1 | Impact of supply voltage ( $V_{DD}$ ) scaling on DRT at 300 K.  | 59       |

| Table 4.2 | Impact of higher temperature on DRT at $V_{DD} = 1 \text{ V}$ . | 62       |

#### **NOMENCLATURE**

| Notation   | Description                                 | Unit       |

|------------|---------------------------------------------|------------|

| L          | Gate length                                 | nm         |

| W          | Width                                       | nm         |

| $T_{OX}$   | Oxide thickness                             | nm         |

| $T_{Si}$   | Silicon thickness                           | nm         |

| $V_G$      | Gate voltage                                | V          |

| $V_{BG}$   | Back gate voltage                           | V          |

| $V_D$      | Drain voltage                               | V          |

| $V_S$      | Source voltage                              | V          |

| $V_{DD}$   | Supply voltage                              | V          |

| $I_{ON}$   | On current                                  | mA         |

| $I_{OFF}$  | Off current                                 | nA         |

| $I_{SD}$   | Source to drain current                     | A          |

| $V_{SD}$   | Source to drain voltage                     | V          |

| $V_{SG}$   | Source to gate voltage                      | V          |

| $V_{GS}$   | Gate to source voltage                      | V          |

| $V_{DS}$   | Drain to source voltage                     | V          |

| $V_{Th}$   | Threshold voltage                           | V          |

| $V_{WWL}$  | Write word line voltage                     | V          |

| $V_{WWL1}$ | Write word line-1 voltage                   | V          |

| $V_{WWL2}$ | Write word line-2 voltage                   | V          |

| $V_{WBL}$  | Write bit line voltage                      | V          |

| $V_{SN}$   | Storage node voltage                        | V          |

| $V_{RBL}$  | Read bit line voltage                       | V          |

| $V_{RWL}$  | Read word line voltage                      | V          |

| $V_{RWL2}$ | Read word line-2 voltage                    | V          |

| $\mu_p$    | Hole mobility                               | $cm^2/V.s$ |

| $\Delta V$ | Voltage difference between two logic levels | V          |

| $\Delta V_{SN}$   | Change in storage node voltage      |    |

|-------------------|-------------------------------------|----|

| $\Delta V_{WWLI}$ | Change in write word line-1 voltage | V  |

| $\Delta V_{WWL2}$ | Change in write word line-2 voltage | V  |

| RAT               | Read access time                    | ns |

| P                 | Power                               | W  |

#### **ACRONYMS**

1T1C One transistor and one capacitor

2T Two transistor

2TOC Two transistor and zero capacitor

3T Three transistor

3TOC Three transistor and zero capacitor

4T Four transistor

4TOC Four transistor and zero capacitor

5T Five transistor6T Six transistor

8T Eight transistor

10T Ten transistor

AI Artificial Intelligence

CC Capacitive Coupling

CIM Compute-in-memory

CMOS Complementary Metal Oxide Semiconductor

CPU Central Processing Unit

DG-MOSFET Double Gate Metal Oxide Semiconductor

Field Effect Transistor

DG-pMOS Double gate p-type MOS

DRAM Dynamic Random-Access Memory

DRT Data Retention Time

eDRAM Embedded DRAM

FDSOI Fully Depleted SOI

GC Gain Cell

GC-eDRAM Gain Cell Embedded DRAM

GPU Graphics Processing Unit

IoT Internet-of-Things

ML Machine Learning

MOS Metal Oxide Semiconductor

MOSCAP MOS Capacitor

MOSFET Metal Oxide Semiconductor Field

Effect Transistor

MR Read Transistor

MW Write Transistor

nMOS n-type MOS

pMOS p-type MOS

PC Personal Computer

PCB Printed Circuit Board

PUF Physical Unclonable Function

RBL Read Bit Line

RWL Read Word Line

Si Silicon

SN Storage Node

SOI Silicon on Insulator

SoC System-on-Chip

SRAM Static Random-Access Memory

WBL Write Bit Line

WWL Write Word Line

WWL<sub>1</sub> Write Word Line-1

WWL<sub>2</sub> Write Word Line-2

#### Chapter 1

#### Introduction

Semiconductor memory is regarded as the central component of any digital system in the world. Every electronic device, from personal computers to smartphones, from artificial intelligence processors to tiny gadgets or Internet-of-Things (IoT) sensors, requires some kind of memory to store data. The features of memory impact the overall system performance, like speed, area, power consumption and even cost [1]. Semiconductor memories are designed for fast access by Central Processing Units (CPUs) to hold binary data and instructions so that processors can access them quickly. Specifically, embedded memories become an essential component of designs for System-on-Chip (SoC) [2]. As technology progresses, the need for denser, faster, and power-efficient memory devices has grown exponentially. These demands have driven innovations in Static Random-Access Memory (SRAM), Dynamic Random-Access Memory (DRAM) and Gain Cell embedded DRAM (GC-eDRAM) memory architectures [3].

#### 1.1 Overview of Memory

Memory can be broadly classified into two primary groups: non-volatile and volatile memory [4]. Whereas non-volatile memories store information regardless of power, volatile memories destroy their retained data once the supply is removed. SRAM and DRAM are the two main forms of volatile memories [5].

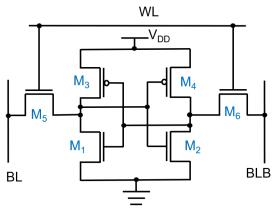

Fig. 1.1 Schematic diagram of a 6T SRAM bitcell [6].

#### 1.1.1 Static Random-Access Memory (SRAM)

Over time, several memory technologies have been developed, each with unique benefits and drawbacks. One of the most used forms is SRAM, where data is stored in a bistable flip-flop circuit [6]. SRAM typically stores a single bit of information using six transistors (6T). A standard SRAM cell architecture consists of two access transistors and two cross-coupled inverters (Fig. 1.1). This configuration ensures that the kept data remains intact as long as power is accessible, without needing any periodic refresh operations. The benefits of SRAM include very quick read and write operations, great stability and reliability, and low dynamic power consumption during access. These qualities make SRAM a popular choice for small buffers, high-speed registers, and CPU cache memories. SRAM is still remained essential for applications requiring very quick access and minimal latency, like the L1 and L2 cache memories in modern microprocessors [6]. However, SRAM uses more area. Hence, memory density is reduced. Furthermore, SRAM is less suitable for very large memories (main memories) since leakage currents cause it to consume considerable static power, particularly in advanced technology nodes such as 28 nm or below [7]. Another challenge of 6T SRAM is the difficulty in scaling cells at lower supply voltages (V<sub>DD</sub>). The noise margins get reduced, which makes SRAM cells more vulnerable to failure due to V<sub>DD</sub> fluctuations [4]. In order to guarantee dependable subthreshold (sub-V<sub>Th</sub>)

operation, alternative SRAM cells with 8, 10, or even up to 14 transistors are necessary [8].

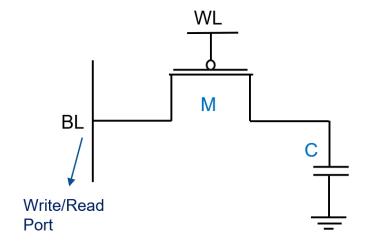

Fig. 1.2 Schematic diagram of a 1T1C DRAM bitcell [9].

#### 1.1.2 Dynamic Random-Access Memory (DRAM)

Another common type is DRAM, which keeps each piece of information using one transistor and one capacitor (1T1C) [9]. Fig. 1.2 shows a schematic diagram of a 1T1C DRAM bitcell. The fundamental idea behind DRAM is very simple: charge either present or absent on the capacitor marks a binary '1' or '0', respectively. The biggest benefit of DRAM is its high density. Only one transistor and one capacitor allow DRAM for the formation of vast memory arrays. Because of this, DRAM is the recommended option for main memory (RAM) in servers, graphics cards, and Personal Computers (PCs) [5]. However, DRAM suffers from a leakage problem. Even if the device is kept powered on, the charge that is stored on the capacitor eventually tends to leak out. Because of this, DRAM cells need to be refreshed on a regular basis in order to recover lost charge and preserve data integrity. As a result, periodic refreshing increases energy consumption and complicates the memory controller [10].

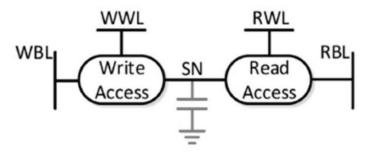

Fig. 1.3 Basic configuration of GC-eDRAM macrocell [11].

#### 1.1.3 Gain Cell Embedded DRAM (GC-eDRAM)

As computers became more powerful and needed to handle larger amounts of data quickly, embedded DRAM (eDRAM) [5] was introduced to combine the advantages of DRAM (high density) with better integration in logic processes. Larger memory embedded straight on the logic process chip, such as CPUs or Graphics Processing Units (GPUs), always benefits rather than depending on outside main memory. The main reasons for this are: (1) higher system-level integration densities are facilitated by embedded memory, and (2) going off-chip connectivity via capacitive lines and input/output (I/O) terminals on printed circuit boards (PCBs) differs from on-chip connections and demands more power consumption [12]. Two forms of eDRAM are examined: (1) traditional 1T1C eDRAM, where a single access transistor and a unique, high-density, 3D capacitor (trench or stack capacitor) builds a macrocell [9], and (2) GC-eDRAM, whose macrocell is built from 2 to 5 MOSFETs [13], [14]. Fig. 1.3 shows the basic configuration of the GC-eDRAM bitcell. Traditional 1T1C eDRAM processes are not completely compatible with logic complementary metaloxide-semiconductor (CMOS) technologies as it requires a special fabrication process to create a dense trench or stacked capacitors on chip [9], for which manufacturing becomes complex and costly. An alternative, GC-eDRAMs are thus completely logic compatible and readily implemented into SoCs with no additional price. GC-eDRAMs promise a good balance between storage density and speed, which makes it a lowpower alternative to SRAM [15], [16], [17], [18], [19], [20]. The following table summarises the key differences:

**Table 1.1** Comparison of SRAM, DRAM and GC-eDRAM [1].

| Feature                   | SRAM      | DRAM   | GC-eDRAM |

|---------------------------|-----------|--------|----------|

| Cell Size                 | Large     | Small  | Small    |

| Refresh Needed            | No        | Yes    | Yes      |

| <b>Process Complexity</b> | Low       | High   | Low      |

| Read Destructive          | No        | Yes    | No       |

| Leakage Power             | High      | Low    | Low      |

| Access Speed              | Very Fast | Medium | Fast     |

#### **1.2** Evaluation of Gain Cells (GCs)

The continuous scaling of CMOS technology has enabled a significant improvement in the performance of digital systems. But this aggressive scaling has also introduced some critical challenges, especially for embedded memories, which occupy at least half of SoCs' overall size and power budget [21]. As technology scaled down to nanometer sizes, traditional memory architectures like SRAM and DRAM have faced significant limitations. In this regard, eDRAM macrocell, also known as gain cell-based memories (GC memories), have developed, which provide a balanced solution between speed, storage density, and energy efficiency.

To store data as an electric charge, the traditional eDRAM bitcell needed a physically built storage capacitor [12]. It additionally utilizes the storage capacitor for write and read operations using a single MOSFET.

Unfortunately, making high-density trench or stacked capacitors for this kind of conventional eDRAM needs extra steps in the processing line. As feature sizes reduced, building sufficiently large and reliable capacitors became extremely difficult. That is why it is incompatible with common CMOS technologies [9]. On the other hand, traditional SRAM cells have lower noise margins and higher leakage currents in highly scaled nodes (65 nm, 45 nm, and 28 nm). As technology scales further, the transistor mismatch and reduced V<sub>DD</sub> make SRAM less reliable unless an extra area and complexity are sacrificed, such as using 8T or 10T SRAM designs [8].

Fig. 1.4 Schematic diagram of a 2T0C DRAM macrocell [15].

The gain cell (GC) concept [22] was introduced to overcome the limitations of traditional SRAM and DRAM memories. It offers a middle-ground solution by providing logic compatibility, small area size, and reduced leakage without the need for any complicated process steps. A GC is a memory structure that stores data dynamically on the parasitic capacitance of a transistor's node (called the storage node, SN) rather than an explicit capacitor. A typical GC uses two transistors, a write transistor (MW) to write the data into the SN and a read transistor (MR) to read the stored data (Fig. 1.4). To improve stability or retention performance, some topologies use one or two additional transistors. GC-eDRAM is completely compatible with popular digital CMOS technologies, as the device is

fabricated solely from accessible metal and vias and MOSFETs. MOSFETs are utilized as Metal Oxide Semiconductor Capacitor (MOSCAP) and as access transistors (write and read transistors). One can improve the storage node capacitance by use of metal layers and vias [1]. Since GC-eDRAM offers many of the benefits of both SRAM (like standard digital CMOS logic compatibility) and 1T1C eDRAM (like better storage density) and prevents many of the problems of both SRAM (like the large bitcell) and 1T1C eDRAM (like destructive reading, restoring, and additional manufacturing expenses for specific processes) [12], it is an interesting substitute. That is why GC-eDRAM macrocells are easy to integrate into every digital system without extra production expenses. Dynamic data retention characteristics are the primary issue of GC-eDRAM over SRAM; hence, it demands periodic refresh operations.

**Fig. 1.5** Schematic representation of (a) 2T Gain Cell [16], (b) 3T Gain Cell [18], (c) 4T Gain Cell [23], and (d) 5T Gain Cell [14].

Over the past ten years, a wide range of GC topologies with 2-5 transistors have been proposed [14], [16], [18], [23]. A basic example of these GCs is displayed in Fig. 1.5. Every one of these designs utilizes a MW to access and store charge on the SN. Additionally, every GC topology has an SN capacitor made up of MW junction capacitance and MOSCAP. In the two-transistor (2T) configuration, the MOSCAP storage transistor can also be used as MR. The comparatively bigger three-transistor (3T) [18] version demonstrates a more reliable read operation because it uses a distinct MR that separates the read bit line (RBL) from MR. For enhanced read robustness, certain four-transistor (4T) [23], [24] GCs use a fourth transistor as MOSCAP capacitively connects the RBL to the SN and boosts the SN capacitor. The word 'gain' refers to the read transistor's transconductance gain, which indicates little changes at storage node voltage (gate voltage of MR) can result in a change in read path current (drain current of MR) [25].

#### 1.3 Different Types of GC Topology

Several gain cell topologies have been proposed in the research community, each offering different trade-offs between area, speed, retention time, and complexity. While the fundamental principle of storing data dynamically using parasitic capacitance remains the same, the number of transistors in all of these circuits is lower than in standard SRAM circuits. This section will explore the popular GC topologies, such as 2T, 3T, 4T, and 5T, with their structure, fundamental principles, benefits, drawbacks, and trade-offs.

#### 1.3.1 2T Gain Cell

The two-transistor (2T) gain cell [16], [17], [26], [27], [28] is the simplest and most area-efficient design. In 2T designs, the simple topology usually has a MW for writing and a MR that stores information and also reads it. The parasitic capacitance corresponding to SN is typically formed between the drain region and the substrate or adjacent interconnects.

As soon as the write word line (WWL) is asserted, MW links the write bit line (WBL) to SN and writes the available data at WBL to SN [16]. When the read word line (RWL) is asserted, MR drives a current through the RBL, and that is how we read the data from the SN without destroying the stored charge. During hold mode, both transistors remain off, and the charge (data) stored on SN is retained for a certain duration depending on leakage currents. However, data retention time (DRT) is comparatively limited because the storage node is weakly held [29].

One of the major advantages of 2T gain cells is area efficiency. With only two transistors, the cell footprint is very small compared to SRAM or DRAM, enabling higher memory density. Another benefit is non-destructive read, as the read transistor allows current through the readout path without lowering the stored charge [30].

The 2T topology suffers from lower retention time. Capacitive coupling (CC) effects between SN and the control lines (WWL, RWL, and RBL) arise from the 2T configuration. CC and leakage paths through MW and MR cause rapid data loss, which compromises the data integrity and reduces efficiency [31]. Thus, a third transistor is usually added, mostly to prevent RBL leakage and to avoid annoying capacitive couples between SN and RWL. In modern designs, implementation of several techniques, like using high-threshold (high-V<sub>Th</sub>) write transistor, body biasing, and optimized WBL during hold, has been applied to extend DRT, which makes it suitable for embedded memory applications [32].

#### 1.3.2 3T Gain Cell

To solve problems observed in 2T, the three-transistor (3T) gain cell [33], [34], [35], [36], [37], [38], [39] is utilized. This design reduced threshold voltage drop during write [40] and improved isolation between the write and read paths. Some designs also minimize RBL leakage and

prevent disrupting CC from RWL to SN. This helps maintain data for longer times without considerably expanding the area and makes it more robust than the 2T model. To improve retention and lower refresh requirements, certain 3T designs incorporate asymmetric transistor sizing or body biasing approaches [41]. Techniques like preferential boosting, where the read bit line or internal node is dynamically boosted by tying the MR drain to RWL instead of ground. Hence reducing some of the positive SN voltage in the pMOS MW design, further improve access times and prevent read-disturb [18]. The 3T GC improves noise margins and minimizes disturbance during read operations by having a dedicated read buffer. But it comes with a larger area and a little more control complexity. To maintain high-speed performance, surprisingly big cache memory designs choose the 2T topology at the expense of extra peripheral circuits [16], [26], [30].

#### **1.3.3 4T Gain Cell**

Turning now to the four-transistor (4T) gain cell, the design usually incorporates extra transistors for data integrity, boosting, or decoupling. These are frequently utilized in applications that require more stability and prefer refresh-free operation [23], [24]. Common designs use two transistors for write or access and two for read or isolation. The additional transistors contribute in the more separation of the write and read paths for non-destructive reads [20]. Another 4T design with three transistors and a 'gated diode' (MOS transistor serving as a storage device and amplifier for the cell voltage) enables techniques like preferential boosting for improved signal levels [42]. Even though 4T topologies have improved retention and better control over noise and leakage, they occupy more area and need complex circuit design because of more word lines or control signals.

#### **1.3.4 5T Gain Cell**

The five-transistor (5T) gain cell is a more modern invention designed for specialized applications like parallel sensing, ternary logic, or ultra-low power operation [43]. This design typically has three transistors for write/read and two for storage or level tuning. The extra transistor enables the storage node to be biased at an intermediate voltage level, so storing either '0,' '1,' or an intermediary 'X' logic [14]. This configuration allows more bits to be stored per cell. Other 5T designs, such as those in ultra-low power FDSOI, are perfect for IoT or biomedical edge applications because they achieve picowatt-level standby power [44]. Still, the area cost increases dramatically, and the design complexity increases as well.

In conclusion, the selection of the gain cell topology is an investigation of design space that balances performance, area, power, and retention. The 2T cells offer the highest density but the weakest retention, 3T maintains a balance with better control, 4T offers reliable read/write operation and long retention, and 5T creates opportunities for more sophisticated features like multi-bit storage and parallel sensing.

**Table 1.2** Comparison of different types of GC topology [13].

| Feature         | 2T GC    | 3T GC  | 4T GC  | 5T GC     |

|-----------------|----------|--------|--------|-----------|

| Area Efficiency | Highest  | High   | Medium | Low       |

| DRT             | Low      | Medium | High   | Very High |

| Read Stability  | Moderate | High   | High   | Very High |

| Complexity      | Very Low | Low    | Medium | High      |

#### 1.4 Features and Applications of Gain Cells

The GC-eDRAM shows particular characteristics and enables design choices that are uncommon to regular DRAMs and SRAM. The features of GC are described as follows —

**Fig. 1.6** Schematic representation of 2T GC showing write and read port [28].

An important aspect of gain cells is that they have two-port compatibility [28], which is their most notable characteristic. The GC-eDRAM is a dual port memory (Fig. 1.6) since a GC has both a write and a read port. As a result, it usually has separate address decoders for the write and read addresses.

With dual-port compatibility, another most advantageous characteristics of GC-eDRAM architecture is that it supports pipelined refreshing, which makes sure to simultaneously read and rewrite data for different cells within a single clock cycle [45]. This feature drastically lowers dynamic and leakage power compared to traditional DRAM architectures. With dual-port capability, the information can be refreshed by reading the content of the row at generic address n, while writing the previously read content back to the row at generic address n–1 within the same cycle. This capability is absent from traditional single-port DRAMs, which need two cycles to complete the same refresh operation [45].

As GC has two-port functionality for which reading becomes non-destructive and does not require any restore operation, unlike in 1T1C DRAM, where a single port is used for both write and read operations, and after every read operation, the data must be restored back to the capacitor [28]. Since the read path is isolated by another read transistor, the stored data can be sensed without changing the node voltage. By avoiding the need to restore the data, GC-eDRAM decreased power consumption per access cycle and reduced external circuit complexity and protected data during reading [46].

The small area footprint of gain cells is one of their most remarkable characteristics. Conventional 6T SRAM cells consume more space by using access transistors and cross-coupled inverters; gain cells are built by using only two transistors. Higher memory density is especially important in cache memory arrays, Artificial Intelligence (AI) and Machine Learning (ML) accelerator designs where vast amounts of on-chip memory are needed [26]. Apart from area, gain cells show logical process compatibility as discussed earlier.

In addition to features, GC has a wide and expanding range of applications, from low-power IoT sensors to high-speed logic cores. Because of its smaller footprint, GC has recently gained a lot of popularity as an on-chip cache memory, particularly as last-level cache in high-end processors [26]. GC is also used as eDRAM in portable electronic gadgets [47] and IoT deployments for sensor networks [48] because of low power consumption. GCs are utilized in Compute-in-memory (CIM) macros in AI accelerators and edge inference engines in order to reduce data movement overhead, which is one of the main sources of power consumption in neural accelerators [49]. Where power budgets are very limited in biomedical and IoT applications, subthreshold GC designs have shown great success; operating below 0.5V these designs can retain data using minimum power, like pico-watts per bit range [44]. Physical Unclonable Functions (PUFs),

where the inherent variations in leakage and retention time across gain cells are utilized as a form of silicon fingerprinting, is another new application [32].

#### 1.5 Motivation for 2T pMOS-only GC

**Fig. 1.7** Overview of 2T gain cell implementation options: (a) All pMOS Cell, (b) Mixed pMOS-nMOS Cell, (c) Mixed nMOS-pMOS Cell, and (d) All nMOS Cell [28].

In memory design, selecting the device architecture is vital, particularly when the objective is high data retention, low leakage power, and compatibility with deeply scaled technologies such as 28nm. Depending on the type of devices used (pMOS or nMOS) for these transistors, four 2T configurations are possible, which are shown in Fig. 1.7. The 2T pMOS-only gain cell is the effective option among different gain cell topologies for embedded dynamic memories intended for better retention and high-performance low-power applications [17], [28].

The most convincing reasons for choosing a 2T structure are its simplicity and compactness. It achieves an extremely compact area with just

two transistors, MW and MR, which allows more bits stored in a given silicon area. For applications like on-chip caches and portable electronics, where memory space frequently limits overall chip size, the 2T gain cell is an especially interesting choice [47].

Along with simplicity, choosing to use pMOS-only devices offers several benefits, especially at lower nodes such as 28nm and even below. When compared to nMOS devices, pMOS transistors inherently have lower subthreshold leakage currents. This is because pMOS devices have lower leakage when they are turned off due to their lower carrier mobility ( $\mu$ ) and higher  $V_{Th}$ . The main cause for SN charge loss is subthreshold leakage via MW. Thus, selecting the all-pMOS arrangement helps to increase the capacity of the memory to retain information without frequent refresh [16].

#### 1.6 Conclusion

In conclusion, the expansion of memory technologies has created demand for low-power, high-density structures with simple logic circuit integration. GC-eDRAM offers a promising solution by combining the advantages of SRAM and DRAM while dealing with their main drawbacks. Two major benefits of using a 2T pMOS-only gain cell in cutting-edge technologies like 28 nm are simplicity and leakage reduction. While many GC topologies have been investigated, the 2T design stands out for its compactness and retention efficiency. This chapter discussed the background and motivation behind GC memories, compared several topologies, and highlighted their features and uses.

#### 1.7 Organization of The Thesis

This thesis aims to explore and optimize a 2T pMOS-only gain cell based on 28nm double gate pMOSFET, with a focus on enhancing DRT and ensuring reliable operation at low supply voltages. There are five chapters in this thesis. The description of which is outlined below.

The study starts with chapter 1, which discusses the evaluation of GC memories, various topologies such as 2T, 3T, 4T, and 5T, and their key features and applications.

The detailed working of the 2T0C gain cell and the importance of DRT is presented in chapter 2.

Chapter 3 presents an analysis of 2T0C GC using 28 nm double gate pMOSFET. This chapter highlights the importance of back bias to reduce capacitive coupling and subthreshold leakage to get enhanced DRT.

The effects of temperature and supply voltage downscaling on GC performance are reported in Chapter 4.

The findings of this work are summarized in chapter 5.

#### Chapter 2

#### **Operation of 2T0C DRAM**

First chapter discussed GC as a promising solution for on-chip cache memory, especially as last-level cache in high-end processors [30]. This chapter will cover a detailed explanation of the operation of memory cell, explaining the fundamental write, hold, and read operations, as well as data storage using a parasitic node capacitor instead of a physical capacitor. Since its working depends on stored voltage levels at a floating node (SN), it is very important to understand charge leakage and device characteristics. This charge degradation at SN governs the retention time. The concept of data retention time (DRT), and the parameters influencing it, will also be discussed.

#### 2.1 Working of Gain Cell

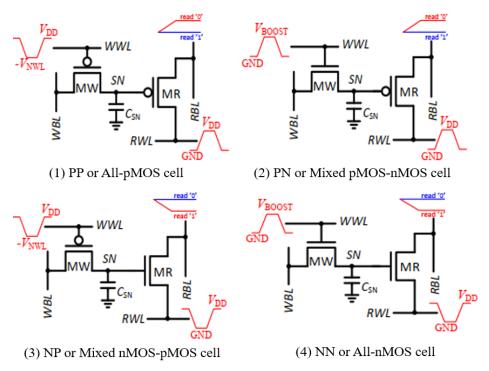

The fundamental idea behind any GC is to store digital information dynamically using charge on an internal node. This is achieved using two transistors, one for write access and another for read access. These two devices together form a memory element that stores data dynamically on SN. The working of GC happens in three operations: (1) writing data, (2) holding data, and (3) reading the stored data. Depending on the type of devices used (pMOS or nMOS) for these transistors, four 2T configurations are possible: (1) PP or All-pMOS cell where both MW and MR are pMOS transistors, (2) PN or Mixed pMOS-nMOS cell where MW is a pMOS-type transistor and MR is an nMOS-type transistor, (3) NP or Mixed nMOS-pMOS cell where MW is an nMOS transistor and MR is a pMOS transistor, and (4) NN or All-nMOS cell where both MW and MR are nMOS-type transistors (Fig. 2.1). Even though four configurations are different, all of these topologies follow a similar operating principle [29]: during write, MW

is turned ON, and it charges or discharges SN depending on the data available on WBL for writing; in the hold phase, both transistors are OFF, and the charge is expected to stay at SN until the next refresh; during the read phase, MR is turned ON, and the voltage at SN determines whether current will flow through MR to the read bit line (RBL), thus reading the stored value.

**Fig. 2.1** Two transistor gain cell implementation options including the schematic waveforms [29].

## 2.1.1 Write Operation

In a 2T gain cell, writing a bit involves turning ON MW and transferring available WBL voltage (data) to the SN [45]. The WWL, which is the gate terminal of MW, is activated (set high for nMOS MW and set low for pMOS MW), which turns ON the MW transistor (Fig. 2.1). The MW now connects the WBL to SN and transfers either logic '1' (high) or logic '0' (low) depending on the value of WBL. MW either pulls the storage node SN toward  $V_{DD}$  (logic 1) or lets it fall closer to the ground (logic 0).

For a pMOS-only GC topology, a negative control bias is fed to the WWL node so that the gate to source potential (V<sub>GS</sub>) becomes more negative than the threshold voltage of the MW, and the MW turns ON. However, due to the threshold voltage drop of the pMOS transistor, pMOS MW passes a weak '0' and a strong '1'. This weak logic '0' is a vulnerability, as it will rise further during the hold phase due to leakage. This incomplete voltage swing affects retention time, which will be discussed in detail later.

#### 2.1.2 Hold Operation

After the data has been written, WWL is de-asserted (turned low for nMOS and high for pMOS MW), which turns OFF the MW transistor, and the SN holds the stored voltage. Since there is no physical capacitor, the only element holding the charge is the parasitic capacitance at SN, which is made up of MW junction capacitance, MOSCAP, and any metal interconnects. Unfortunately, over time, leakage currents from the source/drain junctions through MW slowly destroy the charge. This process causes the voltage at SN to drift away from its original value - a phenomenon known as data degradation, and this degradation defines DRT. Factors like temperature and supply voltage downscaling directly impact this degradation, and that will be discussed later. The aim of this work is to minimize data degradation, i.e., maximizing DRT.

For a pMOS-only GC topology, the control bias is changed to positive so that the  $V_{GS}$  becomes less negative than the threshold voltage of the MW, and the MW turns OFF. This configuration is favorable because pMOS transistors leak less than nMOS, thanks to high  $V_{Th}$  and lower hole mobility ( $\mu_p$ ). Since pMOS passes weak '0', that is the reason for logic '0' degrading much faster than logic '1' in pMOS-only topology.

#### 2.1.3 Read Operation

The read transistor allows data to be sensed by the sense amplifier (SA) from RBL, depending on the charge present on SN. To read out the data, we applied a drain to source (V<sub>DS</sub>) potential across MR so that MR turns ON and current can flow. Keep in mind that during write and hold, we kept V<sub>DS</sub> equal to zero so that no current would flow through the readout path even if MR was activated by the SN (gate of MR). Before reading, to keep V<sub>DS</sub> of MR zero, both RWL and RBL are either pre-charged (for nMOS MR) or pre-discharged (for pMOS MR). As the nMOS passes a strong '0' and the pMOS passes a strong '1'. Before the read operation, RBL is pre-charged for nMOS (pre-discharged RBL for pMOS) to enable changes in RBL to be sensed during readout.

In the read phase, RWL is pulled low (for nMOS MR) or high (for pMOS MR), and V<sub>DS</sub> becomes nonzero. For a pMOS-only GC topology, if SN holds a logic '0', then the gate to source potential (V<sub>GS</sub>) of MR becomes more negative than the threshold voltage, which turns ON MR, and current will flow from RWL to RBL [45]. This charges RBL, and thus read data as logic '0'. If SN holds a logic '1', then the V<sub>GS</sub> of MR is less negative than the threshold voltage, and MR remains OFF. No current will flow from RWL to RBL, RBL voltage will remain at zero, and thus we fetch data as logic '1'. The schematic waveforms describing GC working for different topologies are shown in Fig. 2.1.

## **2.2** Data Retention Time (DRT)

DRT is an important characteristic parameter of volatile memory because after this time period, memory needs refreshing. In GC, data is stored as electrical charge on a SN, which degrades over time. DRT is the time up to which the sense amplifier can read the data correctly [40].

**Fig. 2.2** Three types of leakages that can destroy stored data in a conventional 2T gain cell [17].

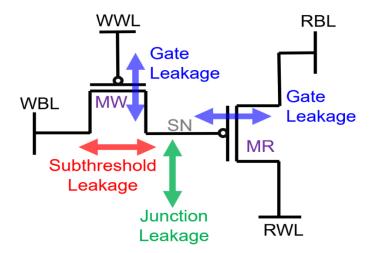

The primary reason for stored data  $(V_{SN})$  degradation is leakage through MW and MR. Fig. 2.2 shows the structure of a conventional 2T eDRAM cell with its three types of leakages [17]:

- (1) Subthreshold leakage: The dominant leakage mechanism that destroys the stored data the most. Even when the MW is OFF, some current penetrates through its channel. This mechanism weakens both logic '0' and logic '1'.

- (2) Gate leakage: In advanced technology, thin gate oxides allow tunneling current to pass through the gate terminal. This leakage mechanism weakens one logic and strengthens another. To turn OFF the pMOS MW, we need a positive voltage at the gate terminal, which charges both logic '0' (weakens) and logic '1' (strengthens).

- (3) Junction leakage: Reverse-biased diodes between drain/source and substrate leak small currents, especially at high temperatures, which also weakens one logic and strengthens another [29]. These leakage phenomena pull the voltage on SN away from its stored state, and if not refreshed in time, the stored value flips.

#### 2.2.1 Importance of DRT

The importance of DRT is that power consumption is inversely proportional to DRT [50]. One might think that if DRT is low, then why not just refresh more frequently? The problem is refreshing consumes power, and in GC the total power consumption is dominated by the retention power due to periodic refreshing. A system/array with many cells, the required energy for refreshing every few microseconds will be substantial. Moreover, in low-power systems, where the system spends long idle periods in sleep or near-zero power modes, a short DRT would lead to unnecessary wakeups just to refresh memory, and the refresh energy may exceed the energy used to compute. Therefore, it is always better to improve DRT rather than refresh more often. Equation 2.1 shows that memory will consume less power if DRT is high [50]. Hence, DRT is a critical design parameter that must be understood and optimized.

$$P_{retention} = P_{leakage} + P_{refresh} = V_{DD}I_{leak} + \frac{E_{refresh}}{t_{refresh}}$$

(2.1)

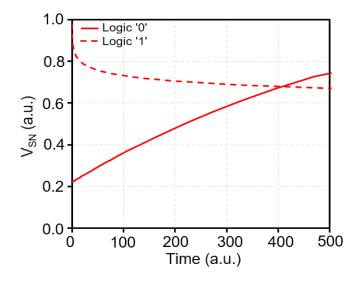

**Fig. 2.3** Storage node voltage  $(V_{SN})$  degradation of 2T GC after write operation.

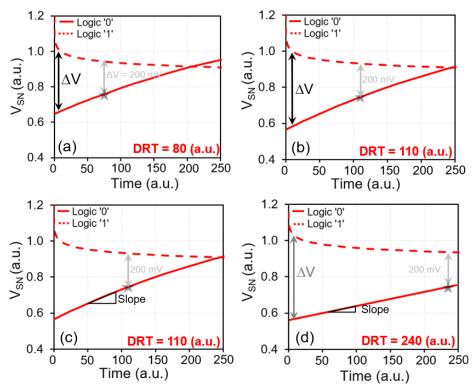

#### 2.2.2 Method to estimate DRT

There are two popular methods [10], [27] to estimate the data retention time of a gain cell. One is the threshold voltage-based method, and the other is the 200 mV differential method. Fig. 2.3 shows the degradation of the stored information ( $V_{SN}$ ) over time. As lower voltage is considered logic '0' and higher voltage is taken as logic '1', so after a write operation, the storage node voltage for logic '0' increases and for logic '1' decreases over time.

#### 2.2.2.1 Method 1 — Threshold Voltage of Read Transistor (MR)

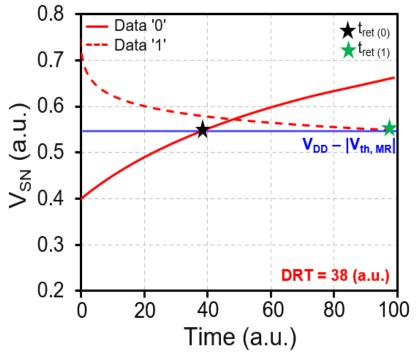

This method [27] is based on determining the rate of decay of the storage node before a read error occurs. In this method, DRT is defined as the time up to which the voltage on the SN remains below (for logic '0') or above (for logic '1') the threshold voltage ( $V_{Th}$ ) of the read transistor MR.

**Fig. 2.4** Storage node voltage ( $V_{SN}$ ) degradation of an arbitrary pMOS-only GC after write operation and DRT estimation using 1<sup>st</sup> method [27].

During read, the current flowing through MR depends on the V<sub>GS</sub>) and V<sub>Th</sub>. For one stored logic (depending on the type of MR), at the gate of MR will activate the read transistor ON, which results in a current flow through MR, and for other logic, MR will remain OFF and no current will follow. In this way, SA can distinguish between logic '0' and logic '1', and reading occurs. As an example, a pMOS read transistor will follow current as long as stored node voltage (V<sub>GS, MR</sub>) remains below (logic '0') its threshold value. As leakage changes SN voltage, so logic '0' drifts upward, and once it crosses the critical point (V<sub>DD</sub> - |V<sub>Th, MR</sub>|), the read transistor can't distinguish logic '0' from a logic '1' anymore, and data will be lost. This method estimated DRT for both logic '0' and logic '1' separately, and the overall DRT is taken as the minimum of that. Fig. 2.4 shows the V<sub>SN</sub> degradation after the write operation and presents the estimated DRT value according to this method. This approach is accurate and straightforward for simulation because it reflects actual read failure conditions, but there is a limitation to this method. If, just after writing, V<sub>SN</sub> for both logic lies either below or above the critical value (V<sub>DD</sub> - |V<sub>Th, MR</sub>|), then MR cannot distinguish logic '0' and logic '1' levels. That is why alternate method for estimates DRT is required. In this method, DRT is the time when the voltage difference between two logic levels reaches a value of 200 mV [10].

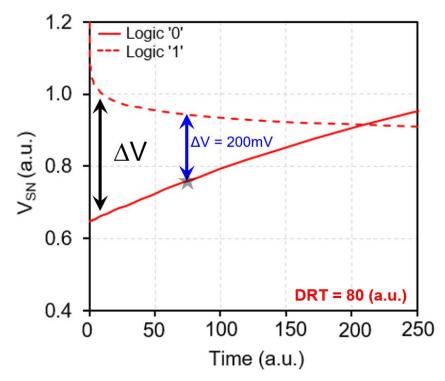

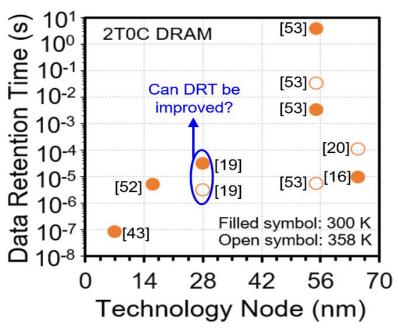

#### 2.2.2.2 Method 2 — 200 mV Differential Method

In this simpler approach, DRT is evaluated by tracking how long the voltage difference between logic '1' and '0' stays above 200 mV [10]. It is assumed that data is still readable as long as there is a voltage difference of at least 200 mV between logic '0' and logic '1' on SN. This strategy is based on the assumption that modern sense amplifiers can reliably detect a potential difference of 200 mV.

**Fig. 2.5** Storage node voltage  $(V_{SN})$  degradation of an arbitrary pMOS-only GC after write operation and DRT estimation using  $2^{nd}$  method [10].

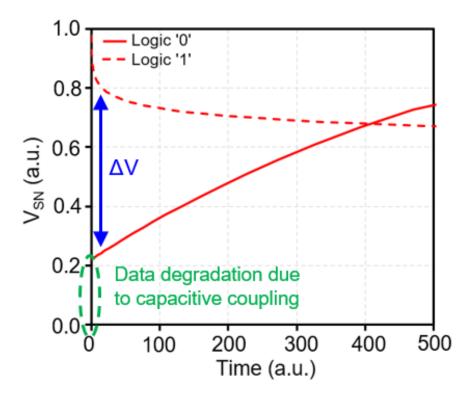

Fig. 2.5 illustrates the degradation of the stored information over time and presents the estimated DRT value according to this method. At the onset of the hold operation, we got a voltage difference ( $\Delta V$ ) between logic '1' and logic '0'. As lower voltage is considered logic '0' and higher voltage is taken as logic '1', hence after a write operation, the storage node voltage for logic '0' increases and for logic '1' decreases over time, and  $\Delta V$  decreases over time. DRT estimated as the moment when the voltage difference between two logic levels reaches a value of 200 mV. In an ideal scenario this difference should be 0 V to distinguish between logic '0' and logic '1', but in practice this 200 mV gives a sufficient margin to the sense amplifier to distinguish between '0' and '1' even if there is any fluctuation. This method is more conservative and gives safer design margins, which is why it's often used in several reports [20], [44], [46]. In this work, this method is used to estimate DRT.

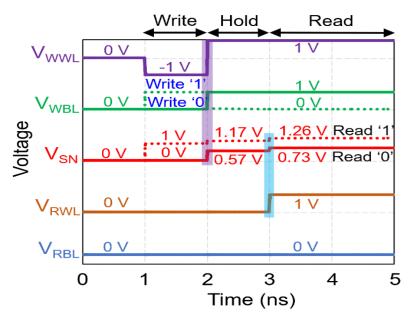

## 2.2.3 Improving DRT

Improving DRT is better approach to minimize frequent refresh. In a dynamic memory cell like the 2T gain cell, the primary cause of data degradation is leakage current, particularly the subthreshold leakage through MW. This current continuously drains the stored voltage on the floating storage node during the hold state. Therefore, the most direct and effective strategy for enhancing DRT is to suppress leakage as much as possible. This includes using transistors with higher threshold voltages [29] (such as pMOS) and applying reverse body biasing [51] to control V<sub>Th</sub> such that MW enters into the hard-off state during hold.

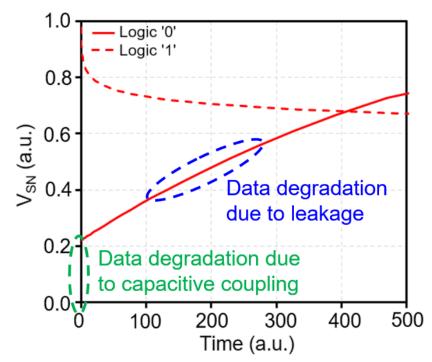

Fig. 2.6 Impact of leakage and capacitive coupling on storage node voltage  $(V_{SN})$  degradation.

Fig. 2.6 illustrates the degradation of the stored information over time due to leakage. Along with this continuous degradation, there is a sudden degradation of data at the onset of the hold operation, and this degradation is because of capacitive coupling (CC).

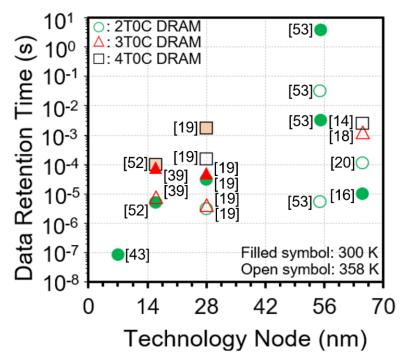

Beyond leakage suppression, there are also architectural solutions that can enhance DRT. Gain cell topologies [14], [19], [39] such as 3T0C, 4T0C, and 5T0C include extra transistors to improve data stability. These designs improve write/read isolation and enhance retention capabilities. However, these improvements come at the cost of increased area and peripheral circuit complexity, which makes them less suitable for dense arrays or compact on-chip memory macros where space is vital [47]. Fig. 2.7 shows the reported DRT values for different architectures.

**Fig. 2.7** Reported DRT values [14], [16], [18], [19], [20], [39], [43], [52], [53] of Si GC-eDRAM at different technology nodes.

To address this trade-off, the focus of this work remains on the 2T topology, which is the most compact among gain cell structures. Instead of adding extra transistors, this work explores the use of double gate (DG) pMOSFETs to improve DRT. DG devices offer better electrostatic control over the channel and significantly reduce subthreshold leakage and minimize CC effects at the storage node. These properties make them perfect for extending data retention without introducing any area overhead.

## 2.3 Conclusion

The functional behavior of the 2T gain cell memory has been thoroughly covered in this chapter, with a particular focus on the pMOS-only configuration. Study started with a general overview of how the gain cell operates, elaborating it into its three main states - write, hold, and read. This chapter explored how the stored charge is vulnerable to various leakage mechanisms. This chapter also had a focus on understanding data retention time, a critical metric for dynamic memory cells. Two commonly used methods for evaluating data retention time, based on the threshold voltage of the read transistor and the 200 mV voltage margin rule, were presented in detail. The understanding gained from this chapter prepares one for the next stage of this work.

## Chapter 3

# Double Gate based 2T pMOS-only GC

## 3.1 Double Gate (DG) p-type MOSFET

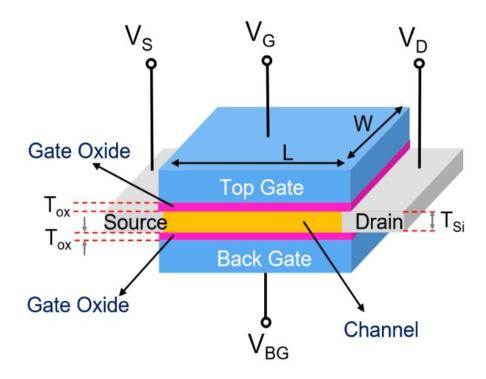

Fig. 3.1 Schematic diagram of a DG-MOSFET.

The increasing need for high-density and low-power digital systems is driving CMOS transistors to continue scaling into the nanoscale regime [54], [55]. However, as CMOS technology scales down beyond 28nm, controlling leakage currents and improving electrostatic integrity become more challenging due to the occurrence of short channel effects (SCEs) [56]. Traditional bulk MOSFETs have higher leakage and threshold voltage variability due to their poor channel control and increasing SCEs. To overcome this issue, a multi-gate transistor, specifically a DG-MOSFET

architecture is used in this work for the design of a 2T gain cell. Compared to traditional planar CMOS technology, the DG concept can significantly improve SCE mitigation at shorter channel lengths [57].

Fig. 3.1 shows the schematic of a double gate MOSFET, where the source and drain are connected at either end of the channel. Unlike single-gate MOSFETs (SG-MOSFETs), where the gate controls the channel from one side, DG MOSFETs employ two gates, a top gate (also known as the front gate) and a back gate (also known as the bottom gate), to control the channel simultaneously from both sides.  $V_G$  and  $V_{BG}$  are the control voltages at the top gate and at the back gate, respectively.  $V_S$  and  $V_D$  are the voltages at the source and the drain terminals.

**Table 3.1** Dimensions of DG-pMOS used in this work.

| W (nm) | L (nm) | Tox (nm) | T <sub>Si</sub> (nm) |

|--------|--------|----------|----------------------|

| 1000   | 28     | 1.3      | 7.2                  |

Table 3.1 shows the dimensions of DG-pMOS used in this work, where W is width, L is the gate length,  $T_{OX}$  is oxide thickness of  $SiO_2$  layer, and  $T_{Si}$  is the silicon thickness of the transistor.

The utilization of double gates effectively enhances the coupling between the gate and channel, thereby facilitating the suppression of SCEs [57]. Furthermore, dual gate architecture creates a symmetric electrostatic field on the channel, which suppresses unwanted influence from the drain and source. As a result, DG-MOSFET exhibits reduced off-current, contributing to overall enhanced performance and efficiency in circuit design [58]. DG-MOSFETs offers higher ON current and reduced OFF current, enabling operation at lower supply voltage [59]. Operating at threshold voltages also reduces the power consumption. Thus, DG-

MOSFETs can improve DRT in gain cell applications by reducing SCEs and the off-state leakage current.

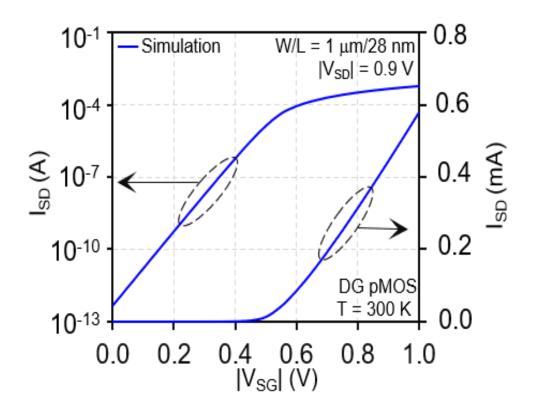

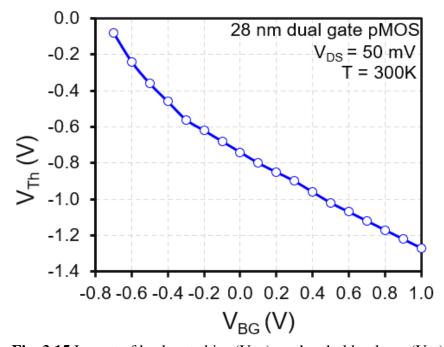

Fig. 3.2 Transfer characteristics of DG-pMOS.

As illustrated in Fig. 3.2, simulated transfer characteristics ( $I_{SD}$  vs  $V_{SG}$ ) of DG-pMOS transistor. The simulation [60] included field, concentration and temperature dependent carrier mobility besides module for generation-recombination and quantum confinement effects. Temperature dependent carrier lifetime was also considered.

Two important parameters for transistor are on-current ( $I_{ON}$ ) and off-current ( $I_{OFF}$ ).  $I_{OFF}$  is a source to drain current ( $I_{SD}$ ) when source to gate voltage ( $V_{SG}$ ) at 0 V and source to drain voltage ( $V_{SD}$ ) at  $V_{DD}$ . In this work,  $V_{DD}$  is equal to 1 V.  $I_{ON}$  is a source to drain current ( $I_{SD}$ ) when source to gate voltage ( $V_{SG}$ ) and source to drain voltage ( $V_{SD}$ ) at  $V_{DD}$ . Mathematically, the same can be expressed as

$$I_{OFF} = I_{SD} @ (V_{SG} = 0 \ V \ and \ V_{SD} = V_{DD})$$

(3.1)

$$I_{ON} = I_{SD} @ (V_{SG} = V_{SD} = V_{DD})$$

(3.2)

The most significant advantage shown in the above plot (Fig. 3.2) is that the DG-pMOS device achieves almost twice the I<sub>ON</sub> compared to the SG FDSOI [61]. This means that the DG transistor will finish the transition more quickly during a write operation when a logic value needs to be stored on the floating storage node of the gain cell. This leads to a significant improvement in the write speed capability of the device. Furthermore, the I<sub>OFF</sub> in DG-pMOS is decreased by nearly two orders of magnitude in comparison to SG FDSOI [61]. This reduction is extremely helpful during the hold phase, where subthreshold leakage has to be minimized to maintain the voltage level on the SN. The main aim of this work is improving data retention time, which increases with the duration of the SN able to preserve its value. The next sections will investigate the utilization of this DG-pMOS device in 2T pMOS-only gain cell design and way of enhancing DRT through effective biasing.

## 3.2 Double Gate 2T pMOS-only Gain Cell

## 3.2.1 Introduction to DG 2T pMOS-only GC

This section presents the proposed gain cell (GC) architecture which utilizes the advantages of a double gate (DG) 2T pMOS-only configuration. The cell is designed to reduce leakage, suppress capacitive coupling, and extend DRT without significantly increasing the area beyond the classical 2T footprint.

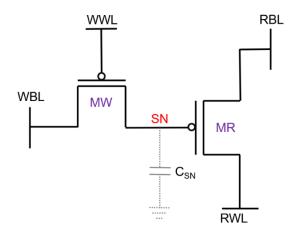

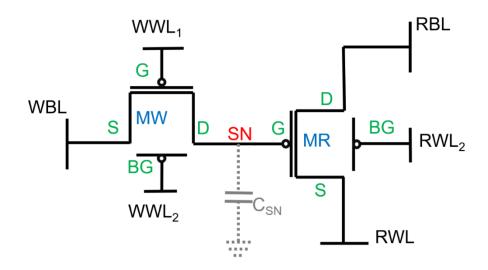

Fig. 3.3 Schematic representation of double gate 2T pMOS only gain cell.

Fig. 3.3 shows the suggested architectural schematic of DG 2T pMOS-only gain cell. The fundamental design is still the same as that of a traditional 2T gain cell. It consists of a MW and a MR, with the SN in between. Both transistors are implemented using double gate pMOS and connected such that the front and back gates of every device can be independently biased to optimize leakage control and capacitive behavior. The MW on the left is controlled by WWL<sub>1</sub> (front gate) and WWL<sub>2</sub> (back gate). The front gate of MR is connected with SN. During read, MR is controlled by RWL (source) and RWL<sub>2</sub> (back gate). A single SN connecting MW and MR, storing logic '1' or '0' depending on the last write operation.

The WBL provides data for writing, and from the read bit line RBL the data can be fetched. This cell is fully compatible with standard logic CMOS and offers scalable leakage control using the double gate structure. The use of pMOS-only transistors reduces gate and subthreshold leakage.

## 3.2.2 Working of DG 2T pMOS-only GC

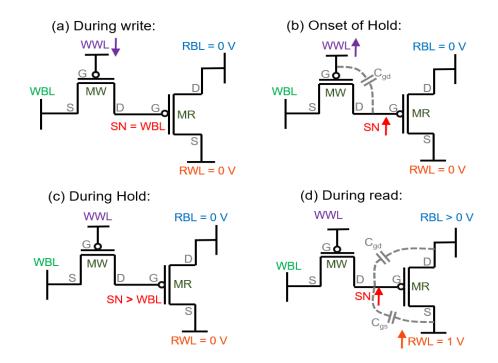

#### 3.2.2.1 Write Operation

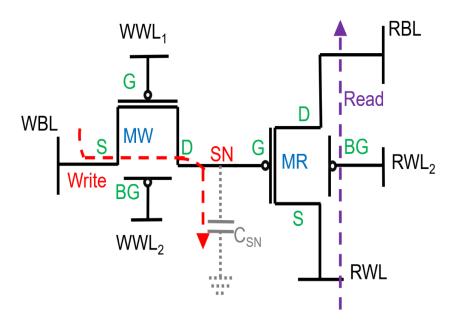

**Fig. 3.4** Schematic representation of DG 2T pMOS-only GC showing write and read paths.

Fig. 3.4 illustrates schematic with write and read paths of DG 2T pMOS-only GC. In a 2T gain cell, writing a bit involves turning ON the MW and transferring available write bit line voltage (data) to the SN [45].

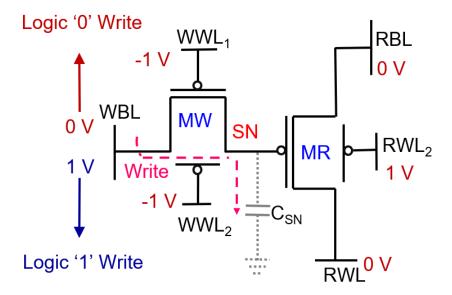

## Write operation

**Fig. 3.5** Bias representation of DG 2T pMOS-only GC during write operation.

In DG 2T pMOS-only GC, the write operation is enabled by activating both WWL<sub>1</sub> and WWL<sub>2</sub> (pulling them LOW for pMOS) to turn ON the MW. To write logic '1', WBL is pulled to  $V_{DD}$  (= 1 V), and SN is pulled toward the  $V_{DD}$  through the conducting MW. Similarly, to write logic '0', WBL is grounded to 0 V, and SN is pulled down to a level near ground. As shown in Fig. 3.5, WWL<sub>1</sub> and WWL<sub>2</sub> are pulled to -1 V to ensure strong conduction through MW. This helps write the data very fast. Meanwhile, the MR remains OFF since RWL<sub>2</sub> is held high and also zero potential difference between RWL and RBL ( $V_{SD, MR}$ ) makes sure no current will flow through MR.

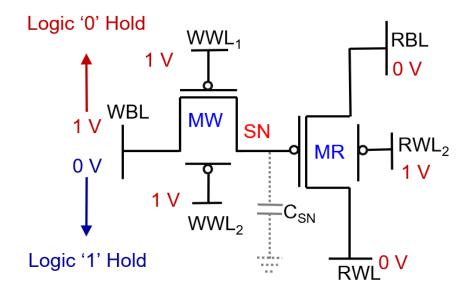

#### 3.2.2.2 Hold Operation

## Hold operation

**Fig. 3.6** Bias representation of DG 2T pMOS-only GC during hold operation.

Once the data is written to the SN, the write word lines  $WWL_1$  and  $WWL_2$  are deactivated (set to 1 V, which is high for pMOS and thus turns MW OFF). At the same time,  $RWL_2$  is also high to turn OFF MR (Fig. 3.6). This isolates the SN completely, allowing it to retain its charge on the storage node capacitance  $C_{SN}$ .

This mode is highly sensitive to leakage and capacitive noise. Here the pMOS-only configuration becomes favorable because pMOS transistors leak less than nMOS due to their higher  $V_{Th}$  and lower  $\mu_p$ . Furthermore, due to the double gate pMOS structure, an independent bias at WWL<sub>2</sub> can further increase the  $V_{Th}$  of the MW transistor and suppress leakage.

#### 3.2.2.3 Read Operation

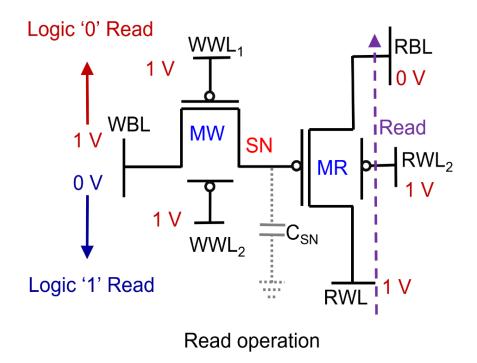

**Fig. 3.7** Bias representation of DG 2T pMOS-only GC during read operation.

As shown in Fig. 3.7, to perform a read, a drain to source potential is applied across MR in order for current flow, and at this time WWL<sub>1</sub> and WWL<sub>2</sub> remain high (MW is OFF). The read word line (RWL) pulled HIGH (1 V), keeping RBL at 0 V. If SN holds a logic '0' (0 V), then the V<sub>GS</sub> of MR becomes more negative than the threshold voltage, which turns ON MR, and current (I<sub>DS</sub>) will flow from RWL to RBL. This charges RBL, and thus read data as logic '0'. If SN holds a logic '1' (1 V), then the V<sub>GS</sub> of MR remains less negative than the threshold voltage, and MR stays OFF. No current will flow from RWL to RBL, RBL voltage will remain at zero, and thus data read as logic '1'. This operation ensures no disturbance to SN during read because of two port compatibility.

#### 3.2.2.4 Timing Diagram

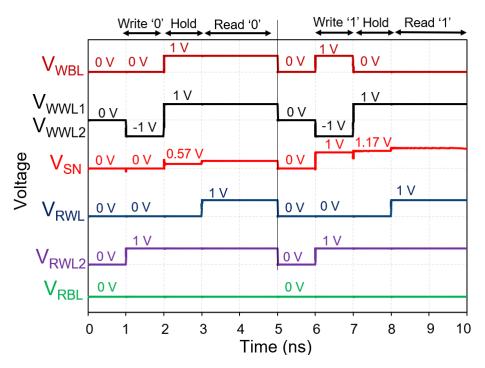

**Fig. 3.8** Timing diagrams demonstrating DG 2T pMOS-only GC operations.

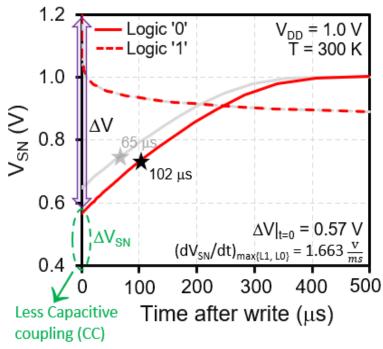

The timing diagram in Fig.3.8 displays voltages over time for WBL, WWL<sub>1</sub>, WWL<sub>2</sub>, SN, RWL, RWL<sub>2</sub>, and RBL during a complete Write  $\rightarrow$  Hold  $\rightarrow$  Read sequences for both logic '0' and logic '1'. During the write operation,  $V_{WWL_1}$  and  $V_{WWL_2}$  = -1 V turn ON MW, and SN is driven to 0 V for logic '0' ( $V_{WBL}$  = 0 V) and to 1 V for logic '1' ( $V_{WBL}$  = 1 V). In the hold operation,  $V_{WWL_1}$  and  $V_{WWL_2}$  = 1 V turn OFF MW, and SN is expected to remain data. SN drifts the data over time because of leakage and capacitive coupling. One can notice that although 0 V is written for logic '0', but at the onset of hold, SN voltage instantly degraded to a higher value such as 0.57 V. This is because of capacitive coupling. The detailed analysis has been present in the next section. For read '0' operation, MR turns ON and RBL charges towards 1 V.

## **3.2.3** Capacitive Coupling (CC)

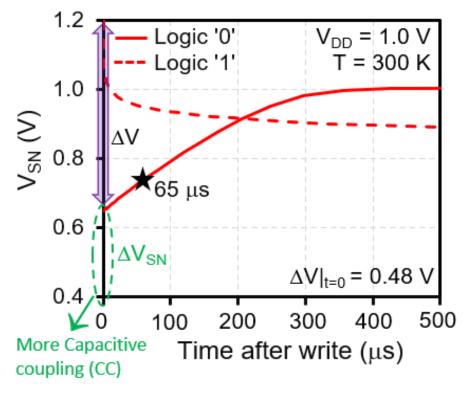

**Fig. 3.9** Impact of capacitive coupling (CC) on storage node voltage ( $V_{SN}$ ) at the beginning of hold state.

In nanoscale CMOS circuits, capacitive coupling is an important phenomenon that refers to a voltage change in one node affecting the voltage of an adjacent node through a parasitic capacitor [62]. The impact of CC is most prominent right after a write operation, at the beginning of the hold phase. The Fig. 3.9 shows logic '0' on SN has a sharp voltage level jump. This degradation is not gradual and cannot be assigned to leakage currents. Instead, it is the result of rapid gate voltage transitions, particularly when WWL or RWL switches states. This sudden jump compromises the voltage difference ( $\Delta V$ ) between logic levels and reduces DRT. Thus, suppressing CC becomes an essential strategy for enhancing retention.

Capacitive coupling refers to the unintentional transfer of electrical energy between two nodes without having any direct electrical connection between them [63]. This transfer occurs due to the presence of parasitic capacitance between the nodes, where a voltage transition at one node induces a voltage shift at another node. The coupled voltage can be approximated by ohm's law-based equation 3.3, which represents larger bias changes over shorter timescales  $(\frac{dV}{dt})$  induce higher capacitive coupling.

$$V_{coupled} \cong (C\frac{dV}{dt})R$$

(3.3)

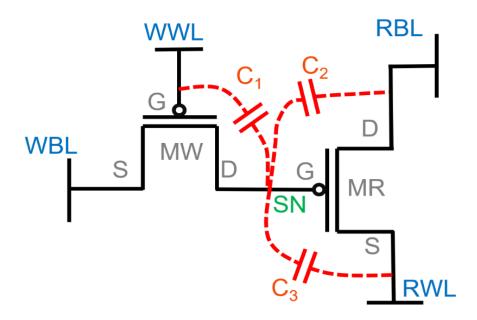

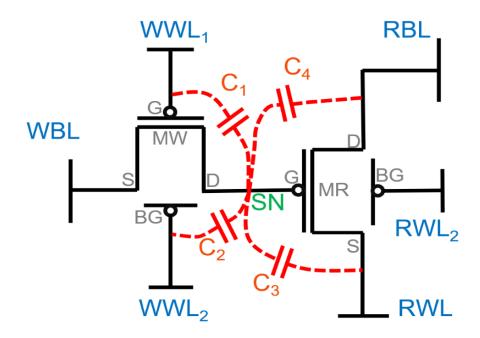

**Fig. 3.10** Schematic of a 2T GC with the coupling capacitances between SN, WWL, RBL, and RWL [62].

MOSFET contains many parasitic capacitances, but here the schematic highlights 3 major parasitic capacitances that are directly connected to the storage node and other control nodes (Fig. 3.10). In gain cells, the SN is surrounded by several control and data lines, such as WWL, RWL, and WBL — all of which are capable of coupling the charge on the SN during transitions. The effect of CC is that if a node voltage changes rapidly, then it induces a change in the storage node voltage [63].

**Fig. 3.11** Impact of capacitive coupling on storage node voltage during transitions of control node biases [63].

The Fig. 3.11 above illustrates the effect of CC on SN voltage throughout memory operation. During write, a lower WWL voltage activates the pMOS MW, and SN voltage is driven to  $V_{WBL}$ . At the onset of the hold operation, when we increased the WWL voltage to turn OFF MW, then some voltage is induced through gate to drain capacitance ( $C_{gd}$ ) into the storage node. When the RWL bias is changed to read the data, it again coupled an unwanted shift on storage node voltage [63]. This phenomenon is captured by the following mathematical models [62], which conclude a larger change in control node biases (such as  $\Delta V_{WWL}$  and  $\Delta V_{RWL}$ ) results in a larger change in storage node voltage ( $\Delta V_{SN}$ ).

$$\Delta V_{SN} \cong \frac{c_1}{c_1 + c_2 + c_3} \Delta V_{WWL} \tag{3.4}$$

$$\Delta V_{SN} \cong \frac{C3}{C1 + C2 + C3} \Delta V_{RWL} \tag{3.5}$$

**Fig. 3.12** Timing diagrams demonstrating capacitive coupling in 2T GC.