## **Exploring Heterogeneous Computing Platforms** for Molecular Dynamics-Based Calculations

#### **A THESIS**

Submitted in partial fulfillment of the requirements for the award of the degree of

Master of Technology

by

AMIT SINGH

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE May 2025

#### INDIAN INSTITUTE OF TECHNOLOGY INDORE

#### CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the thesis entitled Exploring Heterogeneous Computing Platforms for Molecular Dynamics-Based Calculations in the partial fulfillment of the requirements for the award of the degree of MASTER OF TECHNOLOGY and submitted in the DEPARTMENT OF ELECTRICAL ENGINEERING, Indian Institute of Technology **Indore**, is an authentic record of my own work carried out during the time period from July 2024 to May 2025. This thesis has been submitted under the supervision of Prof. Srivathsan Vasudevan and Prof. Satya S. Bulusu, IIT Indore.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other institute.

> Signature of the student with date (AMIT SINGH)

This is to certify that the above statement made by the candidate is correct to the best of my/our knowledge.

V. Swedler 22/05/2025 Signature of the Supervisor of

M.Tech. thesis (with date)

(Prof. Srivathsan Vasudevan)

22/05/2025

Signature of the Supervisor of

M.Tech. thesis (with date)

(Prof. Satya S. Bulusu)

AMIT SINGH has successfully given his M.Tech. Oral Examination held on May 5, 2025.

**Signature of M.Tech Supervisors**

Date 22/05/2025

1/ Smallin

Prof. Srivathsan Vasudevan

**Signature of M.Tech Supervisors**

Prof. Satya S. Bulusu

Saptarshi Ghosh

**Convener DPGC**

Date 23-05-2025

#### ACKNOWLEDGEMENTS

First and foremost, I would like to express my sincere appreciation to my thesis supervisors, **Prof. Srivathsan Vasudevan**, Professor, Department of Electrical Engineering, IIT Indore, and **Prof. Satya S. Bulusu**, Professor, Department of Chemistry, IIT Indore. Their generous guidance, support, mentoring, constant encouragement, and invaluable suggestions have been instrumental in making this work possible.

I am grateful to the M.Tech Coordinators, **Assistant Prof. Dr Rinkee Chopra** and **Prof. Abhinav Kranti** for their valuable advice, insightful comments and cooperation during my Research work presentation.

I express my sincere gratitude to IIT Indore for making available all facilities for this work. The cooperation from faculty and staff members at the Department of Electrical Engineering, IIT Indore, is gratefully acknowledged. Thanks are due to IIT Indore and the Ministry of Education, Government of India, for providing the stipend during the M.Tech. (VDN) programme.

I would also like to express my heartfelt gratitude to my parents and my younger brother for their unwavering support throughout my journey.

I would like to extend my wholehearted thanks to my lab members **Mr. Abhishek Ojha**, **Ms. Aparna Gangwar**, **Mr. Suvirn Upadhyay and Mr. Ashutosh Patel**and **Mr. Habit Tatin** for their help, support and for creating a positive environment in the lab throughout the year.

I would also like to express my gratitude to my seniors **Mr. Ankit Patel** and **Mr. Dharmendra Kartikey** for their support and guidance in my academic journey.

Last but not the least I am thankful to my friends without whom this journey would not have been so memorable. Special thanks to **Abu Said Parvez Alam**, **Akash Pandey**, **Suvirn Upadhyay**, **Atharv Limaye** and **Ashreta Sahay** for their help and support throughout this journey.

**Amit Singh**

## THIS THESIS IS DEDICATED TO MY FAMILY AND FRIENDS

#### **Abstract**

Molecular dynamics (MD) simulations demand high computational power to model atomic interactions over time, often limiting their scalability on conventional processors. This thesis explores the role of FPGA-based heterogeneous computing in accelerating MD calculations by offloading key computational tasks such as force computation and integration. Through custom hardware design using high-level synthesis, the study demonstrates how FPGAs can offer significant performance gains with improved energy efficiency compared to CPUs and even GPUs in specific scenarios. By placing FPGAs at the heart of the MD simulation workflow, this work highlights their potential to drive scalable and efficient molecular simulations, paving the way for broader adoption in computational science.

### **Table of Contents**

| TITLE PAGE        | I    |

|-------------------|------|

| DECLARATION PAGE  | II   |

| ACKNOWLEDGEMENT   | III  |

| DEDICATION PAGE   | IV   |

| ABSTRACT          | V    |

| TABLE OF CONTENTS | VI   |

| LIST OF FIGURES   | X    |

| LIST OF TABLES    | XIII |

| ACRONYMS          | XIV  |

#### **Contents**

| Chapte | r 1 Introd                                 | duction                                           | 1   |

|--------|--------------------------------------------|---------------------------------------------------|-----|

| 1.1    | Backgroun                                  | nd and motivation                                 | 1   |

| 1.2    | A Brief introduction to MD Simulation2     |                                                   |     |

| 1.3    | Computational challenges to MD Simulation  |                                                   |     |

| 1.4    | Heterogeneous Computing for MD simulation5 |                                                   |     |

| 1.5    | Perspective 6                              | e on Heterogeneous FPGA-based Computing Platforms |     |

| 1.5    | .1 Heteroger                               | neous Computing Platforms Based on FPGA           | 7   |

| 1.5    | .2 Advantag                                | es of FPGA                                        | 7   |

| 1.6    | What Are K                                 | Kernels8                                          |     |

| 1.7    | Partitioning                               | g10                                               |     |

| 1.8    | Conclusion                                 | 14                                                |     |

| 1.9    | 9 Objective                                |                                                   |     |

| 1.10   | Organizatio                                | on of the Thesis                                  |     |

| Chap   | ter 2 Lite                                 | erature Review                                    |     |

| 2.1    | High Thro                                  | ughput                                            |     |

| 2.2    | Low Laten                                  | ncy                                               |     |

| 2.3    | Timing                                     |                                                   |     |

| 2.4    | Evolution i                                | in High performance computing                     |     |

| 2.5    | CPU                                        |                                                   |     |

| 2.6    | GPU                                        | 21                                                |     |

| 2.7    | FPGA                                       |                                                   |     |

| 2.7    | 7.1 Internal a                             | architecture of FPGA                              | .23 |

|        | 2.7.1.1                                    | Look up Table25                                   |     |

|        | 2.7.1.2                                    | Flip-flop or Latches                              |     |

|        | 2.7.1.3                                    | Multiplexer                                       |     |

|        | 2.7.1.4                                    | Programmable Interconnect                         |     |

|        | 2.7.1.5                                    | Programmable I/O blocks                           |     |

|        | 2716                                       | DSP Slice 29                                      |     |

| 2.7.1.7 Block RAM                                            | . 30 |

|--------------------------------------------------------------|------|

| 2.7.1.7 Internal clock circuitry                             | . 30 |

| 2.8 Overview of FPGA H/W design Methodology                  | . 30 |

| 2.9 S/W design Flow for FPGA using Xilinx Tool               | . 33 |

| 2.10 Merits and Demerits of FPGA                             | . 34 |

| 2.10 Boards utilized in Data Tx and Rx                       | . 35 |

| 2.11 BASYS 3 Board                                           | . 37 |

| 2.11 UART as Communication Protocol                          | . 38 |

| 2.12 Merits of UART as Communication Protocol                | . 40 |

| 2.13 Demerits of UART as Communication Medium                | . 40 |

| 2.13 Identification of Communicated Data                     | . 41 |

| Chapter 3 System Design and Implementation                   | . 43 |

| 3.1 Xilinx FPGA Ip                                           | . 44 |

| 3.1.1 Microblaze Softcore Processor                          | 44   |

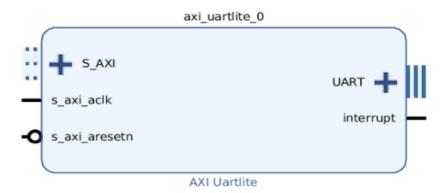

| 3.1.2 AXI UartLite                                           | 45   |

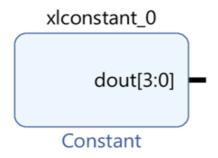

| 3.1.3 Constant IPs                                           | 45   |

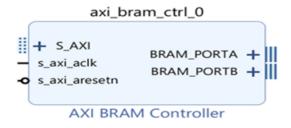

| 3.1.4 AXI BRAM Controller                                    | 46   |

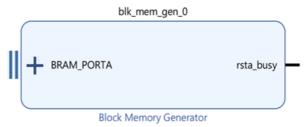

| 3.1.5 Block Memory Generator                                 | 47   |

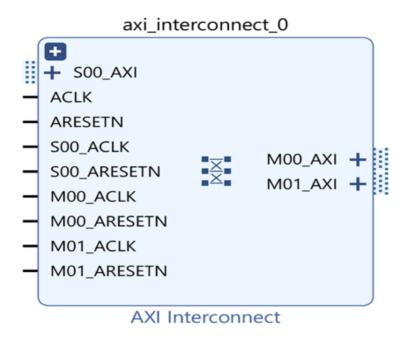

| 3.1.5 AXI Interconnect                                       | 48   |

| 3.1.6 AXI GPIO IP                                            | 49   |

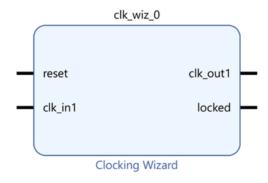

| 3.1.7 Clocking Wizard                                        | 50   |

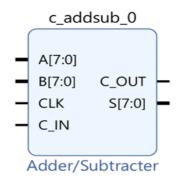

| 3.1.8 Adder/Subtractor IP                                    | 50   |

| 3.2 STM 32 microcontroller                                   | . 51 |

| 3.3 Jumper wire                                              | . 52 |

| 3.4 DSO                                                      | 53   |

| 3.5 Implementation of data tx and rx b/w BASYS3 board and PC | 53   |

| 3.6 B/D for data storage operation in BRAM of FPGA           | 55   |

| 3.7 B/D for data sending operation from FPGA to PC           | 55   |

| 3.8 B/D for receiving the data on LED of rx board            | . 55 |

| 3.9 B/D for data tx b/w STM 32 m/c and FPGA                  | . 58 |

| 3.10 B/D for data Exchange between two BASYS 3 board         | 58   |

| 3.11 B/D for Implementation of ALU operations                | 58 |

|--------------------------------------------------------------|----|

| 3.12 B/D to Implement add operation using adder IP           | 60 |

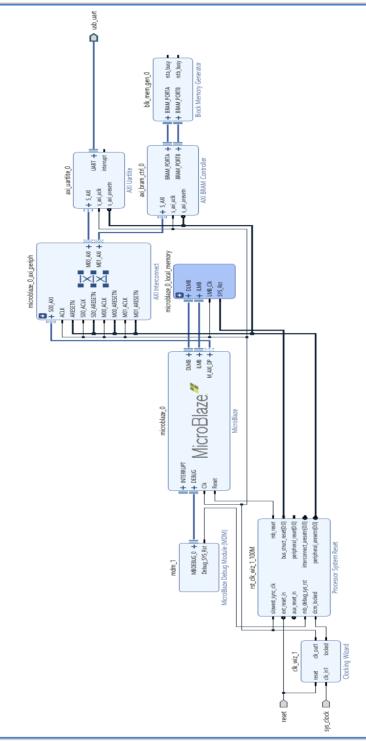

| 3.13 B/D to realize Data tx and rx using ZYNQ board          | 60 |

| 3.14 Code section                                            | 63 |

| Chapter 4 Results and Discussion                             | 78 |

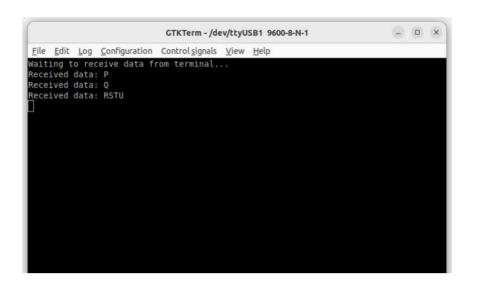

| 4.1 Results (data sent)                                      | 78 |

| 4.2 Results (data received)                                  | 78 |

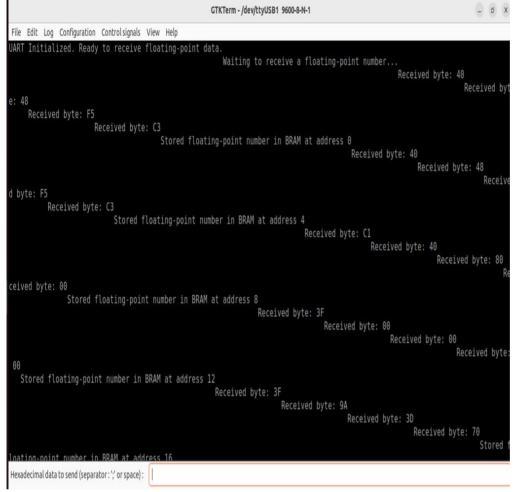

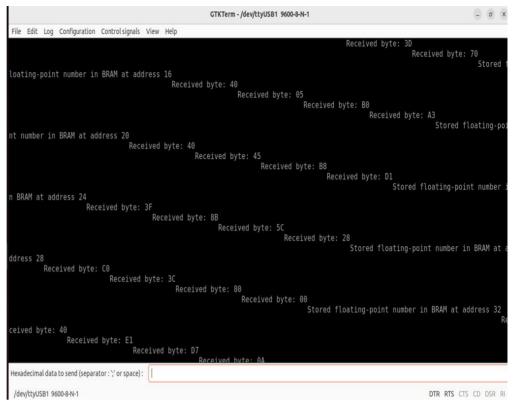

| 4.3 Data storage in BRAM                                     | 81 |

| 4.4 Results for Interboard Communication                     | 84 |

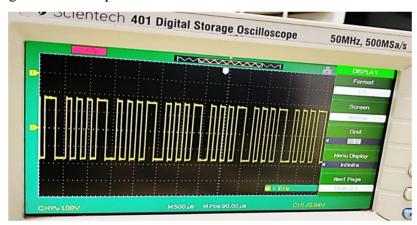

| 4.4.1 Data sent from FPGA to DSO                             | 84 |

| 4.4.2 Data tx from STM 32 to FPGA                            | 85 |

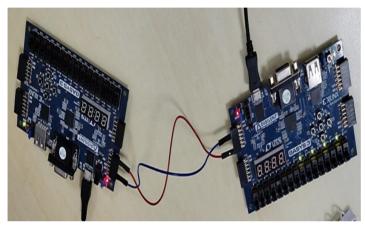

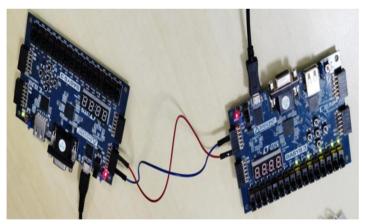

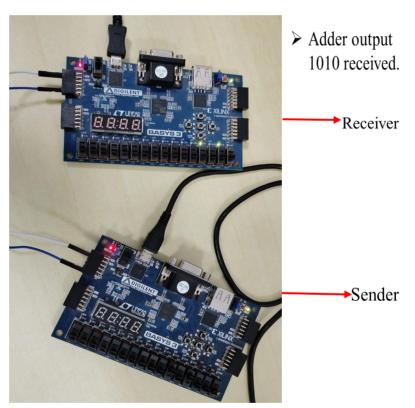

| 4.4.3 Data tx from BASYS 3 Board to BASYS 3 Board            | 86 |

| 4.4.4 Results of ALU operations without IP core              | 87 |

| 4.4.5 Results obtained using adder IP                        | 90 |

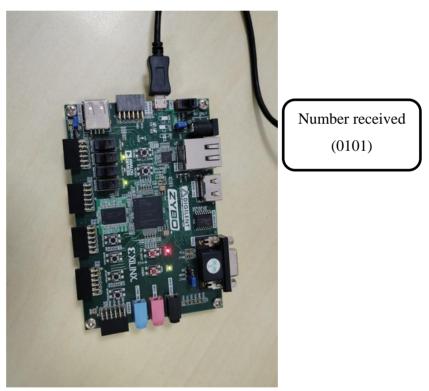

| 4.4.6 Data received on ZYNQ board from PC                    | 91 |

| 4.4.6 ZYNQ board as sender using UART Comm. Protocol         | 93 |

| 4.5 Summary of Results and Discussion                        | 94 |

| Chapter 5 Future Scope of the Project work                   | 96 |

| 5.1 Future Scope of the Project work                         | 96 |

| 5.2 Analogy b/w my Project work and MD simulation on FPGA    | 96 |

| 5.2.1 H/W Comm. and data exchange as simulation setup        | 97 |

| 5.2.2 Mem.utilization and operation execution as computation | 98 |

| 5.2.3 Interboard communication and visualization             | 98 |

| 5.3 Possible Future Extension                                | 99 |

| 5.4 Conclusion                                               | 00 |

|                                                              |    |

## **List of Figures**

| Figure    | Figure Title                                  | Page No |

|-----------|-----------------------------------------------|---------|

| No.       |                                               |         |

| Fig. 1.1  | Simplified Data Partitioning & Flow in        | 13      |

|           | Heterogeneous MD Simulation (Zynq-            |         |

|           | based platform).                              |         |

| Fig. 1.2  | Simplified Data Partitioning & Flow in        | 14      |

|           | MD Simulation (BASYS 3 with UART              |         |

|           | Communication                                 |         |

| Fig. 2.1  | Moore's Law and Performance of                | 19      |

|           | Various Computers Over Time                   |         |

|           |                                               |         |

| Fig. 2.2  | Block diagram of CPU                          | 21      |

| Fig. 2.3  | Block diagram of GPU                          | 23      |

| Fig. 2.4  | Internal architecture of FPGA                 | 24      |

| Fig. 2.5  | Block diagram of CLB                          | 25      |

| Fig. 2.6  | S-R flip flop along with S-R latch            | 26      |

| Fig. 2.7  | Multiplexer block diagram                     | 27      |

| Fig. 2.8  | Programmable I/O block                        | 28      |

| Fig. 2.9  | Block diagram of DSP                          | 29      |

| Fig. 2.10 | General flow of hardware design               | 31      |

| Fig. 2.11 | Block diagram for software design flow of FPG | A 33    |

| Fig. 2.12 | The ZYBO Zyng-7000 development board          | 35      |

| Fig. 2.13 | Digilent Basys 3 Artix-7 FPGA Board           | 37 |

|-----------|-----------------------------------------------|----|

| Fig. 2.14 | UART with Data Bus                            | 39 |

| Fig. 2.15 | UART frame of data transmission and reception | 39 |

| Fig. 3.1  | Microblaze IP Diagram                         | 44 |

| Fig. 3.2  | AXI UartLite IP                               | 45 |

| Fig. 3.3  | Constant IP                                   | 46 |

| Fig. 3.4  | AXI BRAM Controller                           | 46 |

| Fig. 3.5  | Block Memory Generator                        | 47 |

| Fig. 3.6  | AXI Interconnect IP                           | 48 |

| Fig. 3.7  | AXI GPIO IP                                   | 49 |

| Fig. 3.8  | Clocking Wizard IP                            | 50 |

| Fig. 3.9  | Adder/Subtractor IP                           | 51 |

| Fig. 3.10 | STM32 microcontroller(nucleo-L476RG)          | 52 |

| Fig. 3.11 | B/D for implementation of tx and rx           | 54 |

| Fig. 3.12 | B/D for rx to display received no. on LED     | 56 |

| Fig. 3.13 | B/D for data storage operation in BRAM        | 57 |

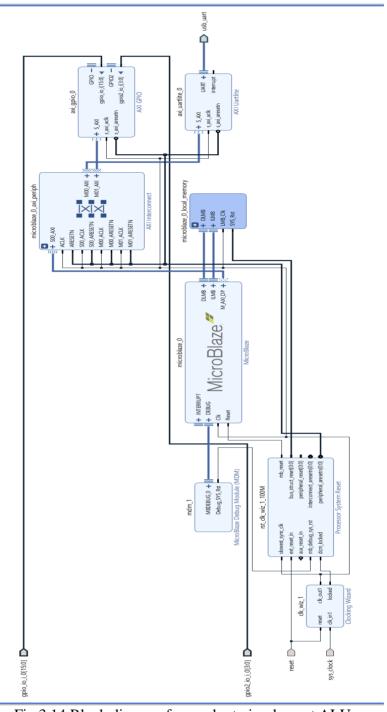

| Fig. 3.14 | B/D for sender to implement ALU operations    | 59 |

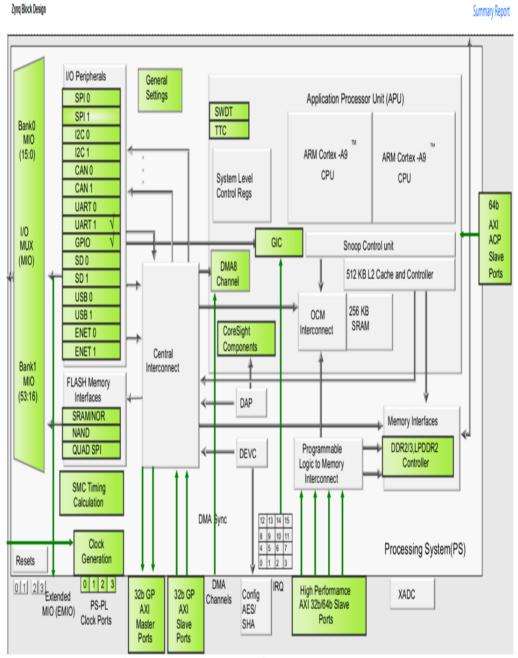

| Fig. 3.15 | Internal architecture of ZYNQ board           | 61 |

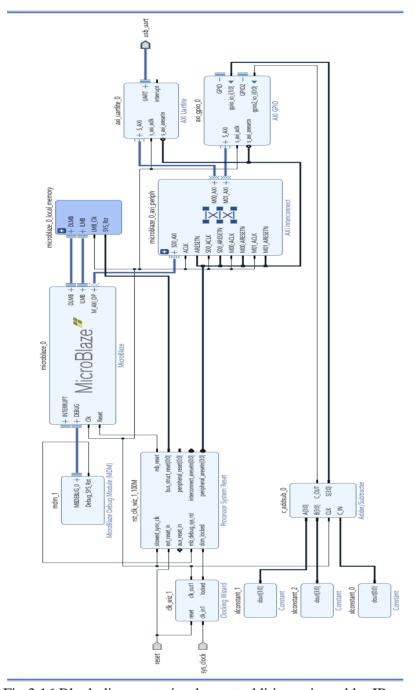

| Fig. 3.16 | B/D to implement addition using adder IP      | 62 |

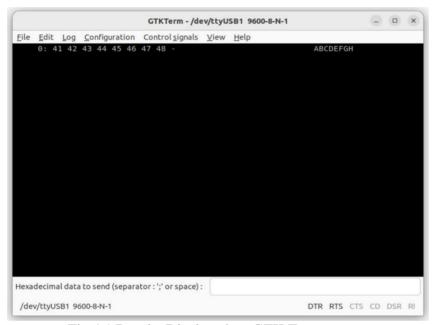

| Fig. 4.1  | Results Displayed on GTK Term                 | 78 |

| Fig. 4.2  | Results obtained on GTK term                  | 79 |

| Fig. 4.3  | Storage of Integer type data                  | 81 |

| Fig. 4.4  | Storage of Floating type data                 | 82 |

| Fig. 4.5  | Storage of Floating type data                 | 83 |

| Fig. 4.6     | DSO as Data rx from FPGA                | 84 |

|--------------|-----------------------------------------|----|

| Fig. 4.7     | Data transfer between STM32 and BASYS 3 | 85 |

| Fig. 4.8     | BASYS 3 as sender and receiver          | 86 |

| Fig. 4.9     | BASYS 3 as sender and receiver          | 86 |

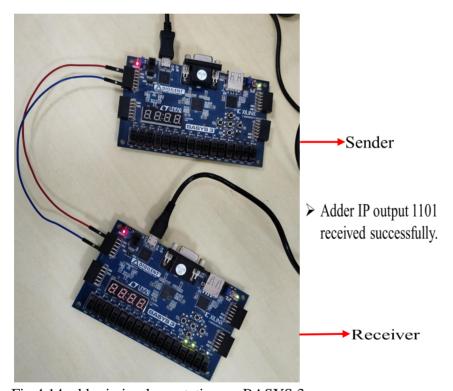

| Fig. 4.10    | Add operation on BASYS 3 board          | 87 |

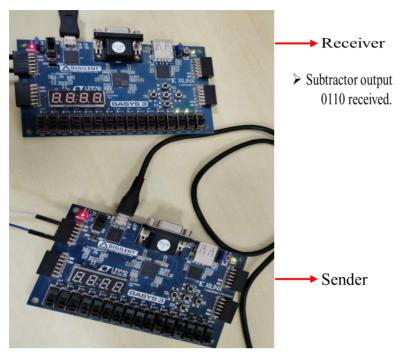

| Fig. 4.11    | Sub operation on BASYS 3 board          | 88 |

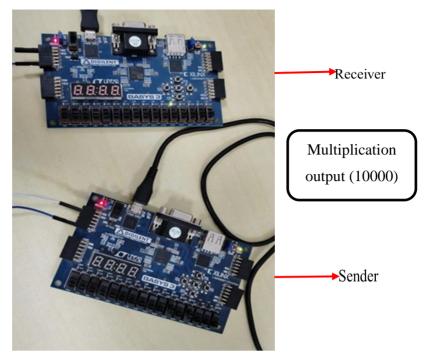

| Fig. 4.12    | MUL. operation on BASYS 3 board         | 89 |

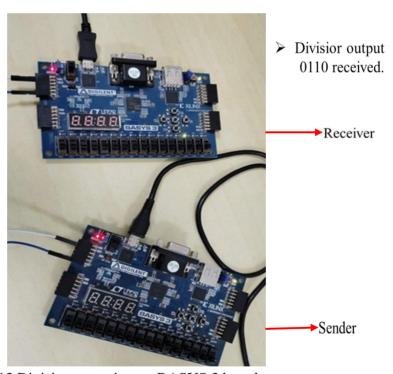

| Fig. 4.13    | Div. operation on BASYS 3 board         | 89 |

| Fig. 4.14    | Adder IP operation on BASYS 3 board     | 90 |

| Fig. 4.15    | ZYNQ board as rx                        | 91 |

| Fig. 4.16    | ZYNQ board as rx                        | 90 |

| Fig. 4.17    | ZYNQ board as rx                        | 92 |

| Fig. 4.18    | ZYNQ board as tx                        | 93 |

| Fig. 5.1 Bl  | ock diagram for MD simulation           | 97 |

| Fig. 5.2 H/V | V S/W prototype for MD simulation       | 99 |

### **List of Tables**

| Table No.  | Table Title                             | Page No. |

|------------|-----------------------------------------|----------|

| Table no 1 | (For received data)                     | 79       |

| Table no 2 | (To send data)                          | 79       |

| Table no 3 | For the displayed value on GTK term     | 82       |

| Table no 4 | For the stored values shown on GTK term | 83       |

|            |                                         |          |

### **ACRONYMS**

**HPC--High Performance Computing**

**CPU--Central Processing Unit**

GPU-- Graphics Processing Unit

ASIC-- Application Specific Integrated Circuit

FPGA- Field Programmable Gate Array

MD- - Molecular Dynamics

IP—Intellectual Property

CLB—Configuration Logic Block

LUT—Look Up Table

MUX-Multiplexer

HDL—Hardware Description Language

AXI—Advance Extensible Interface

HLS—High Level Synthesis

RISC—Reduce Instruction Set Computer

IAP—Interatomic Potential

DSP—Digital Signal Processing

PCIe—Peripheral Component Interconnect Express

UART-- Universal Asynchronous Receiver-Transmitter

DSO—Digital Storage Oscilloscope

SRAM—Static Random-Access Memory

IO—Input Output

GPIO—General Purpose Input Output

SDK—Software Development Kit

BRAM—Block Random Access Memory

DDR-- Double Data Rate

SPI-- Serial Peripheral Interface

**IC- Instruction Cache**

DC-- Data Cache

FIFO-- First In First Out

MIG-- Memory Interface Generator

RTL--Register Transfer Level

B/D—Block Diagram

### Chapter 1

### Introduction

#### 1.1 Background and Motivation

In today's world, the need to understand matter at the atomic and molecular level is of paramount importance. From designing next-generation materials and drugs to building effective energy storage systems [1] and knowledge of biological processes [2], the behavior of systems at the molecular level explains innumerable technological and scientific advances. Many of the critical issues in modern science, including developing cancer treatments, building lightweight and durable materials, or maximizing catalysts [3] for green energy, require a deep understanding of how atoms and molecules interact over time.

However, direct observation of atomic-scale phenomena is difficult due to limitations in the existing experimental techniques. While tools like X-ray crystallography and electron microscopy provide structural insights, they are often static or averaged over time, and may not capture dynamic processes such as molecular folding, diffusion, or reaction pathways. Additionally, experimental investigations at this scale are often expensive, time-consuming, and limited in scope.

To complement and sometimes even replace physical experimentation, computational methods have emerged as powerful tools for probing molecular systems. Among these, Molecular Dynamics (MD) simulation [4] stands out as one of the most widely used techniques. By numerically modeling the physical laws that govern atomic interactions, MD simulations allow researchers to investigate how molecular systems evolve under different conditions. This enables the scrutiny of structural,

thermodynamic, and kinetic aspects of systems whose access would otherwise be confined experimentally.

#### 1.2 A Brief Introduction to MD Simulation

An important tool in computational science, molecular dynamics (MD) simulation is used widely to examine the physical movements of atoms and molecules. The numerical solution of Newton's equations of motion[5] for a system of interacting particles it enables researchers to look into intricate physical systems at the atomic level. In domains where understanding molecular interactions and predicting system behavior under diverse circumstances are essential, such as materials science, chemistry, biology, and nanotechnology, MD simulations are essential.

MD simulations are well-known for being computationally demanding, particularly when working with large systems or lengthy simulation times, despite their scientific value. Since some computation tasks are inherently sequential and require massive data throughput, traditional CPU-based platforms frequently struggle to deliver real-time or high-throughput performance. The need for faster and more effective computing solutions is increasing along with the demand for longer and more detailed simulations.

Heterogeneous computing platforms[6] have become a viable remedy for these constraints. These platforms combine hardware accelerators like Graphics Processing Units (GPUs) and Field-Programmable Gate Arrays (FPGAs) with general-purpose CPUs (CPUs). Because of their low latency, energy efficiency, and adaptable hardware architecture, FPGAs provide a distinct advantage over the others. FPGAs can be specifically designed to speed up the computational kernels of MD algorithms, potentially resulting in significant performance gains, in contrast to GPUs, which have a fixed architecture optimized for high-throughput parallelism.

Here we investigate how to speed up MD-based simulations by designing and implementing a heterogeneous computing platform that uses FPGAs. We hope to show how accuracy can be maintained while performance and energy efficiency are increased by offloading crucial computational functions, like force calculations and Neighbour list updates, onto an FPGA. In addition to contributing to the continuous endeavor to speed up MD simulations, this work sheds light on the practical challenges and architectural compromises associated with FPGA-based hardware acceleration for scientific computing.

## 1.3 Computational challenges in MD simulation

The high computational cost of Molecular Dynamics (MD) simulations frequently limits their practical application, although they offer rich insights into molecular behavior. On conventional CPU-based platforms, it can take days or weeks of computation to simulate even a few nanoseconds of real-time dynamics for a system with thousands or millions of atoms. This is because MD simulations require the computation of forces resulting from all pairwise and bonded interactions as well as the repetitive numerical integration of particle motion, both of which must be completed at each femtosecond-scale time step.

The number of particles and interactions that need to be calculated increases quickly with the complexity of the systems being studied, such as biomolecular assemblies, polymer blends, or nanostructured materials. The simulation burden may also be increased by coarse-grained models, long-range electrostatics, or more complex force fields. Because of this, researchers must frequently choose one of the three trade-offs—accuracy, system size, and simulation length—to maintain realistic runtimes.

The computing community has increasingly resorted to heterogeneous computing platforms, which combine general-purpose CPUs with specialised accelerators like Graphics Processing Units (GPUs) and Field-Programmable Gate Arrays (FPGAs), in order to get around these bottlenecks. Although GPUs have already shown significant speedups for MD tasks by performing force calculations in parallel, FPGAs provide a special and frequently overlooked benefit: hardware-level customizability.

The design and implementation of a heterogeneous computing platform that uses FPGAs to speed up MD-based simulations is examined in this thesis. Our goal is to show how accuracy can be maintained while performance and energy efficiency are increased by offloading crucial computational functions, like force calculations and neighbour list updates, onto an FPGA. In addition to adding to the continuous endeavour to speed up MD simulations, this work sheds light on the real-world difficulties and architectural compromises associated with FPGA-based hardware acceleration for scientific computing.

#### Why FPGAs?

With Field-Programmable Gate Arrays (FPGAs), designers can configure up the hardware exactly according to the computational problem's structure. FPGAs can be programmed to implement custom pipelines and parallel data paths for particular algorithms, in contrast to CPUs and GPUs, which function with fixed instruction sets and general-purpose pipelines. This makes it possible to execute MD kernels with significantly reduced latency and power consumption, including Neighbour generation, non-bonded force evaluation, and particle updates.

FPGAs are especially appealing for uses like embedded systems, portable medical devices, and massive data centers where real-time performance and energy efficiency are crucial. This implies that simulations

can be extended to longer periods or larger systems in the context of MD while still requiring a manageable amount of computing power.

Moreover, it is now more possible to incorporate FPGAs into heterogeneous computing architectures alongside CPUs and GPUs thanks to recent developments in high-level synthesis (HLS) tools and FPGA development platforms. This creates new possibilities for offloading the most time-consuming portions of MD simulations to FPGAs, increasing speed and energy efficiency without compromising accuracy or flexibility.

## 1.4 Heterogeneous Computing for MD Simulations

Utilizing the strengths of each component, a heterogeneous computing platform combines various processing unit types, usually CPUs, GPUs, and FPGAs, to carry out tasks collectively. This architectural model offers an effective approach to handle the algorithm's various computational requirements in the context of MD simulations more effectively than any particular processor type can.

## MD simulations consist of multiple tasks, each with unique computational properties:

- Force calculations are parallelizable and computationally difficult, especially for non-bonded interactions such as Lennard-Jones or Coulomb forces.

- Creating neighbour lists necessitates memory-intensive processes like sorting and spatial data structures.

- The process of integrating motion equations is comparatively simple and has a consistent pattern.

- Restriction enforcement and boundary conditions are less appropriate for parallel execution and may call for conditional logic.

- High-level control logic, preprocessing, and data flow coordination are the tasks that CPUs are best suited for.

- Massively parallel tasks, like calculating pairwise forces across numerous particles at once, are a strength of GPUs.

FPGAs are perfect for offloading bottleneck tasks that benefit from special data flow and parallelism because they can be set up to run particular computational kernels (such as cell list updates or short-range force evaluation) with deep pipelining, low latency, and high throughput.

Heterogeneous systems can handle larger or more complex models, improve energy efficiency, and drastically cut down simulation runtime by dividing MD tasks among these units. For example, an FPGA can continuously compute non-bonded interactions in real time, offloading one of the most burdensome operations from the CPU/GPU and enabling better overall throughput, whereas a CPU might handle simulation setup and output.

As demonstrated by hybrid MD packages that employ GPUs for force calculation or specialized FPGA-accelerated modules integrated into HPC clusters, recent research and industrial tools have started adopting such architectures. These developments pave the way for wider use and additional simulation acceleration innovation.

## 1.5 Perspective on Heterogeneous FPGAbased Computing Platforms

The overarching goal of this thesis is to explore and demonstrate the use of FPGA-based acceleration within a heterogeneous computing platform to improve the performance and energy efficiency of MD-based simulations.

## 1.5.1 A Study of Heterogeneous Computing Platforms Based on FPGA

The term "heterogeneous computing platform" presumes a more expansive meaning in this work; it not only describes a combination of processing components, such as CPUs and FPGAs, cooperating, but it also describes the actual implementation of FPGAs on various hardware platforms with different architectural characteristics. The implementation examines at platforms like the Zynq-7000 series, which combines ARM processors (Processing System, or PS) and programmable logic (PL) on a single chip, allowing for deeper hardware-software co-design, and the Basys 3 board, which offers a simple, lightweight FPGA fabric (perfect for testing core logic).

#### 1.5.2 Advantages of FPGA

Because of its ease of use and accessibility for quick prototyping, the Basys 3 Board (Artix-7 FPGA) is appropriate for implementing and validating basic hardware accelerators (such as force calculators and integrators).

A dual-core ARM processor and programmable logic are combined in the Zynq Series (such as Zed Board or ZCU boards), enabling close integration between hardware (custom logic in PL) and software (running on ARM). For full-stack MD implementations, where control logic, memory management, and data streaming can all be optimised simultaneously, this is especially advantageous.

PC-FPGA configurations: Simulating a real-world heterogeneous setup between high-level MD engines and low-level accelerators, simulation tasks can be offloaded to an FPGA and results returned asynchronously when the FPGA is connected to a host PC via interfaces such as UART, USB, or PCIe.

This perspective is important since MD accelerator deployment in the real world is rarely confined to a single, consistent platform. Smaller FPGAs are often used for kernel development in research and practical development, followed by embedded SoCs like Zynq for tighter integration and, ultimately, scaling to datacenter-grade FPGAs or hybrid cloud-based systems. This work investigates several boards, assessing not only acceleration potential separately but also portability, design reusability, and device-to-device performance scaling—all critical attributes for future MD hardware engines.

Therefore, this illustrates a platform-aware heterogeneous computing vision by showing how FPGAs deployed in various configurations — from academic prototypes to embedded systems — can gradually accelerate MD simulations and how these setups individually and collectively contribute to faster, more efficient molecular simulations.

#### 1.6 What are kernels?

In simple terms, a kernel in this context refers to a self-contained, reusable block of computation — a small part of a larger algorithm that performs a specific task. In Molecular Dynamics (MD) simulations, kernels are the core units of computation that are repeated many times.

So, when we say: "Identifying which kernels are best suited for FPGA acceleration". It means figuring out which parts of the MD simulation (like force calculation or neighbor list building) can be broken out and then efficiently run on the FPGA to speed up the simulation.

#### **Examples of MD kernels:**

- Force calculation kernel calculates the interaction forces between pairs of atoms.

- Neighbor list kernel builds a list of nearby atoms for each particle.

• Integration kernel – updates particle positions and velocities using algorithms like Verlet integration.

These are considered "kernels" because they run many times (often millions of iterations). They are compute-intensive. They can often be separated from the rest of the code and offloaded to a specialized processor (like an FPGA or GPU).

Kernels Well-Suited for FPGA Acceleration in MD Simulations. example:

#### a) Non-Bonded Force Calculation (e.g., Lennard-Jones Potential)

Why is it suitable?

- It's repetitive, parallelizable, and has regular arithmetic.

- FPGA advantage: Can be pipelined to compute forces between many atom pairs in parallel.

- Implementation: Use fixed-point or reduced-precision floating-point on Basys 3 or Zynq PL.

#### b) Neighbor List Construction

Why is it suitable?

- It involves spatial searches, but can be optimized via cutoff distance checks.

- FPGA advantage: Efficient at comparing many distances in parallel using loop unrolling.

- Implementation: Suitable for Zynq boards with more BRAM for storing coordinates.

#### c) Verlet Integration/Time stepping

Why is it suitable?

- A small, deterministic loop for updating position and velocity.

- FPGA advantage: Can be a pipelined arithmetic block, ideal for Basys3.

- Implementation: Use block RAMs to store positions, update in-place with minimal latency.

#### d) Constraint Solvers

Why is it more complex?

- These often involve iterative solvers and are harder to pipeline.

- FPGA suitability: Only partially suitable unless highly optimized, more fitting for Zynq.

#### **Strategy Based on Platform:**

- 1) Basys 3: Ideal for developing and testing smaller, arithmetic-heavy kernels like Verlet integration or a simple Lennard-Jones force loop.

- 2) **Zynq:** Ideal for building end-to-end MD pipelines, combining an ARM processor (for control) and PL (for force calculation + neighbor list).

#### 1.7 Partitioning

Partitioning: A key concept in realizing the actual purpose of heterogeneous computing.

#### What is Data Partitioning?

Data partitioning refers to dividing the simulation data into smaller, manageable chunks that can be distributed across different compute resources, like FPGA fabric and CPUs, to enable parallel processing.

#### Why is It Important in Heterogeneous Platforms?

In a heterogeneous system (e.g., ARM CPU + FPGA), each component has strengths

- FPGA: Excellent at parallel and pipelined arithmetic tasks. Ideal for computing interactions, applying forces, or processing multiple atom pairs in parallel.

- CPU (ARM or Host): Better at handling complex logic, control flow, file I/O, or memory allocation tasks.

#### By partitioning the data effectively, we can

- Offload only the high-compute, parallel parts (e.g., force calculations) to the FPGA.

- Keep control and orchestration (e.g., managing simulation steps or writing results) on the CPU.

- Avoid idle hardware maximize hardware utilization.

- Reduce memory bottlenecks process data in-place on the right unit.

#### **How It Applies to MD Simulations**

- Let's take a practical example:

- Suppose you're simulating a system with N particles. You typically need to:

- Loop over all particle pairs to compute forces.

- Update positions/velocities.

- Rebuild neighbor lists every few steps.

#### Without Data Partitioning:

- All data resides in CPU memory.

- The CPU runs all calculations serially or via software loops.

- FPGA is underutilized (if used at all).

- Bottleneck: Single memory interface, no hardware acceleration.

#### With Data Partitioning:

• Divide the particle list into smaller blocks (e.g., blocks of 64 or 128 atoms).

- Each block is sent to the FPGA via AXI4 or UART for force computation.

- The CPU keeps track of time steps, boundary conditions, etc.

- Overlap computation on FPGA with neighbor list rebuilding on CPU.

#### **Types of Partitioning Approaches:**

- a) Spatial Partitioning: Divide the simulation space (e.g., a 3D box) into regions. Assign different regions to different units.

- FPGA processes atoms in region A.

- The CPU handles region B or overall orchestration.

- Helpful in simulations with millions of particles.

- b) Functional Partitioning: Divide the simulation tasks (not space).

- FPGA: Force calculation and position updates.

- CPU: Neighbor list updates, output logging, temperature scaling.

- c) Temporal Partitioning: Assign different time steps or intervals to different units.

- While FPGA processes the current step, CPU prepares the next input.

## Benefits of Data Partitioning: Especially on platforms like Basys 3 or Zynq.

- **Basys 3**: Limited memory, but perfect for functional partitioning of one kernel at a time (e.g., force calc).

- **Zynq** (**ARM** + **PL**): Enables true hardware/software co-design perfect for both spatial and functional partitioning.

#### **Data partitioning:**

- Reduces latency by enabling in-place computation on an FPGA.

- Minimizes data movement process data where it resides.

- Scales better more logic = more blocks processed in parallel.

- Makes the MD accelerator modular and portable.

#### **Summary**

- Data partitioning is not just about splitting data it's about smart delegation:

- Sending the right kind of data to the right hardware at the right time.

- Enabling both CPU and FPGA to work in parallel and avoid idle time.

- Essential for scaling MD simulations across heterogeneous platforms, like a Basys 3 prototype and a Zynq deployment.

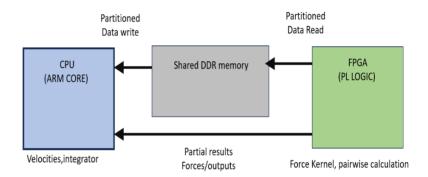

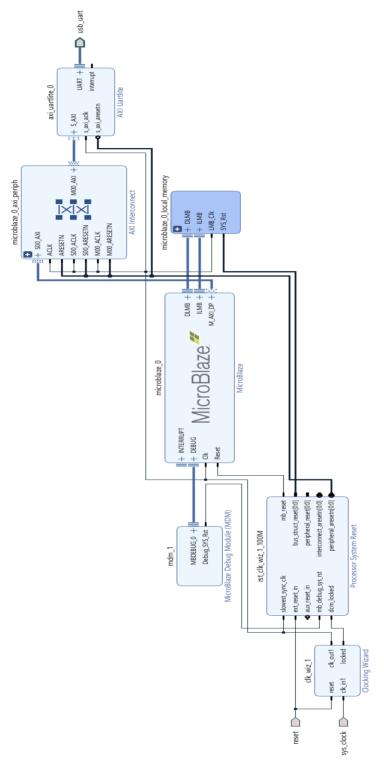

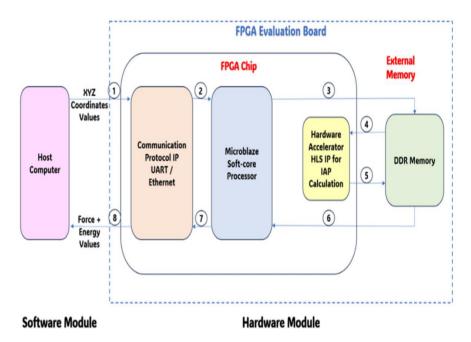

**Fig.1.1** Simplified Data Partitioning & Flow in Heterogeneous MD Simulation (Zynq-based platform)

Here's a block diagram that illustrates how data partitioning enables efficient MD simulation on a heterogeneous platform like the Zynq board:

#### Key Concepts in the Diagram:

The CPU (ARM Core) handles velocity updates, integration (Verlet Algorithm), and control and orchestration at the same time, FPGA (Programmable logic) accelerates the process of pairwise calculations and distance check. Shared DDR memory holds partitioned data sets (positions, forces), and it acts as a communication buffer between the CPU and the FPGA.

This architecture allows concurrent processing of MD tasks, maximizing both performance and energy efficiency.

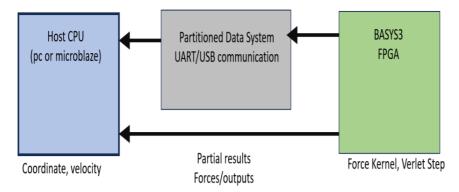

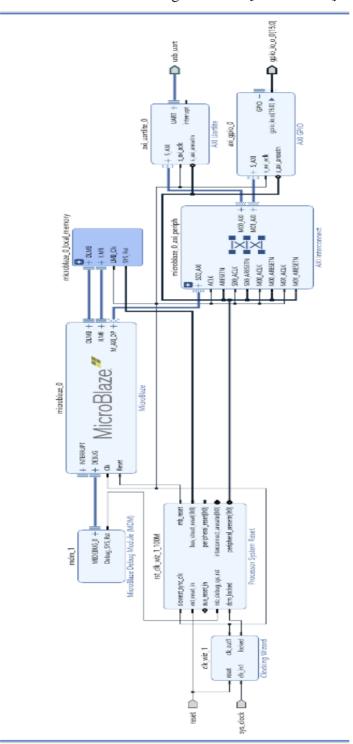

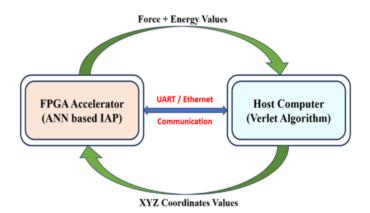

**Fig.1.2** Simplified Data Partitioning & Flow in MD Simulation (BASYS 3 with UART Communication

Here is the block diagram showing data partitioning and flow for MD simulation on the Basys 3 board, where communication is handled via UART or USB instead of shared memory

Host CPU / MicroBlaze Prepares simulation data (positions, velocities) and sends it to the FPGA via UART.it also receives result back (computed forces). FPGA mainly focused on force computation and numerical integration and it operates in real time as the data arrives

#### **Why This Matters**

It allows MD simulation on low-cost hardware (Basys 3).it demonstrates the feasibility of FPGA- based acceleration even without a full OS or shared memory. Efficient data partitioning enables a clear division of responsibilities between host and the FPGA.

#### 1.8 Conclusions

While Molecular Dynamics (MD) simulations have become essential across scientific disciplines, they remain constrained by performance bottlenecks, especially when scaling to large systems or simulating long time durations. Although GPUs have accelerated MD algorithms to a degree, they remain limited by fixed architectures and

inefficient memory access patterns for certain irregular tasks. FPGAs, despite their flexibility and performance potential, are underutilized in mainstream MD applications. Most existing implementations rely heavily on CPUs and GPUs, overlooking how FPGAs could be strategically integrated into heterogeneous systems to accelerate specific, high-impact parts of the MD pipeline, such as non-bonded force computations, neighbor list generation, and bonded interactions, with lower power and potentially higher throughput for certain workloads.

However, integrating FPGAs into MD simulation workflows presents several challenges: Identifying which kernels are best suited for FPGA acceleration, efficiently partitioning workloads between CPU, GPU, and FPGA, managing data flow and synchronization across heterogeneous components, and evaluating trade-offs between performance, energy efficiency, and resource utilization

This thesis aims to address these challenges by exploring a heterogeneous computing platform that executes a simple mathematical operation on a smaller prototype IP—serving as a foundation that can be scaled to more complex IPs—while integrating FPGA acceleration into the MD simulation process to enable optimized task scheduling and efficient data distribution across multiple processing units.

#### 1.9 Objective

- 1) To explore potential scalability to multi-FPGA or CPU-GPU-FPGA systems, demonstrating the viability of FPGA acceleration in broader high-performance computing (HPC) contexts for MD.

- 2) To integrate these FPGA modules within a CPU-FPGA heterogeneous computing framework, ensuring seamless communication, task delegation, and memory consistency to ensure hardware control as well as easy debugging of the given system.

3)Implement the simple ALU operations in the FPGA-FPGA-based system using UART communication protocol, which will later translate into a complex MD simulation by using a larger IP framework.

#### 1.10 Organization of the Thesis

The thesis will be divided into five chapters, and in each chapter, the generic flow of content representation will be as follows: the **first chapter** will provide a brief introduction of the background and motivation behind the given research work and all the elements associated with it. As we move ahead into the **second chapter**, this module explores the theoretical fundamentals and literature survey required to develop a system that can imitate the FPGA Accelerator for IAP-based MD Simulation. Subsequently, **the third module** will give the details of the hardware and software development and implementation of different operations involved, and interboard communication to realize the final work. The **fourth chapter** will discuss the various results obtained after the real implementation of the system. Finally, as we reach into the final phase of the Thesis, that is, **chapter five**, this module delves into the possibilities of future work and the large-scale implementation of the existing project work.

### **Chapter 2**

#### **Literature Review**

These three metrics—throughput, latency, and timing—are essential for assessing and improving system performance in the larger High-Performance Computing (HPC) framework. The goals of HPC platforms, which frequently combine CPUs, GPUs, and FPGAs in heterogeneous architectures, are to optimize throughput for processing large amounts of data, reduce latency for responsiveness in real time, and make sure that designs adhere to stringent timing requirements for dependable operation at high clock frequencies. Specifically, when FPGAs are used in an HPC environment, they are used to speed up data-intensive kernels by taking advantage of their built-in parallelism and pipelining features, which have a direct effect on latency and throughput. Furthermore, satisfying timing constraints in FPGA designs guarantees that these accelerators can operate at ideal clock frequencies without going against setup or hold specifications, maintaining the high-speed performance required for HPC workloads like deep learning inference, scientific computing, and molecular dynamics simulations. High-throughput architectures are designed to maximize the number of bits processed per second, while low-latency architectures aim to minimize the time delay between the input and output of a module. At the same time, timing optimizations focus on reducing the combinatorial delay along the critical path to ensure the design meets its target clock frequency

As discussed above, the three main components that decide how fast any computing machine will perform are **THROUGHPUT**, **LATENCY**, and **TIMING OPTIMIZATIONS**. Now, it will be discussed how these metrics play a key role in high-performance computing.

#### 2.1 High throughput

A design focused on high throughput prioritizes maintaining a continuous and efficient flow of data over time. It aims to maximize the overall data processing rate, placing less emphasis on how long it takes for an individual data element to travel from input to output (latency).

#### 2.2 Low Latency

A low-latency design focuses on transferring data from input to output in the shortest possible time by reducing delays in intermediate stages. To achieve this, techniques such as parallel execution, pipelining, and simplified logic are often employed, even if they might compromise the design's throughput or limit its peak operating frequency.

#### 2.3 Timing

Timing in a digital design refers to its operating clock frequency. This frequency is fundamentally constrained by the longest delay between any two sequential components, which sets an upper bound on how fast the clock can run. Unlike broader speed/area trade-offs covered in other parts of this chapter, clock speed operates at a more fundamental level of abstraction and isn't inherently tied to specific architectural choices. However, the internal decisions made within a particular architecture, such as how resources are organized, do influence timing performance. For instance, determining whether a pipelined architecture outperforms an iterative one in terms of speed requires detailed insight into the actual implementation. The design's peak performance or maximum operating frequency can be described using the standard minimum-frequency formula, excluding factors like clock-to-clock jitter.

$$F_{max} = \frac{1}{T_{clk-q} + T_{logic} + T_{routing} + T_{setup} - T_{skew}}$$

(2.1)

In Eqn 2.1, **Fmax** is the **maximum allowable frequency** for the clock; T clk-q is the time from clock arrival until data arrives at Q; T-logic is propagation delay through logic between flip-flops; Trouting is routing delay between flip-flops; Tsetup is minimum time data must arrive at D before the next rising edge of clock (setup time); and Tskew is propagation delay of clock between the launch flip-flop and the capture flip-flop.

## 2.4 Evolution in High-Performance Computing (HPC)

HPC covers all aspects of technology, methodologies, and applications aimed at achieving the maximum computing capability possible using clusters of powerful processors. These processors work simultaneously to handle large-scale multi-dimensional datasets, often referred to as big data, and to solve complex problems at very high speeds. The primary goal of HPC is to provide solutions to questions that cannot be adequately addressed solely through empirical methods, theory, or commercially available computers. The most visible components of HPC are high-performance computers, commonly known a supercomputers, which occupy large areas and consume significant power.

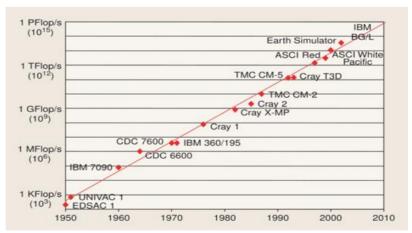

**Fig.2.1** Moore's Law and Performance of Various Computers Over Time.

Moore's law states that processor performance approximately doubles every 18 months. HPC performance is typically measured by two fundamental metrics: "Time" and "Number of operations". The most commonly used metric in HPC is "floating point operations per second" or "flops". These measurements include thousands (KFLOPS), millions (MFLOPS), billions (GFLOPS), trillions (TFLOPS), and quadrillions (PFLOPS) of floating-point operations executed per second, representing increasing levels of computational performance. Fig. 2.1 clearly illustrates the consistent trend of Moore's Law, which has held throughout much of the modern computing era, with performance increasing by approximately two orders of magnitude every decade. This ongoing advancement continues to push the boundaries of computing technology. However, as Moore's law slows down and manufacturing reaches physical limits, managing heat and power becomes increasingly challenging due to higher processor speeds and core counts. In response to evolving user needs and power constraints, heterogeneous computing platforms have emerged as a viable solution. FPGA emerged as the best solution among all the heterogeneous computing platforms due to its parallel processing capabilities.

#### **2.5 CPU**

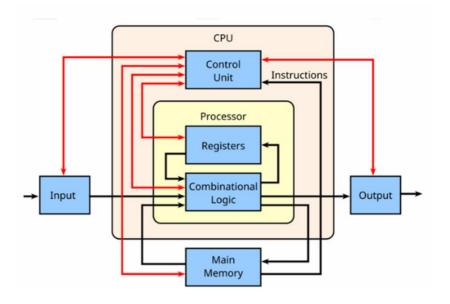

The Central Processing Unit (CPU) acts as the core of a computer system, executing program instructions by handling basic tasks like arithmetic calculations, logical decisions, control functions, and input/output operations. It processes information and oversees the functioning of all other hardware components. A basic CPU block diagram illustrates key units including the Arithmetic Logic Unit (ALU), the Control Unit (CU), internal registers, and data buses. These components collaborate to execute operations, manage control signals, and handle the movement of data within the processor.

Fig.2.2 Block diagram for CPU

## **2.6 GPU**

A graphical processing unit, or GPU, is a type of specialized processor that is mainly used for image and graphics processing. A GPU is designed to execute numerous basic computations simultaneously, which makes it perfect for tasks requiring massive parallel processing, as opposed to a CPU, which is optimized for general-purpose tasks.

The GPU performs parallel processing by using hundreds or thousands of small cores to handle many operations at once. It is responsible for graphics rendering, originally built to manage images, videos, and animations for visual display. Today, it is also widely used for data acceleration in fields like scientific computing, AI, and machine learning, enabling faster execution of large-scale mathematical tasks. Additionally, the GPU supports the CPU by offloading repetitive and computation-heavy operations, improving overall system performance.

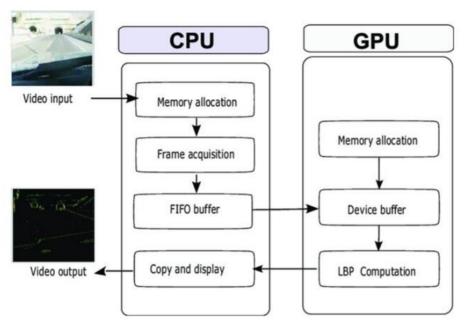

The general block diagram, which depicts the basic functionality of the GPU, is given below:

Fig.2.3 Block diagram of GPU

## **2.5 FPGA**

FPGAs (Field-Programmable Gate Arrays) are customizable digital logic devices that can be programmed to perform any specified hardware function. They are built using a matrix of configurable elements (such as logic blocks, I/O modules, etc.) that are connected using built-in wiring channels and adjustable switches. The operations of these blocks and interconnections are governed by millions of SRAM (Static RAM) cells, which are loaded with configuration data during initialization to define the intended behavior. Users define this behavior using a hardware design language like VHDL or Verilog, or alternatively, leverage high-level synthesis (HLS) tools to convert code written in languages like C or OpenCL into HDL form. The HDL is then compiled through a sophisticated electronic design automation (EDA) toolchain into a binary bitstream that programs the configuration memory of the FPGA.

In contrast to designing a custom application-specific integrated circuit (ASIC), FPGAs provide much lower upfront development costs and a faster path to deployment. By utilizing readily available off-the-shelf FPGA hardware, an entire system can be built in a matter of weeks, eliminating the need for extensive physical design, layout, manufacturing, and validation typically required for ASICs. Additionally, FPGAs support easy post-deployment hardware modifications by loading a new bitstream in the field—hence the term "field-programmable." This capability makes FPGAs especially appealing for small to medium-sized projects, particularly in markets with rapid product evolution. These advantages have driven FPGA adoption across domains like wireless systems, embedded processing, data networking, ASIC emulation, and high-speed financial trading.

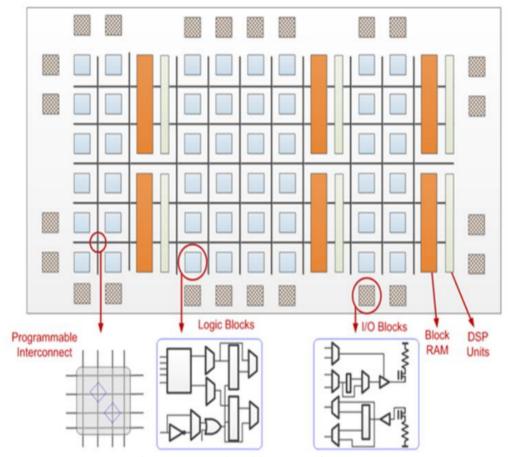

#### 2.5.1 Internal architecture of FPGA

The internal architecture of an FPGA is composed of many blocks as follows: the Configurable Logic Blocks (CLBs) serve as the central units for computation, containing lookup tables (LUTs), flip-flops, and multiplexers to perform both combinational and sequential logic operations. Surrounding these are Input/Output Blocks (IOBs), which handle data transfer between the FPGA and external components by supporting various I/O protocols. These blocks are interconnected through a **programmable** routing network, a flexible mesh of wires and switches that define the signal paths across the chip. To ensure proper timing and synchronization, clock management resources such as **phase-locked loops** (PLLs) and clock distribution trees are embedded in the architecture. The FPGA also includes **Block RAM (BRAM)** for fast, on-chip data storage and buffering, and **DSP** slices, which are specialized for high-speed arithmetic operations like multiplication and accumulation, essential for applications in digital signal processing and machine learning. At the foundation of the FPGA's reconfigurability lies the configuration memory, which stores the

programming bitstream and enables the dynamic arrangement of logic functions and routing paths, making the FPGA a highly flexible and adaptable platform for a variety of digital applications.

Fig.2.4 Internal architecture of FPGA

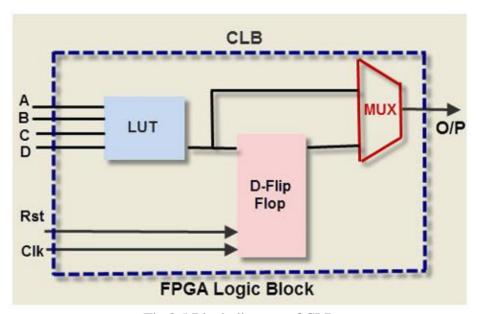

### **Configurable Logic Blocks (CLB)**

A CLB is the core component of an FPGA, enabling it to adopt various hardware setups. Essentially, an FPGA is comprised of numerous CLBs, forming its structure. With thousands of these on modern FPGAs, they can be programmed to execute nearly any logical operation. Each CLB contains its own set of discrete logic elements, including look-up tables (LUTs), multiplexers, and flip-flops. The configurable logic block general diagram is shown below

Fig.2.5 Block diagram of CLB

## 1) Look up table

The Lookup Table (LUT), a pivotal element within the CLB of an FPGA, serves as a cornerstone for its functionality. It operates as a customizable truth table, associating input configurations with corresponding output values. LUTs possess programmable capabilities, enabling them to execute various combinational logic functions. Their flexibility is paramount in digital circuit design, as they empower engineers to implement diverse logic operations tailored to specific requirements. From basic logic gates to intricate functions such as adders and multiplexers, LUTs provide a versatile platform for crafting custom digital circuits, accommodating a spectrum of computational tasks with precision and efficiency.

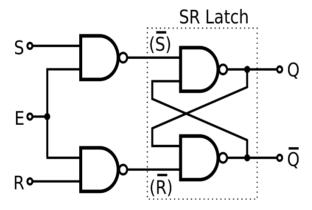

#### 2) Flip-flop or Latches

A **flip-flop** is a basic digital memory element used to store one bit of binary data. It is edge-triggered, meaning it changes its output only on the rising or falling edge of a clock signal, making it ideal for synchronous circuits. Flip-flops are widely used in sequential logic for registers, counters, and state machines.

A **latch**, on the other hand, is a level-sensitive storage device that changes its output as long as the enable signal (or control signal) is active. It is used in asynchronous circuits where data needs to be stored or held without relying on a clock edge.

Flip-flops or latches, integral components within a CLB, play a vital role in FPGA functionality by providing the capability to both store and synchronize data. Acting as memory elements, they facilitate the retention of crucial state information within the FPGA, ensuring the stability and accuracy of ongoing processes. These flip-flops or latches serve multiple purposes within the digital circuitry: they can store intermediate results during complex computations, implement sequential logic to control the order of operations, and create memory elements for temporary or permanent data storage. Their versatility enables the FPGA to manage and manipulate data streams effectively, enhancing its overall performance and functionality in various applications.

Fig.2.6 S-R flip flop along with S-R latch

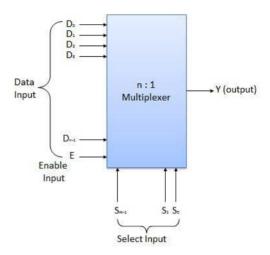

#### 3)Multiplexer (MUX)

The multiplexer (MUX) housed within a CLB is critical in managing data flow within an FPGA. It acts as a switchboard, enabling the selection of different inputs based on control signals. This capability allows signals from various sources to be routed and connected to different components within the CLB as needed. By providing this flexibility, the multiplexer

facilitates the adaptation of the FPGA to diverse operational requirements. For instance, it permits the selection of appropriate input signals for specific computational tasks or conditions, thereby enhancing the versatility and efficiency of the FPGA's operation. Additionally, the MUX is crucial in optimizing resource utilization within the CLB, ensuring that signals are efficiently directed to the appropriate destinations for processing or further routing.

Fig.2.7 Multiplexer block diagram

#### **Programmable Interconnect**

In FPGAs, routing consists of wire segments of varying lengths interconnected by electrically programmable switches. The density of logic blocks within an FPGA is influenced by the length and number of these wire segments used for routing. Balancing the number of connecting segments is crucial as it affects both the density of logic blocks and the space occupied by routing. Programmable routing links logic and input/output blocks to complete a user-defined design unit. This routing circuit comprises multiplexers, pass transistors, and tristate buffers. Pass transistors and multiplexers within a logic cluster establish connections between the logic units.

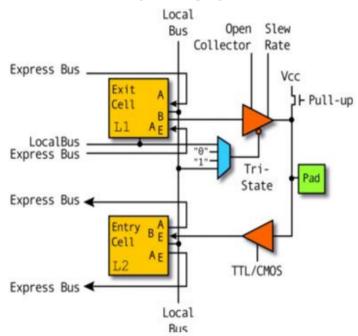

#### Programmable I/O Blocks

FPGAs feature flexible IO architectures that enable them to connect with a wide variety of devices, making them essential communication centers in many systems. Nevertheless, supporting multiple IO interfaces and standards through a single group of physical IOs poses considerable difficulties, demanding compatibility with different voltage ranges, signal properties, timing requirements, and communication protocols.

Fig.2.8 General block diagram for programmable I/O blocks

A Configurable Input/Output (I/O) Block, shown in Fig. 2.8, manages signal reception into the FPGA and signal transmission out of it. It contains input and output buffers that support control settings for three-state and open-drain modes. Usually, pull-up resistors are integrated at the outputs, while optional pull-down resistors can be added to internally terminate signals or buses, thus eliminating the requirement for external termination components. Moreover, the output polarity can be set to either active high or active low, and the slew rate can be adjusted to support either fast or slow transitions in signal rise and fall times Using flip-flops on the output side allows clocked signals to be sent directly to the output pins,

which helps minimize delays and ensures that setup time requirements for connected external devices are met. Likewise, placing flip-flops on the input side reduces the signal delay before it reaches internal logic, effectively lowering the hold time demands within the FPGA.

### Digital Signal Processing (DSP) Slice

The DSP slice, also known as a DSP block or cell, is a specialized component within an FPGA designed specifically for handling digital signal processing tasks. Unlike the more versatile Configurable Logic Blocks (CLBs), which perform a wide range of general functions, DSP slices are purpose-built to efficiently carry out operations like multiplication, filtering, and accumulation. These units come with dedicated hardware elements, including multipliers, accumulators, and specialized adders, allowing them to execute DSP functions with greater speed and lower resource usage compared to implementations using CLBs. The inclusion of DSP slices greatly strengthens the FPGA's capacity for real-time signal processing, making them essential in fields such as telecommunications, audio processing, and image and video analysis.

B<sub>i-1</sub>

DSP

B<sub>i+1</sub>

| M<sub>1</sub>

| M<sub>2</sub>

| B<sub>i+1</sub>

| M<sub>1</sub>

Fig.2.9 Block diagram of DSP

**Block Random Access Memory (BRAM)**

Block RAM (BRAM) is the on-chip dedicated memory available within an FPGA, designed for high-speed data storage and access during processing. This embedded memory plays a vital role in buffering and temporarily holding data for use by logic elements. On most FPGA boards, memory configurations may vary, but BRAM stands out for being directly integrated into the chip. For instance, in Xilinx 7 series devices, each BRAM block typically has a fixed capacity of 36K bits. These blocks are flexible—they can be partitioned into smaller units or combined to form larger memory spaces as needed. BRAM also supports a variety of operating modes and can be configured with additional features, such as error correction capabilities, enhancing reliability in critical applications.

### **Internal clock circuitry**

The internal clock circuitry of an FPGA is designed to manage and distribute timing signals efficiently across the chip. It includes specialized I/O blocks with high-drive clock drivers capable of handling strong clock signals. These drivers receive input from dedicated clock pads and route the signals onto global clock lines, which are engineered to ensure low skew and fast signal propagation throughout the FPGA. This infrastructure supports synchronous design, which is critical in FPGA development, as only these global clock lines can maintain uniform timing and reliable signal alignment across all logic elements.

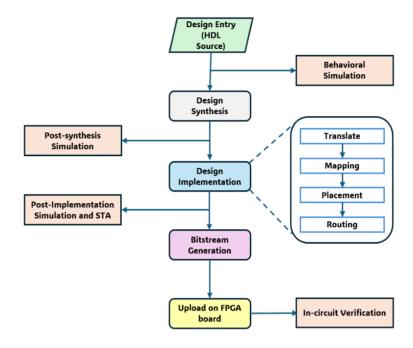

# 2.6 Overview of FPGA Hardware Design Methodology

The standard hardware design flow for FPGA programming is shown in Fig.2.10. FPGAs need a specific hardware design process, in contrast to microcontrollers and microprocessors, which usually rely on software design. Below is a description of the key steps in FPGA programming.

Fig.2.10 General flow of hardware design

The various blocks, which are interconnected above, when operating in synchronization with each other, give us the desired implementation of any logical and arithmetic circuit.

## **Design Entry**

A hardware description language (HDL), a schematic editor, or an editor for finite-state machines (FSMs) can all be used to describe the logic of a design. This procedure entails selecting elements from a library and directly projecting the functionality of the design onto particular computational blocks. HDLs provide a means of defining the design either structurally or behaviorally for intricate designs where managing visual representation becomes challenging. Although Verilog and VHDL are the most popular HDLs, Handel-C, Impulse-C, and System are some C-like substitutes.

#### **Behavioral Simulation**

By contrasting the HDL's output with the behavioral model's, this step is crucial for confirming the HDL's accuracy. Functional testing is made possible by behavioral simulation using Electronic Design Automation (EDA) tools and the RTL (Register Transfer Level) description.

## **Design Synthesis**

This process converts the HDL code into a device netlist, which represents the entire circuit using logical components. During synthesis, the tool verifies code syntax, analyzes the design's architectural hierarchy, and performs compilation along with various optimizations. The generated netlist is typically saved in a .ngc file format.

## **Design Implementation**

The design implementation comprises the following steps

#### 1. Translate

During translation, netlists are combined into a single NGD file, followed by timing and logical design rule checks. Constraints from the user constraint file (UCF) are then integrated into the merged netlist.

### 2. Map

During this stage, the tool applies timing and location constraints and distributes resources to basic logic components. The physical design database and a post-mapping Static Timing Analysis (STA) report detailing block and routing delays are then produced, along with optimization for the target device.

**Place and Route** This phase involves the placement and routing of the design, resulting in the post-place-and-route STA report detailing all nets and delays in the design.

## **Device Programming**

The finalized routed design needs to be translated into a format compatible with the FPGA. To achieve this, the routed .ncd file is input into the BitGen utility, which produces a bitstream file that holds the complete configuration data required to program the FPGA.

## **Timing Analysis**

In this phase, a timing analysis tool verifies that the implemented design satisfies the user-defined timing constraints, such as clock frequency, setup time violations, and hold time violations.

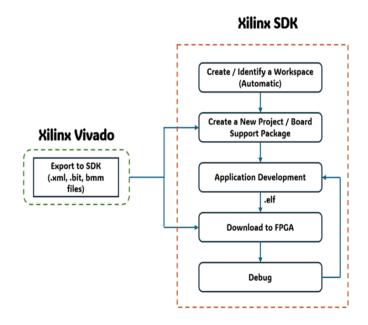

## 2.7 Software Design Flow for FPGA Using Xilinx Tools

Fig.2.11 Block diagram for software design flow of FPGA

The standard workflow for developing a software application for a Vivado®-based embedded system using Xilinx® SDK includes the following steps:

1)Launch Xilinx SDK and choose to either open an existing workspace or create a new one using a hardware platform file generated by the Vivado® IP Integrator.

**2)Start developing the software application**. The SDK offers comprehensive documentation for software libraries and drivers provided within the Board Support Package (BSP).

3)The SDK automatically creates a default linker script for the application. we can modify the memory layout as needed using the linker script generation tools.

**4)To test the application on the hardware target**, set up a run/debug configuration. If required, load the hardware bitstream onto the FPGA device before executing or debugging the application.

## 2.8 Merits and demerits of FPGA

FPGAs offer several benefits. Their ability to be programmed at the logic level allows them to support high-speed and parallel signal processing, which are tasks that are frequently challenging for traditional processors. FPGAs are completely reprogrammable, even remotely, enabling numerous reuses in contrast to ASICs, which are fixed after fabrication. Faster time-to-market is made possible by their broad availability and rapid programming using HDL. Furthermore, FPGA development is less expensive than ASIC development, with no major Non-Recurring Engineering (NRE) costs and lower tool and development costs. Automated tools that manage timing, placement, and routing further streamline the design process by lowering the amount of manual labour and simplifying the design.

There are some restrictions on FPGAs. In contrast to the comparatively simpler C programming used in processor-based systems, programming them necessitates a thorough understanding of digital system design and VHDL or Verilog. In comparison to ASICs, they also typically use more power and provide less optimization flexibility. The initial FPGA selection is a crucial choice because, once chosen, the design is constrained by the resources of the device, which may limit the project's overall size and functionality. In contrast to ASICs, which are more affordable in large quantities, FPGAs are best suited for prototyping and small-scale production, but their cost decreases as production volume rises.

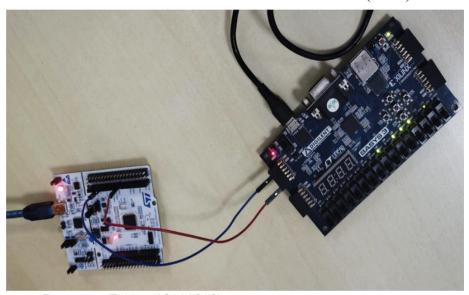

# 2.9 Boards utilized in data transmission and reception

As in the subsequent chapters, the primary focus of the thesis work has been centered around data communication between different peripherals. So, in this regard, different types of boards have been utilized. These are the BASYS 3 Board and the ZYNQ Board.

Fig.2.12 The ZYBO Zynq-7000 development board

A flexible, entry-level development platform for embedded software and digital circuit design is the **ZYBO** (Zynq Board). It offers an integrated solution that combines the flexibility of 7-series FPGA fabric with the power of **a dual-core ARM Cortex-A9 processor**, thanks to its construction around the **Xilinx Zynq-7000 Z-7010 SoC**, the smallest member of the Zynq family. Because of its All Programmable System-on-Chip (AP SoC) architecture, which facilitates smooth hardware/software integration, ZYBO is perfect for low-to-mid volume embedded applications, educational use, and rapid prototyping. A variety of multimedia and connectivity peripherals are included on the board, enabling full system development without the need for extra parts. There is plenty of space for customization and expansion thanks to its six MOD ports.

## **Key Features of the Zynq-7010 AP SoC**

A DDR3 memory controller with eight DMA channels for effective data handling supports the Zynq-7010 AP SoC's potent 650 MHz dual-core ARM Cortex-A9 processor. It provides a wide range of low-bandwidth interfaces like SPI, UART, CAN, and I<sup>2</sup>C for general-purpose communication in addition to high-bandwidth peripherals like Gigabit Ethernet, USB 2.0, and SDIO.

The 4,400 logic slices that make up the integrated programmable logic, which is comparable to an Xilinx Artix-7 FPGA, each have eight flip-flops and four 6-input LUTs. It has two clock management tiles with PLL and MMCM for accurate timing control, 80 DSP slices for sophisticated arithmetic operations, and 240 KB of block RAM. High-performance, mixed-signal processing is also made possible by its on-chip XADC (analog-to-digital converter) and support for internal clock speeds exceeding 450 MHz.

## 2.10 BASYS 3 Board

Fig. 2.13 Digilent Basys 3 Artix-7 FPGA Board

The **Basys 3** board is a fully integrated, user-friendly digital circuit development platform built around the Xilinx Artix-7<sup>TM</sup> FPGA (**part number XC7A35T-1CPG236C**). Designed for both beginners and advanced users, it offers a cost-effective solution for implementing a wide range of digital designs, from simple combinational circuits to more advanced sequential systems like embedded processors and controllers. Featuring built-in USB, VGA, and other I/O ports, along with an ample set of switches, LEDs, and various I/O devices, the board enables users to develop and test numerous projects without needing external hardware. Additionally, the board provides sufficient unallocated FPGA I/O pins for further expansion via Digilent Pmods or custom peripherals, making it a versatile platform for both academic and practical applications.

## **Key Features of the Basys 3 Board**

With more capacity, faster speed, and better resources than previous generations, the Artix-7 FPGA is made for high-performance logic applications. The Artix-7 35T version incorporates roughly 33,280 logic cells arranged in 5,200 slices, each of which has eight flip-flops and four 6-input look-up tables (LUTs). In addition, it has 90 DSP slices for effective

arithmetic operations, 1,800 Kbits of fast block RAM, and internal clock speeds higher than 450 MHz. It has five clock management tiles with phase-locked loops (PLLs) to control timing and synchronization. Furthermore, an on-chip analog-to-digital converter (XADC) is housed in the FPGA, allowing for internal analogue signal monitoring.

## Peripherals available on the Basys 3 Board

The **Basys 3** board also has an enhanced array of ports and peripherals to support a wide range of digital designs. It features 16 user switches, 16 user LEDs, 5 pushbuttons, and a 4-digit 7-segment display for basic input/output operations. For expansion, it includes three Pmod ports and an additional Pmod dedicated to XADC signals. A 12-bit VGA output supports display capabilities, while communication and programming are facilitated through a USB-UART bridge, Serial Flash memory, and a Digilent USB-JTAG port. Moreover, it includes a USB HID host interface, allowing direct connection of mice, keyboards, and memory sticks.

## 2.11 UART as a Communication Protocol

UART is a fundamental communication protocol in various systems, including embedded systems, microcontrollers, and computers, primarily due to its simplicity and efficiency. Unlike other communication protocols, such as SPI or I2C, UART requires only two wires for transmitting and receiving data, making it a preferred choice in many applications. UART operates on asynchronous serial communication at its core, offering configurable speeds to accommodate diverse system requirements. In this asynchronous mode, data transmission occurs without a synchronized clock signal between the transmitting and receiving devices. Instead, UART devices rely on predefined baud rates to ensure proper data transfer.

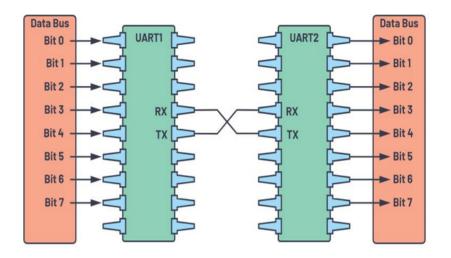

Fig.2.14 UART with Data Bus

Each UART device consists of two fundamental signals: Transmitter (Tx) and Receiver (Rx), which enable the exchange of serial data between devices, ensuring efficient communication. As illustrated in Fig. 2.14, the transmitting UART receives data in parallel format through a control data bus. This data is then converted into serial form and transmitted bit by bit to the receiving UART, where it is describing back into parallel form for use by the receiving device.

Although UART communication is relatively straightforward, proper synchronization is critical for reliable data exchange. Both the transmitting and receiving devices must operate at the same baud rate, allowing for a deviation of up to 10%. Exceeding this tolerance can result in timing mismatches, potentially causing errors in data transmission and reception. Therefore, aligning baud rates accurately is vital for effective UART communication. The typical UART frame structure is depicted in Fig. 2.15.

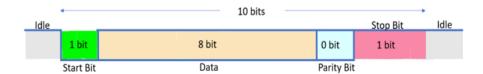

Fig.2.15 UART frame of data transmission and reception

# 2.12 Merits of UART as communication protocol

There are following advantages of using UART as communication protocol for data transmission and reception.

- 1) It operates efficiently by utilizing only two wires, simplifying the hardware setup required for communication between device.

- 2) Unlike synchronous communication protocols, UART does not necessitate a dedicated clocksignal, reducing system complexity.

- 3) The data format which is sent from one device to another device includes a parity bit to check that if any error is present in the data packet.

- 4) UART's flexibility allows the data packet structure to be modified, provided that both the transmitter and receiver are configured to match the changes.

# 2.13 Demerits of UART as communication medium

Despite its various advantages as communication protocal, it has certain limitations too.

- 1)A significant drawback is the limited size of the data frame, which can be a maximum of 10 bits. This constraint can create difficulties when handling larger data sets.

- 2) UART does not support multi-master or multi-slave configurations, which restricts its use in scenarios that require such system architectures.

- 3) Ensuring consistent baud rates across UART devices is essential, as deviations greater than 10% can cause synchronization problems and data

transmission errors, making reliable communication between devices challenging.

## 2.14 Identification of communicated data

In UART communication, data is transmitted by first sending a start bit, represented by a "0." This is followed by the 8-bit data. Once the entire data packet is sent, a stop bit, represented by a "1," is transmitted to indicate the completion of the data transmission process.

Another important point to note is that after the start bit is transmitted, the data packet is sent beginning with the least significant bit (LSB), proceeding sequentially up to the most significant bit (MSB).

For example, suppose if it is required to send the data from FPGA to a PC and if the data is specified as (10101110) then first bit will be start bit that is 0 and after that LSB of the given data like 0 in this case and subsequentially other bits till MSB is reached and after that stop bit 1 as final bit to show the completion of transmission/reception process.

The above text accurately represents the format in which data is transmitted or received by any device.

## Chapter 3

## **System Design and Implementation**

In this module the whole work carried out throughout my project will be discussed in length and breadth. Here all the hardware and software components involved in the realization of my project will also be discussed in vivid details.

As we know, heterogeneous computing plays an important role in the realization of complex systems where there is large-scale involvement of data in executing the assigned task. In view of the above problem statement several tasks have been performed, which eventually led to the development of a prototype system, which, if implemented successfully with some rectification in it, will surely lead to the real implementation of MD simulation using heterogeneous computing.

To realize the final work following steps have been taken and these are as follows:

- 1) To establish communication between PC and an FPGA by sending and receiving the data correctly.

- 2) To store the data in the BRAM of FPGA.

- 3) To check the integrity of sent data by using a DSO.

- 4) To check the integrity of received by using inbuilt led on the BASYS 3 Board.

- 5) Before establishing the interboard communication between two Basys 3 Board the signal strength and its integrity is verified by using STM 32 Microcontroller and DSO.

- 6) Finally, the interboard communication has been implemented and various arithmetic and logical operations were performed on