# A CRITICAL ASSESSMENT OF REALIZING CAPACITORLESS DRAM WITH INNOVATIVE RECONFIGURABLE MOSFETS

#### Ph.D. Thesis

# By **ROHIT KUMAR NIRALA**

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE

**JULY 2025**

# A CRITICAL ASSESSMENT OF REALIZING CAPACITORLESS DRAM WITH INNOVATIVE RECONFIGURABLE MOSFETS

#### **A THESIS**

Submitted in partial fulfillment of the requirements for the award of the degree of

DOCTOR OF PHILOSOPHY

## ROHIT KUMAR NIRALA

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE

**JULY 2025**

#### INDIAN INSTITUTE OF TECHNOLOGY INDORE

I hereby certify that the work which is being presented in the thesis entitled A CRITICAL ASSESSMENT OF REALIZING **CAPACITORLESS DRAM** WITH **INNOVATIVE RECONFIGURABLE MOSFETS** in the partial fulfillment of the requirements for the award of the degree of DOCTOR OF PHILOSOPHY and submitted in the DEPARTMENT OF ELECTRICAL ENGINEERING, INDIAN INSTITUTE OF TECHNOLOGY INDORE, is an authentic record of my own work carried out during the time period from August 2020 to July 2025 under the supervision of Dr. Abhinav Kranti, Professor, Department of Electrical Engineering, Indian Institute of Technology Indore.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other institute.

Rohit Kumar Dirala 21-07-2025

Signature of the student with date

Rohit Kumar Nirala (Roll no. 2001102005)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

Signature of Thesis Supervisor with date

Prof. Abhinav Kranti

Rohit Kumar Nirala has successfully given his Ph.D. Oral Examination held on November 17, 2025.

Signature of Thesis Supervisor with date

#### **ACKNOWLEDGEMENTS**

My profound appreciation goes out to my Ph.D. thesis advisor, Prof. Abhinav Kranti, for giving me the chance to work in his research group at IIT Indore. I am incredibly appreciative of his advice, inspiration, patience, and criticism throughout my doctoral studies. I would like to sincerely thank my PSPC members, Prof. Prabhat Kumar Upadhyay, and Prof. Abhishek Srivastava, for their comments, helpful recommendations, and constructive criticism during the Ph.D. work.

I would like to express my sincere gratitude to the University Grants Commission, Ministry of Education, Government of India, for the award of Junior Research Fellowship (190520491384) for the entire duration of the Ph.D. program. The research infrastructure at the Department of Electrical Engineering, IIT Indore, for the Ph.D. research is gratefully acknowledged. I would also like to acknowledge the use of research infrastructure under the grant CRG/2019/002937, from the Department of Science and Technology, Government of India. The thesis work would not have been possible without the support, help and cooperation of faculty and staff members of IIT Indore.

I am deeply grateful to my present and former colleagues Nivedita, Bhuvaneshwari, Sandeep, Arghya, Keerthi, Aakash, Abu, Aman, and Devesh for their kind support during my research work. Furthermore, I extend my heartfelt gratitude to Dr. Manish Gupta, BITS Pilani, K K Birla Goa Campus, Goa, for discussions and support on the research work and simulation tool.

I dedicate this work to the loving memory of my parents, Late Mr. Satyendra Narayan Singh and Late Mrs. Mina Singh, whose values and blessings continue to guide and inspire me every day. My deepest gratitude to my elder brother, Mr. Rahul Kumar Nirala, and my sister-in-law, Mrs. Laxmi Singh, for their care, and encouragement, and to my wife, Mrs. Manisha Singh, for her unwavering support. The smiles of my nieces, Aishani and Avani, and my nephew, Ayansh have been a constant source of motivation and joy throughout this journey.

Lastly, I wish to express my profound gratitude to the Almighty, who has bestowed upon me life, faith, and the ability to navigate through this crucial phase of my journey.

Rohit Kumar Nirala

# In the Loving Memory of My Parents

#### **ABSTRACT**

## A CRITICAL ASSESSMENT OF REALIZING CAPACITORLESS DRAM WITH INNOVATIVE RECONFIGURABLE MOSFETS

The evolution of transistor architecture from conventional planar to three-dimensional vertical nanosheet or nanowire coupled with innovation through low power Silicon-on-Insulator (SOI) technology has largely contributed to enhancing transistor density in modern chips. Despite critical innovations in transistor architecture and reduction of parasitic components, a fundamental limitation of Complementary Metal Oxide Semiconductor (CMOS) technology is the requirement of separate n-type and p-type transistors to implement logic circuits. If the polarity (type of transistor) could be obtained through bias in the same structure (device) then separate transistors would not be needed for implementing logic circuits. A three gated (3-gated) reconfigurable MOSFET, also known as reconfigurable field effect transistor (RFET), permits selective carrier injection through modulation of metal-semiconductor (M-S) Schottky contact with an additional gate for channel control.

The possibility of showcasing single transistor (1T) capacitorless (0C) dynamic random access memory (DRAM) through RFET adds to the multifunctional capability of the architecture. The 3-gated RFET is ideal for 1T-DRAM as it facilitates the storage of generated holes in the semiconductor film underneath the control gate (CG). A higher positive (negative) voltage at the polarity gate (PG) causes band bending, and subsequent tunneling of electrons (holes) to the semiconductor which transforms the region underneath PG to function as pseudo source/drain. The location of pseudo source/drain regions away from the semiconductor region underneath the CG due to the presence of underlap/ungated region allows the storage of holes at appropriate biases. The feasibility assessment of implementing 1T-DRAM with RFET has been carried out through well calibrated simulations with appropriate models for capturing inherent physical phenomenon in the device.

The degradation of retention time (RT) with a change in bias is a serious concern in 1T-DRAM. This degradation is critical for 1T-DRAM with RFET due to a greater (three) number of gates. While front and back PGs can be electrically connected, the independent front and back CG

operation is required to implement 1T-DRAM through planar RFET. Therefore, the bias range able to sustain a degradation of 50% of maximum retention time ( $RT_{max}$ ) in RFET based 1T-DRAM has been investigated to estimate the bias tolerance of retention time. In addition, the sensitivity of key performance metrics of 1T-DRAM on device parameters has also been evaluated.

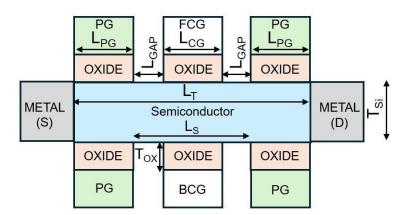

RFET can be designed with different combinations of lengths of CG ( $L_{CG}$ ) and PG ( $L_{PG}$ ) and ungated region ( $L_{GAP}$ ) for a fixed total length ( $L_{T} = 2(L_{PG} + L_{GAP}) + L_{CG}$ )). The storage length ( $L_{S} = L_{CG} + 2L_{GAP}$ ) depends on CG and separation between PG and CG. This essentially implies that RFET could be designed with various values of  $L_{S}/L_{T}$  (with typical range of 0.4 to 0.8) for a given  $L_{T}$  (100 nm). Hence, the choice of optimal biases for RFET based 1T-DRAM have been ascertained as a function of  $L_{S}/L_{T}$ . In addition, the requirements of 1T-DRAM to function as on-chip (embedded) memory is different from that for standalone applications due to the requirement of fast write/read operations. An in-depth analysis in terms of write and read access times has been carried out to ascertain the feasibility of RFET for implementation as embedded 1T-DRAM.

The use of nanowire (NW) transistor architecture has been largely dictated by the progress in logic technology. Investigating the possible realization of 1T-DRAM with NW transistor architecture is crucial for using same type of transistors for logic and memory blocks. Since independent back gate operation is not possible in NW transistor, RFET serves as an ideal topology to realize 1T-DRAM. In addition to exploring 1T-DRAM functionality, the impact of word line (WL) and bit line (BL) disturbance in an array for various operations (write 1, write 0, and read) has been examined for pragmatic memory realization. The biases for 1T-DRAM are usually selected to ensure proper operations – write 1 (program), write 0 (erase), hold, and read. In an array realization, an important parameter for bias selection is array disturbance apart from feasibility of individual memory operations. Hence, bias optimization (for each operation) based on enhancing the duration of disturbance tolerance has been carried out in RFET based 1T-DRAM array.

Overall, this thesis presents a critical assessment of implementing 1T-DRAM through planar and nanowire topologies of RFET. Besides highlighting the working mechanism and device physics for implementing 1T-DRAM, the thesis has introduced fresh perspectives to enhance array retention while focusing on bias selection based on the duration of disturbance tolerance.

#### LIST OF PUBLICATIONS

#### A1. In refereed Journals:

- R.K. Nirala, S. Semwal, Y.V. Bhuvaneshwari, N. Rai and A. Kranti, "Sensitivity implications for programmable transistor based 1T-DRAM", Solid-State Electronics, vol. 194, 108353, 2022. DOI: 10.1016/j.sse.2022.108353 (Journal Impact factor: 1.4).

- 2. R.K. Nirala, S. Semwal, and A. Kranti, "A critique of length and bias dependent constraints for 1T-DRAM operation through RFET", Semiconductor Science and Technology, vol. 37, 105013, 2022. DOI: 10.1088/1361-6641/ac8c67 (Journal Impact factor: 1.9).

- **3.** R.K. Nirala, S. Semwal, M. Gupta, and A. Kranti, "Energy and disturbance analysis of 1T-DRAM with nanowire gate-all-around RFET", **IEEE Trans. Electron Devices**, vol. 71, pp. 2950-2956, 2024. DOI: 10.1109/TED.2024.3371950 (Journal Impact factor: 2.9).

#### **A2.** In refereed Conferences:

- R.K. Nirala, S. Semwal, Y.V. Bhuvaneshwari, N. Rai, and A. Kranti, "Scalability and sensitivity assessment of programmable transistor based 1T-DRAM", 8<sup>th</sup> Joint International EuroSOI Workshop and International Conference on Ultimate Integration on Silicon (EuroSOI-ULIS), May 18-20, 2022, Accepted (Online presentation).

- 2. R.K. Nirala, S. Semwal, N. Rai, and A. Kranti, "What are the constraints for 1T-DRAM operation via reconfigurable transistor?", Extended Abstracts of the 2022 International Conference on Solid State Devices and Materials (SSDM), Chiba, Japan, September 26-29, 2022, pp. 621-622, 2022. DOI: 10.7567/SSDM.2022.J-10-02.

- 3. A. Kranti, R.K. Nirala, and S. Semwal, "Dual word line enabled energy-efficient high-speed RFET based 1T-eDRAM", Extended Abstracts of the 2023 International Conference on Solid State Devices and Materials (SSDM), Nagoya, Japan, September 5-8, 2023, pp. 685-686, 2023. DOI: 10.7567/SSDM.2023.PS-2-17.

- 4. R.K. Nirala, M. Gupta, and A. Kranti, "Disturbance induced refresh time lowering in nanowire RFET 1T-DRAM array", Extended Abstracts of the 2024 International Conference on Solid State Devices and Materials (SSDM), Himeji, Japan, September 1-4, 2024, pp. 629-630, 2024. DOI: 10.7567/SSDM.2024.PS-02-08.

**5.** A. Kranti, R.K. Nirala, and M. Gupta, "Duration of disturbance tolerance governed bias selection in 1T-DRAM array", Extended Abstracts of the **2025 International Conference on Solid State Devices and Materials (SSDM)**, Yokohama, Japan, September 15-18, 2025, pp. 717-718, 2025. DOI: 10.7567/SSDM.2025.PS-02-10.

## TABLE OF CONTENTS

| TITLE PAGE           | Ι     |

|----------------------|-------|

| DECLARATION PAGE     | II    |

| ACKNOWLEDGEMENT      | III   |

| DEDICATION PAGE      | IV    |

| ABSTRACT             | V     |

| LIST OF PUBLICATIONS | VII   |

| TABLE OF CONTENTS    | IX    |

| LIST OF FIGURES      | XIII  |

| LIST OF TABLES       | XXII  |

| NOMENCLATURE         | XXIV  |

| ACRONYMS             | XXVII |

#### **Chapter 1: Introduction**

| 1.1 Downscaling Bulk Metal-Oxide-Semiconductor Transistor                | 3  |

|--------------------------------------------------------------------------|----|

| 1.2 Silicon-on-Insulator MOSFET                                          | 5  |

| 1.3 Schottky Barrier MOSFET                                              | 9  |

| 1.4 Reconfigurable Transistors                                           | 11 |

| 1.5 Comparison with Conventional MOSFETs                                 | 14 |

| 1.6 Memory Architecture                                                  | 16 |

| 1.7 Potential of RFET for Capacitorless Dynamic                          | 17 |

| Random Access Memory (1T-DRAM)                                           |    |

| 1.8 Hole Generation Mechanism in 1T-DRAM                                 | 18 |

| 1.9 Problem Formulation and Thesis Objectives                            | 19 |

| 1.10 Thesis Outline                                                      | 20 |

| Chapter 2: Working Mechanism of RFET and Implementing                    |    |

| Capacitorless DRAM                                                       |    |

| 2.1 Introduction                                                         | 23 |

| 2.2 Simulation and Device Description                                    | 26 |

| 2.3 Working Mechanism of RFET                                            | 26 |

| 2.3.1 Impact of Positive V <sub>PG</sub> on SB                           | 27 |

| 2.3.2 N-Type Pseudo Source/Drain Region                                  | 27 |

| 2.3.3 Impact of Positive V <sub>CG</sub> on Energy Barrier Underneath CG | 29 |

| 2.3.4 N-Type Conduction in RFET                                          | 30 |

| 2.3.5 Impact of Negative V <sub>PG</sub> on SB                           | 30 |

| 2.3.6 P-Type Pseudo Source/Drain Regions                                 | 32 |

| 2.3.7 Impact of Negative V <sub>CG</sub> on Energy Barrier Underneath CG | 32 |

| 2.3.8 P-Type Conduction in RFET                                          | 32 |

| 2.4 Working Mechanism of RFET based 1T-DRAM                              | 34 |

| 2.4.1 Write 1 and Write 0 Operations                                     | 35 |

| 2.4.2 Hold Operation                                                     | 36 |

| 2.4.3 Read Operation                                                     | 39 |

| 2.4.4 Retention Time Estimation                                          | 39 |

| 2.4.5 Performance at High Temperature (125 °C)                           | 40 |

| 2.5 Sensitivity Analysis                                            | 41 |

|---------------------------------------------------------------------|----|

| 2.5.1 Analysis of Voltage Sensitivity During Hold Operation         | 42 |

| 2.5.2 Analysis of Voltage Sensitivity During Read Operation         | 44 |

| 2.5.3 Process Sensitivity                                           | 45 |

| 2.6 Conclusion                                                      | 46 |

| Chapter 3: Length Dependent Constraints in RFET 1T-DRAM             |    |

| 3.1 Introduction                                                    | 47 |

| 3.2 Impact of Storage Length on 1T-DRAM Performance                 | 51 |

| 3.2.1 1T-DRAM Operation with Different Storage Lengths              | 51 |

| 3.2.2 Trade-offs Associated with Storage Length and Retention Time  | 53 |

| 3.3 Storage Length Dependent Bias Optimization                      | 55 |

| 3.3.1 Bias Optimization for Write 1 Operation                       | 55 |

| 3.3.2 Bias Optimization for Hold Operation                          | 56 |

| 3.3.3 Bias Optimization for Read Operation                          | 58 |

| 3.4 Impact of Non-Optimal Bias on Retention Time                    | 60 |

| 3.4.1 Variation in Retention Time with Non-Optimal Hold Bias        | 60 |

| 3.4.2 Variation in Retention Time with Non-Optimal Read Bias        | 61 |

| 3.5 Control Gate Length Dependent Bias Optimization                 | 62 |

| 3.6 Feasibility of RFET for On-Chip 1T-DRAM                         | 66 |

| 3.6.1 Impact of Write Time Reduction on Hole Concentration          | 67 |

| 3.6.2 Impact of Read Time Reduction on Retention Time               | 68 |

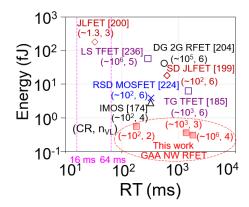

| 3.6.3 Benchmarking                                                  | 69 |

| 3.7 Fabrication Flow of RFET                                        | 70 |

| 3.8 Impact of Traps on SM and RT                                    | 71 |

| 3.9 Conclusion                                                      | 73 |

| Chapter 4: Word Line and Bit Line Disturbance in Nanowire Gate-All- |    |

| Around RFET                                                         |    |

| 4.1 Introduction                                                    | 75 |

| 4.2 1T-DRAM Operation in NW GAA RFET                                | 78 |

| 4.2.1 Write 1 and Write 0 Operations                                | 78 |

| 4.2.2 Hold Operation                                                   | 79  |

|------------------------------------------------------------------------|-----|

| 4.2.3 Read Operation                                                   | 80  |

| 4.2.4 1T-DRAM Operation with Four Voltage Levels                       | 82  |

| 4.3 Disturbance Analysis in RFET based 1T-DRAM Array                   | 83  |

| 4.3.1 Disturbance Analysis with Three Voltage Levels                   | 84  |

| 4.3.1.1 WL/BL Disturbance due to Write 1 Operation                     | 86  |

| 4.3.1.2 WL/BL Disturbance due to Write 0 Operation                     | 87  |

| 4.3.1.3 WL/BL Disturbance due to Read Operation                        | 89  |

| 4.3.2 Disturbance Analysis with Four Voltage Levels                    | 91  |

| 4.4 Duration of Disturbance Tolerance in RFET based 1T-DRAM            | 94  |

| 4.4.1 Optimizing Write 1 to Maximize Duration of Disturbance Tolerance | 95  |

| 4.4.2 Optimizing Write 0 to Maximize Duration of Disturbance Tolerance | 96  |

| 4.4.3 Optimizing Read to Maximize Duration of Disturbance Tolerance    | 97  |

| 4.4.4 Disturbance through Hole Concentration Contours                  | 101 |

| 4.4.5 Optimized Biases and Corresponding Current Transient             | 101 |

| 4.5 Benchmarking                                                       | 102 |

| 4.6 Conclusion                                                         | 105 |

| Chapter 5: Conclusion and Scope for Future Work                        |     |

| 5.1 Conclusion                                                         | 107 |

| 5.2 Implementing 1T-DRAM with RFET                                     | 108 |

| 5.3 RFET Length Dependent Bias Optimization                            | 109 |

| 5.4 1T-DRAM with Nanowire RFET and Array Disturbance                   | 110 |

| 5.5 Scope for Future Work                                              | 112 |

| References                                                             | 113 |

## LIST OF FIGURES

| Figure<br>No.   | Figure Title                                                      | Page<br>No. |

|-----------------|-------------------------------------------------------------------|-------------|

| Fig. 1.1        | Growth in processor clock frequency from 1978 to 2017 (39         | 1           |

|                 | years) [5].                                                       |             |

| Fig. 1.2        | Growth in processor performance from 1978 to 2018 (40             | 2           |

|                 | years) [5].                                                       |             |

| <b>Fig. 1.3</b> | Schematic representation of SOI MOSFET with relatively (a)        | 6           |

|                 | thick semiconductor layer, (b) thin semiconductor layer, (c)      |             |

|                 | thin buried oxide layer, and (d) double gate architecture. The    |             |

|                 | substrate region (below the buried oxide) is not shown as the     |             |

|                 | focus is on the active semiconductor layer [7].                   |             |

| Fig. 1.4        | Schematic representation of multi-gate MOSFET cross-              | 7           |

|                 | section (perpendicular to current flow) for (a) vertical dual     |             |

|                 | gate, (b) triple gate, (c) pi gate, (d) omega gate, (e) quadruple |             |

|                 | gate, and (f) cylindrical nanowire architecture [1].              |             |

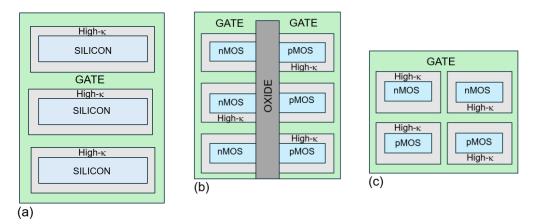

| Fig. 1.5        | Schematic representation of cross-section (perpendicular to       | 9           |

|                 | current flow) of (a) multi-bridge-channel MOSFET [55-56],         |             |

|                 | (b) forksheet MOSFET [57-59], and (c) complementary               |             |

|                 | MOSFET [60-61].                                                   |             |

| <b>Fig. 1.6</b> | Schematic representation of Schottky barrier (SB) MOSFET          | 10          |

|                 | [67].                                                             |             |

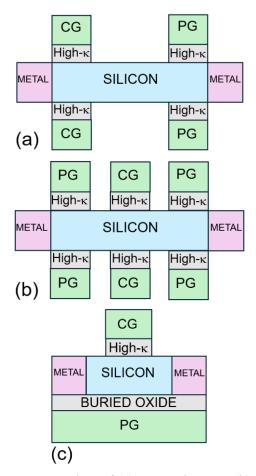

| <b>Fig. 1.7</b> | Schematic representation of (a) 2-gated RFET (b) 3-gated          | 13          |

|                 | RFET, and (c) 2-gated (front and back) RFET architecture          |             |

|                 | [74]. Notations: PG and CG represent program gate and             |             |

|                 | control gate, respectively.                                       |             |

| <b>Fig. 1.8</b> | Schematic representation of 3-gated RFET utilized for             | 15          |

|                 | implementing capacitorless 1T-DRAM. Notations: PG and CG          |             |

|                 | represent program gate and control gate, respectively.            |             |

| Fig. 1.9        | Memory hierarchy based on latency and capacity [149].             | 17          |

|                 |                                                                   |             |

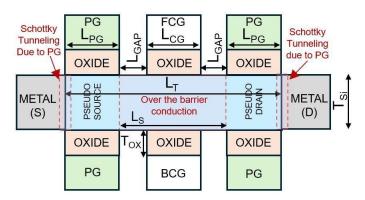

- Fig. 2.1 Schematic diagram of a dual (front (F) and back (B)) gate 24 architecture of reconfigurable field effect transistor (RFET) with two polarity gates (PG) and one control gate (CG). The L<sub>PG</sub>, L<sub>GAP</sub>, L<sub>CG</sub>, L<sub>S</sub>, L<sub>T</sub>, T<sub>OX</sub>, and T<sub>Si</sub> are program gate length, ungated region length, control gate length, storage region length, total length, oxide thickness, and Silicon film thickness, respectively.

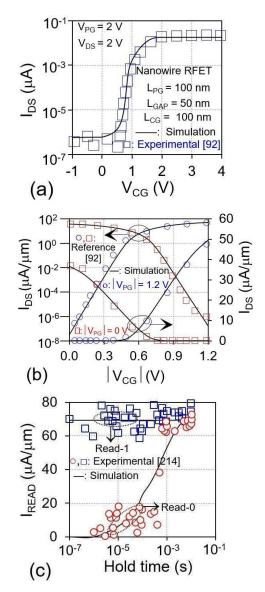

- Fig. 2.2 Comparison of simulated with (a) experimental transfer 25 characteristics ( $I_{DS}$  versus  $V_{CG}$ ) of RFET [92], (b) simulated transfer characteristics for both nMOS and pMOS, (c) experimental read current transient as a function of hold (H) time in MOSFET based 1T-DRAM [214].

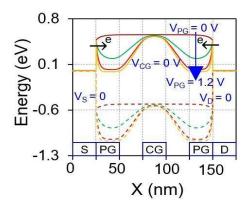

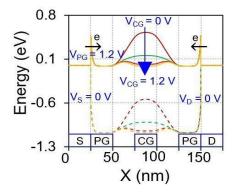

- Fig. 2.3 Impact of positive  $V_{PG}$  on Schottky barrier (SB) at  $V_{CG} = V_S = 27$   $V_D = 0$  V. The curve is extracted at the surface of the RFET channel.

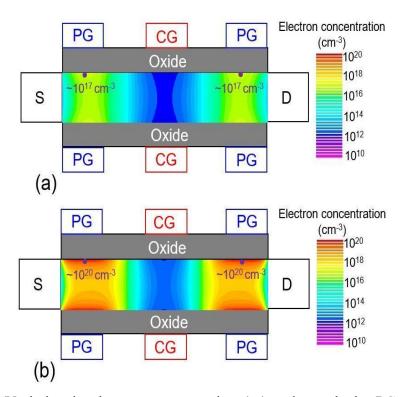

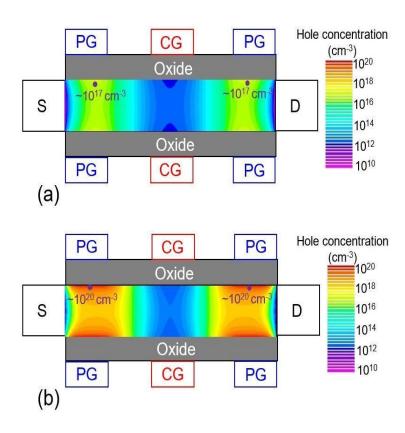

- Fig. 2.4 Variation in electron concentration (n<sub>e</sub>) underneath the PG 28 after the application of (a)  $V_{PG} = 0.4 \text{ V}$ , (b)  $V_{PG} = 1.2 \text{ V}$  at  $V_{CG} = V_S = V_D = 0 \text{ V}$ . A filled circle denotes the point where the electron concentration (n<sub>e</sub>) is mentioned in the contour.

- Fig. 2.5 Impact of positive  $V_{CG}$  on energy barrier underneath the CG at  $V_{PG} = 1.2 \text{ V}, V_S = V_D = 0 \text{ V}$ . The curve is extracted at the surface of the RFET channel.

- Fig. 2.6 Variation in electron concentration ( $n_e$ ) underneath the CG 29 after the application of (a)  $V_{CG} = 0.4 \text{ V}$ , (b)  $V_{CG} = 1.2 \text{ V}$  at  $V_{PG}$  = 1.2 V,  $V_S = V_D = 0 \text{ V}$ . (c) Transfer characteristics of RFET ( $I_{DS}$  versus  $V_{CG}$ ) showing nMOS behavior at different  $V_{DS}$ , i.e., 50 mV and 1 V. A filled circle denotes the point where the electron concentration ( $n_e$ ) is mentioned in the contour.

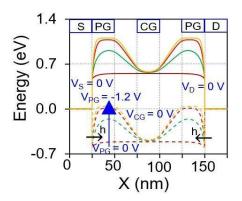

- Fig. 2.7 Impact of negative  $V_{PG}$  on Schottky barrier (SB) at  $V_{CG} = V_S$  31 =  $V_D = 0$  V. The curve is extracted at the surface of the RFET channel.

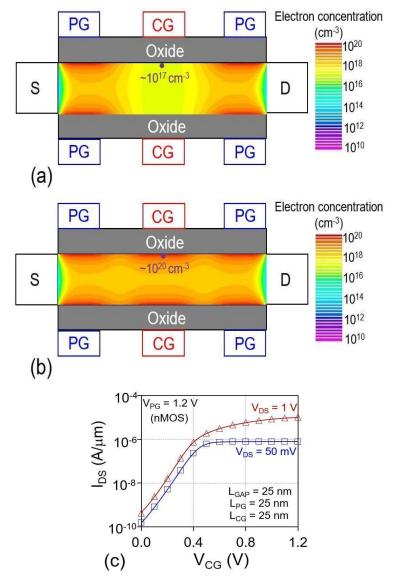

- Fig. 2.8 Variation in hole concentration  $(n_h)$  underneath the PG after the application of (a)  $V_{PG} = -0.4 \text{ V}$ , (b)  $V_{PG} = -1.2 \text{ V}$  at  $V_{CG} = V_S = V_D = 0 \text{ V}$ . Filled circle denotes the point corresponding to that the hole concentration  $(n_h)$  has been mentioned in the contour.

- Fig. 2.9 Impact of negative  $V_{CG}$  on energy barrier underneath the CG 33 at  $V_{PG}$  = -1.2 V,  $V_S$  =  $V_D$  = 0 V. The curve is extracted at the surface of the RFET channel.

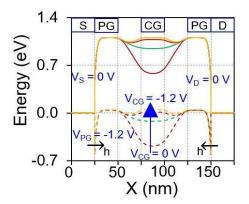

- Fig. 2.10 Variation in hole concentration  $(n_h)$  underneath the CG after the application of (a)  $V_{CG} = -0.4 \text{ V}$ , (b)  $V_{CG} = -1.2 \text{ V}$  at  $V_{PG} = -1.2 \text{ V}$ ,  $V_S = V_D = 0 \text{ V}$ . (c) Transfer characteristics of RFET (I<sub>DS</sub> versus  $V_{CG}$ ) showing pMOS behavior at different  $V_{DS}$ , i.e., -50 mV and -1 V. The filled circle denotes the point where the hole concentration  $(n_h)$  is mentioned in the contour.

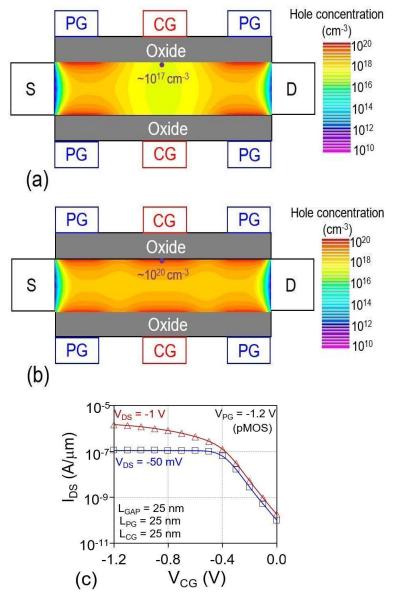

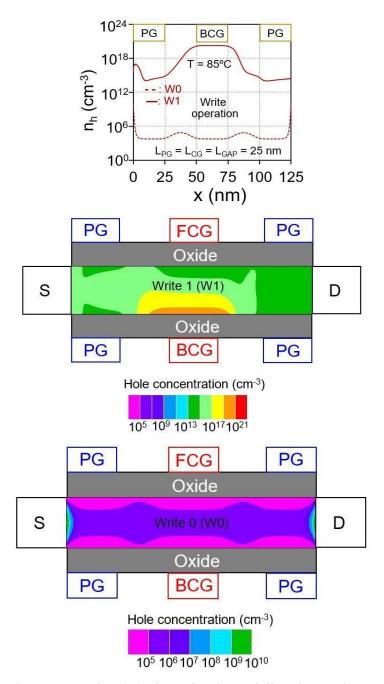

- Fig. 2.11 Hole concentration (n<sub>h</sub>) along the channel direction underneath the back control gate (BCG) for write 1 (W1) and write 0 (W0) operation at Temperature (T) = 85 °C, along with the contour plots of write 1 (W1) and write 0 (W0). The curve is extracted at the bottom surface of the RFET channel.

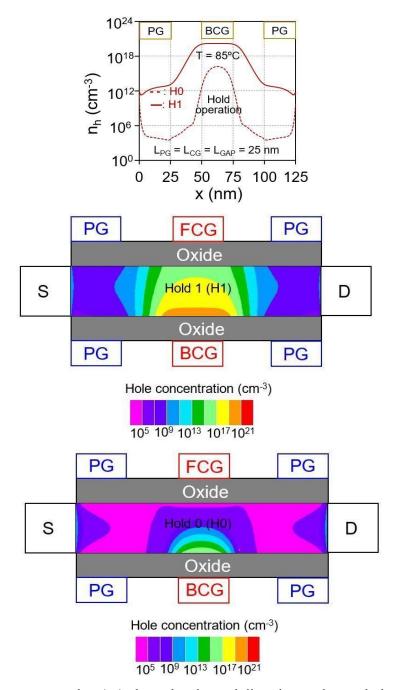

- Fig. 2.12 Hole concentration (n<sub>h</sub>) along the channel direction underneath the back control gate (BCG) for hold 1 (H1) and hold 0 (H0) operation at Temperature (T) = 85 °C, along with the contour plots of hold 1 (H1) and hold 0 (W0). The curve is extracted at the bottom surface of the RFET channel.

- Fig. 2.13

(a) Potential along the channel direction underneath the front control gate (FCG) for read 1 (R1) and read 0 (R0) operation at Temperature (T) = 85 °C (curve is extracted at the front surface of the RFET channel). (b) Drain current transient for the sequence of 1T-DRAM operation with RFET at temperature (T) = 85 °C.

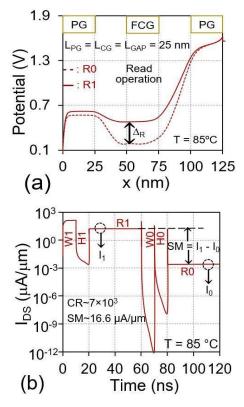

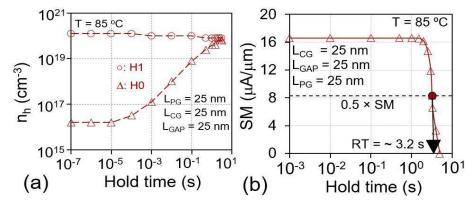

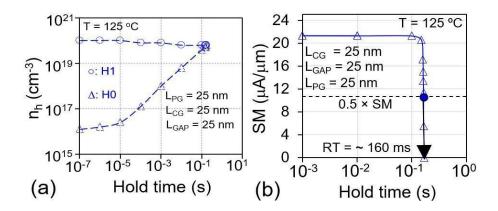

- Fig. 2.14 (a) Variation in hole concentration ( $n_h$ ) with hold time ( $t_{HOLD}$ ) 41 for H1 and H0 states. (b) Variation in sense margin (SM) with hold time ( $t_{HOLD}$ ) at temperature (T) = 85 °C.

- Fig. 2.15 (a) Variation in hole concentration ( $n_h$ ) with hold time ( $t_{HOLD}$ ) 42 for H1 and H0 states. (b) Variation in sense margin (SM) with hold time ( $t_{HOLD}$ ) at temperature (T) = 125 °C.

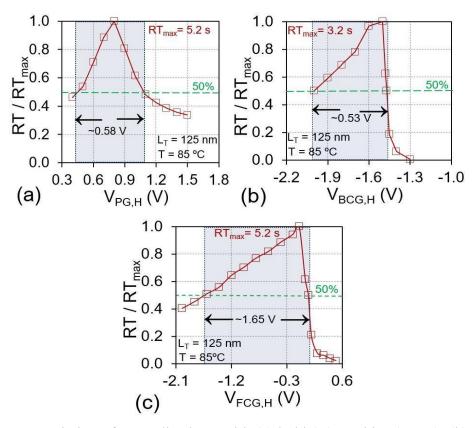

- Fig. 2.16 Variation of normalized RT with (a) hold (H) PG bias ( $V_{PG,H}$ ), 43 (b) hold (H) BCG bias ( $V_{BCG,H}$ ), (c) hold (H) FCG bias ( $V_{FCG,H}$ ), at temperature (T) = 85 °C.

- Fig. 2.17 Variation of normalized RT with (a) read (R) PG bias  $(V_{PG,R})$ , 44 (b) read (R) BCG bias  $(V_{BCG,R})$ , (c) read (R) FCG bias  $(V_{FCG,R})$ , at temperature (T) = 85 °C.

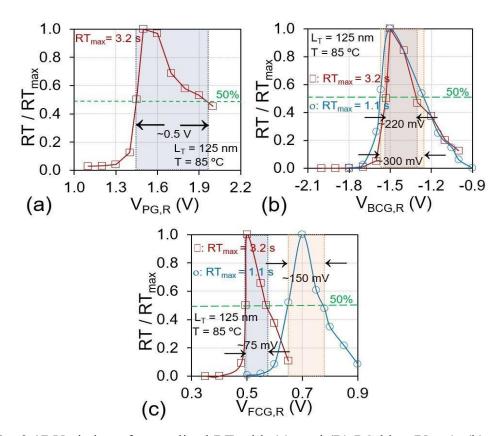

- Fig. 2.18 Sensitivity of RT, SM, and CR on RFET parameters ( $T_{Si}$ ,  $T_{OX}$ , 46  $L_{CG}$ ,  $L_{PG}$ , and  $L_{GAP}$ ), at temperature (T) = 85 °C. The highlighted region shows medium and low sensitivity.

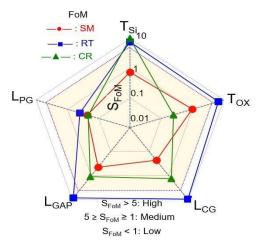

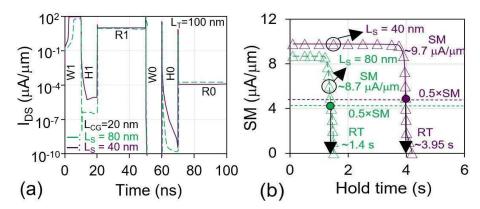

- Fig. 3.1 Variation of hole concentration (n<sub>h</sub>) at the back surface of RFET along the channel direction (x-direction) during (a) write 1 (W1) and write 0 (W0), (b) hold 1 (H1) and hold 0 (H0) operation. (c) Variation of potential at front surface during read 1 (R1) and read 0 (R0) operation. (d) Current transient of RFET based 1T-DRAM for various operations. Variation of (e) hole concentration (n<sub>h</sub>) and (f) read current for R1 and R0 with hold time (t<sub>HOLD</sub>). Biases are mentioned in Table 3.2.

- Fig. 3.2 Comparison of (a) Drain current transient and (b) Variation in SM with hold time ( $t_{HOLD}$ ) of  $L_S=40$  nm and 80 nm for fixed  $L_{CG}=20$  nm with optimal bias. For  $L_S=40$  nm, all biases are the same as shown in Table 3.2, while for  $L_S=80$  nm, biases are the same as shown in Table 3.3.

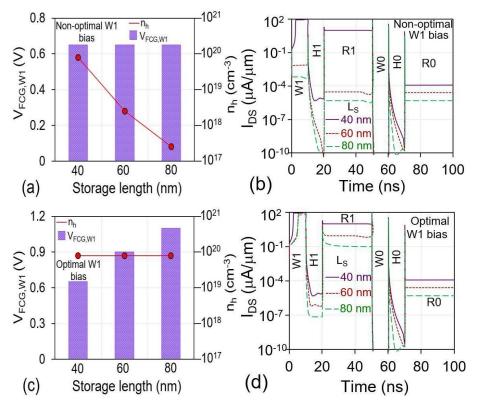

- Fig. 3.3 (a) Excess hole concentration (nh) generated for different L<sub>S</sub> 57 values (40 nm, 60 nm, and 80 nm) at V<sub>FCG,W1</sub> = 0.65 V. (b) Current transient for various L<sub>S</sub> values for the same biases (non-optimal for L<sub>S</sub> = 60 nm and 80 nm) shown in Table 3.2.

(c) Comparison of optimal front CG W1 bias (V<sub>FCG,W1</sub>) for different L<sub>S</sub>. (d) Comparison of the current transient for various L<sub>S</sub> with optimized V<sub>FCG,W1</sub>. L<sub>CG</sub> is 20 nm for L<sub>T</sub> of 100 nm in each L<sub>S</sub>, i.e., 40 nm, 60 nm, and 80 nm.

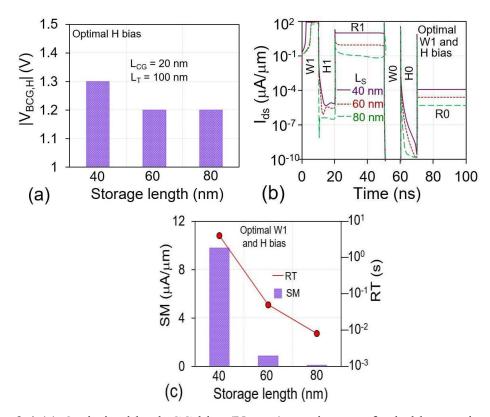

- Fig. 3.4 (a) Optimized back CG bias ( $V_{BCG,H}$ ) requirement for hold operation for different  $L_S$  values. (b) Comparison of current transient for various  $L_S$  values with optimized  $V_{FCG,W1}$  and  $V_{BCG,H}$ . (c) Variation of RT and SM for different  $L_S$  values with optimized  $V_{FCG,W1}$ , and  $V_{BCG,H}$  but at a non-optimal  $V_{FCG,R}$ .  $L_{CG}$  is 20 nm for  $L_T$  of 100 nm in each  $L_S$ , i.e., 40 nm, 60 nm, and 80 nm.

- Fig. 3.5

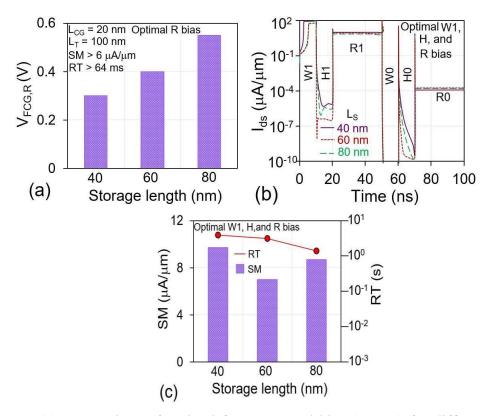

(a) Comparison of optimal front CG read bias (V<sub>FCG,R</sub>) for 59 different L<sub>S</sub> values. (b) Comparison of current transients for various L<sub>S</sub> with optimized V<sub>FCG,W1</sub>, V<sub>BCG,H</sub>, and V<sub>FCG,R</sub>. (c) Variation of RT and SM for different L<sub>S</sub> with optimized V<sub>FCG,W1</sub>, V<sub>BCG,H</sub>, and V<sub>FCG,R</sub>. L<sub>CG</sub> is 20 nm for L<sub>T</sub> of 100 nm in each L<sub>S</sub>, i.e., 40 nm, 60 nm, and 80 nm.

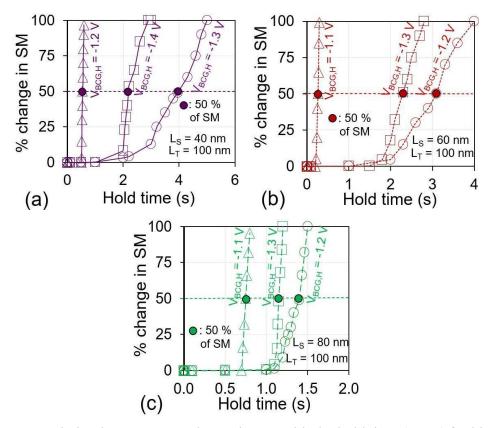

- Fig 3.6 Variation in percentage change in SM with the hold time 60  $(t_{HOLD})$  for biases above and below the optimized  $V_{BCG,H}$  for (a)  $L_S = 40$  nm, (b)  $L_S = 60$  nm, and (c)  $L_S = 80$  nm.

- Fig. 3.7 Variation in SM with the hold time ( $t_{HOLD}$ ) for biases above 62 and below the optimized  $V_{FCG,R}$  for (a)  $L_S = 40$  nm, (b)  $L_S = 60$  nm, and (c)  $L_S = 80$  nm.

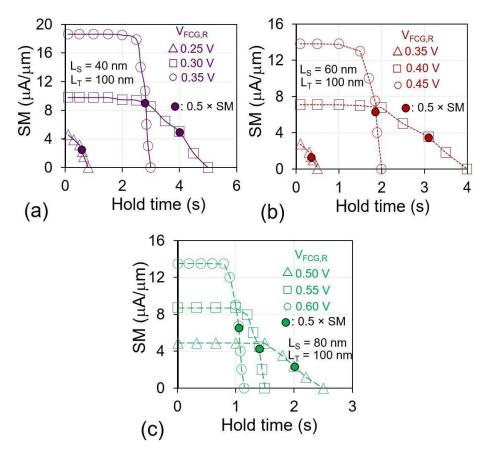

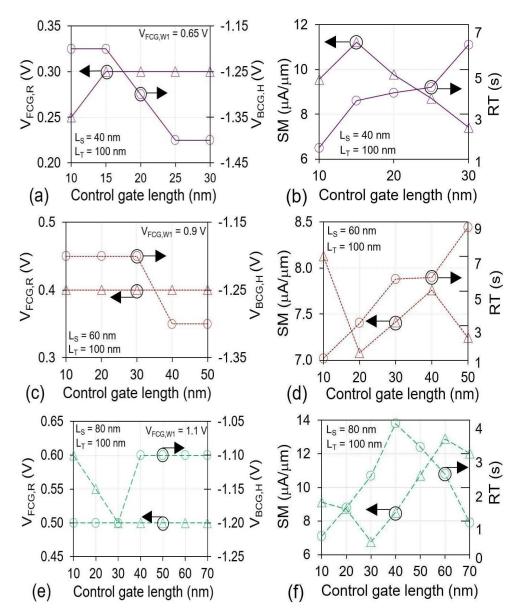

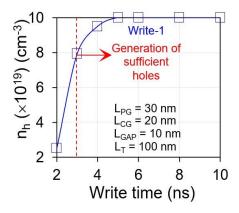

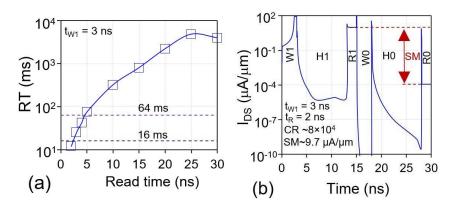

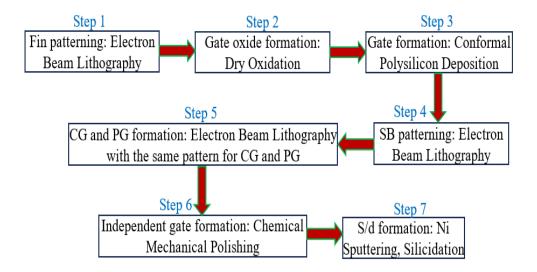

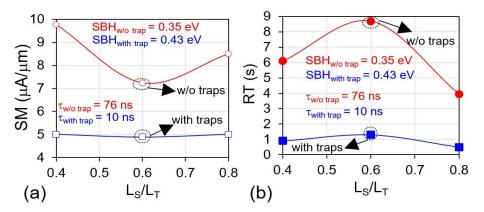

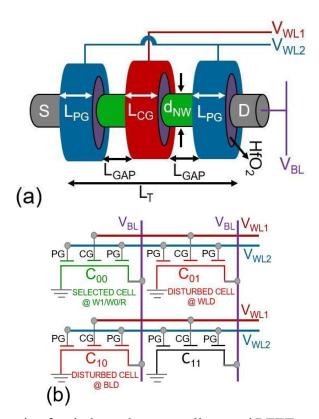

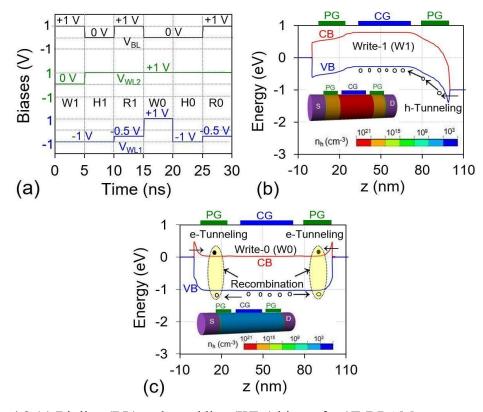

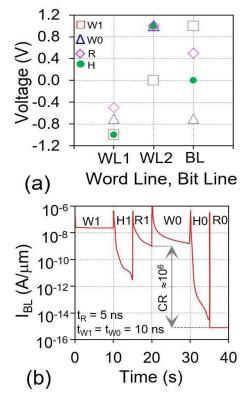

Fig. 3.8 (a) Variation of optimal back CG hold bias (V<sub>BCG,H</sub>) and front 64 CG read bias (V<sub>FCG,R</sub>) with control gate length (L<sub>CG</sub>) and corresponding (b) SM and RT for  $L_{CG}$  in  $L_{S} = 40$  nm. (c) Variation of optimal back CG hold bias (V<sub>BCG,H</sub>) and front CG read bias (V<sub>FCG,R</sub>) with control gate length (L<sub>CG</sub>) and corresponding (d) SM and RT for  $L_{CG}$  in  $L_{S} = 60$  nm. (e) Variation of optimal back CG hold bias (V<sub>BCG,H</sub>) and front CG read bias (V<sub>FCG,R</sub>) with control gate length (L<sub>CG</sub>) and corresponding (f) SM and RT for  $L_{CG}$  in  $L_{S} = 80$  nm. Fig. 3.9 Variation of hole concentration (nh) at back surface of RFET 66 during write 1 (W1) for various values of write time ( $t_{W1} = 2$ ns to 10 ns). All biases are mentioned in Table 3.2. (a) Variation of RT with read time ( $t_R = 2$  ns to 30 ns) for a Fig. 3.10 67 fixed  $t_{W1}$  of 3 ns. (b) Current transient for a minimum  $t_{W1}$  (3 ns) and  $t_R$  (2 ns). Parameters:  $L_{PG} = 30$  nm,  $L_{CG} = 20$  nm,  $L_{GAP}$ = 10 nm and  $L_T$  = 100 nm. All biases are mentioned in Table 3.2. Fig. 3.11 Possible fabrication flow for RFET structure through well-71 known fabrication steps used in [225], [227]. Fig. 3.12 Impact of traps on (a) sense margin (SM) and (b) retention time 73 (RT) of RFET based 1T-DRAM. Fig. 4.1 (a) Schematic of an independent gate-all-around RFET used 76 for 1T-DRAM operation. The notation for WL or BL bias is V with the subscript denoting WLs (WL1 and WL2) or BL. V<sub>WL1</sub> and V<sub>WL2</sub> are connected to CG and PG, respectively, whereas  $V_{BL}$  is connected to the D. (b) A 2 × 2 array consists of NW GAA RFET in each cell, i.e., cell 00, cell 01, cell 10, and cell 11. Each cell in the array consists of two WLs and one BL. Fig. 4.2 (a) Bit line (BL) and word line (WLs) biases for 1T-DRAM 79 corresponding to bias  $n_{VL} = 3$ .  $V_{WL1} = 0$  V during the read (R) operation correspond to bias scheme for  $n_{VL} = 2$ . Contour plot

- for hole concentration (n<sub>h</sub>) and variation of conduction (CB) and valence (VB) band along the channel direction (z) for (b) Write 1 (W1) and (c) Write 0 (W0) operations.

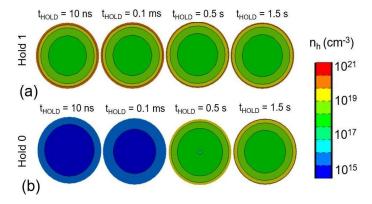

- Fig. 4.3 Contour plots showing hole concentration (n<sub>h</sub>) with hold time 80 (t<sub>HOLD</sub>) during (a) Hold 1 (H1), and (b) Hold 0 (H0) operations at mid-CG position.

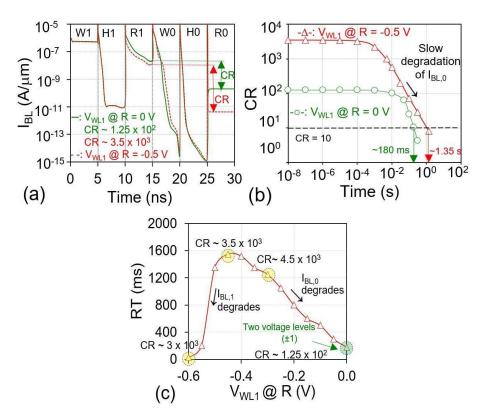

- Fig. 4.4 (a) Current transient for different CG read biases  $V_{WL1}$  (= 0 V 81 with  $n_{VL}$  = 2 and -0.5 V with  $n_{VL}$  = 3). (b) Variation of current ratio (CR) with  $t_{HOLD}$  for  $V_{WL1}$  = 0 V and -0.5 V. (c) Retention time (RT) as a function of  $V_{WL1}$  ( $n_{VL}$  = 3).

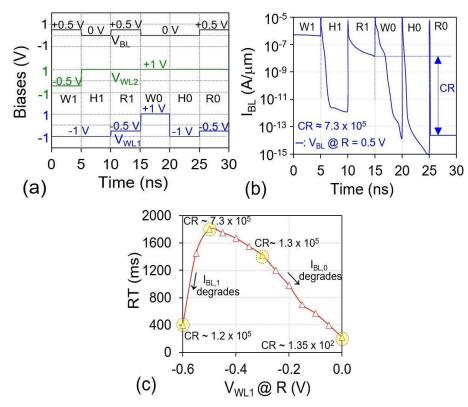

- Fig. 4.5 (a) Bit line (BL) and word line (WL) biases for 1T-DRAM 83 corresponding to bias  $n_{VL} = 4$ . (b) Current transient showing 1T-DRAM operations for  $n_{VL} = 4$ . (c) Retention time (RT) as a function of  $V_{WL1}$  ( $n_{VL} = 4$ ).

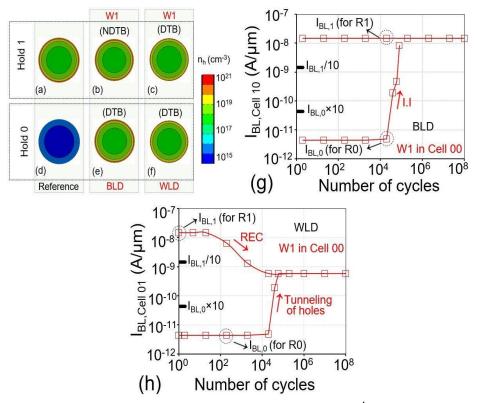

- Fig. 4.6 Contour plots, extracted at mid-CG position after 10<sup>4</sup> cycles, showing hole concentration n<sub>h</sub> after H1 state for (a) reference cell (independent cell), (b) cell 10 after W1, (c) cell 01 after W1. Hole concentration n<sub>h</sub> after H0 state for (d) reference cell (independent cell), (e) cell 10 after W1, (f) cell 01 after W1. (g) Impact of BL disturbance on I<sub>BL,1</sub> and I<sub>BL,0</sub> of cell 10 due to W1 (n<sub>VL</sub> = 3). (h) Impact of WL disturbance on I<sub>BL,1</sub> and I<sub>BL,0</sub> of cell 01 due to W1 (n<sub>VL</sub> = 3). DTB and NDTB denote disturbed or not disturbed.

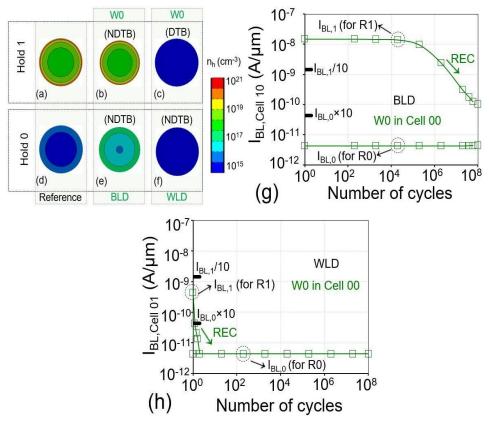

- Fig. 4.7 Contour plots, extracted at mid-CG position after 10<sup>4</sup> cycles, 89 showing hole concentration n<sub>h</sub> after H1 state for (a) reference cell (single cell), (b) cell 10 after W0, (c) cell 01 after W0. Hole concentration n<sub>h</sub> after H0 state for (d) reference cell (single cell), (e) cell 10 after W0, (f) cell 01 after W0. (g) Impact of BL disturbance on I<sub>BL,1</sub> and I<sub>BL,0</sub> of cell 10 due to W0 (n<sub>VL</sub> = 3). (h) Impact of WL disturbance on I<sub>BL,1</sub> and I<sub>BL,0</sub>

of cell 01 due to W0 ( $n_{VL}$  = 3). DTB and NDTB denote disturbed or not disturbed.

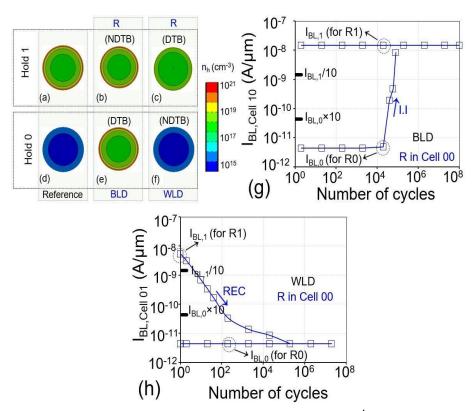

- Fig. 4.8 Contour plots, extracted at mid-CG position after  $10^4$  cycles, showing hole concentration  $n_h$  after H1 state for (a) reference cell (independent cell), (b) cell 10 after R, (c) cell 01 after R. Hole concentration  $n_h$  after H0 state for (d) reference cell (independent cell), (e) cell 10 after R, (f) cell 01 after R. (g) Impact of BL disturbance on  $I_{BL,1}$  and  $I_{BL,0}$  of cell 10 due to R ( $n_{VL} = 3$ ). (h) Impact of WL disturbance on  $I_{BL,1}$  and  $I_{BL,0}$  of cell 01 due to R ( $n_{VL} = 3$ ). DTB and NDTB denote disturbed or not disturbed.

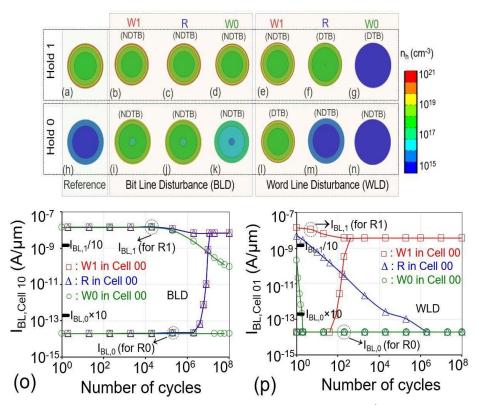

- Fig. 4.9 Contour plots, extracted at mid-CG position after  $10^6$  cycles, 94 showing  $n_h$  for (a) reference cell (independent cell) H1 state and impact of BL disturbance for (b) W1, (c) R, and (d) W0 operations, and WL disturbance for (e) W1, (f) R, and (g) W0 operations for H1 state. Contour plots showing  $n_h$  for (h) reference cell H0 state and impact of BL disturbance for (i) W1, (j) R, and (k) W0 operations, and WL disturbance for (l) W1, (m) R, and (n) W0 operations for H0 state. (o) Impact of BL disturbance on  $I_{BL,1}$  and  $I_{BL,0}$  of cell 10 due to W1, W0, and R operations ( $n_{VL} = 4$ ). (p) Impact of WL disturbance on  $I_{BL,1}$  and  $I_{BL,0}$  of cell 01 due to W1, W0, and R operations ( $n_{VL} = 4$ ). DTB and NDTB denote disturbed or not disturbed.

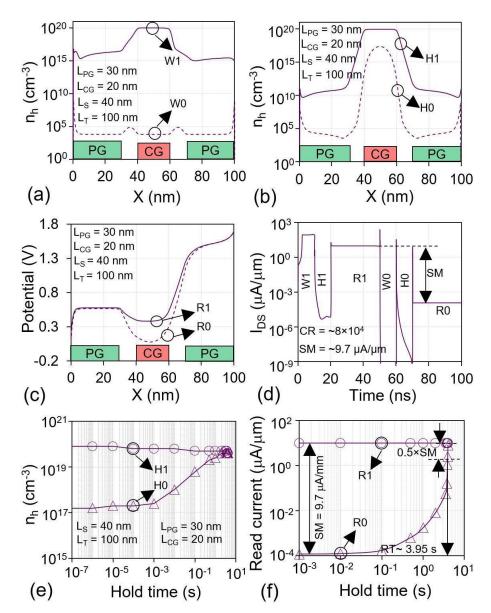

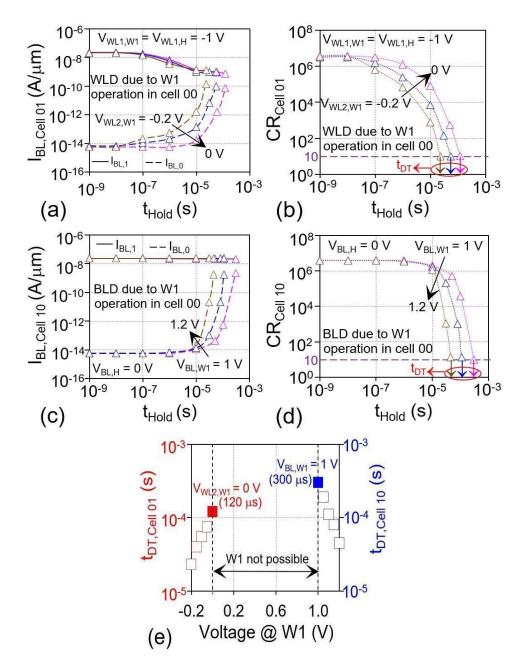

- Fig. 4.10 (a) Bit line currents ( $I_{BL,1}$ ,  $I_{BL,0}$ ) and (b) Current Ratio (CR = 98  $I_{BL,1}/I_{BL,0}$ ) as a function of hold time ( $t_{HOLD}$ ) due to WLD for W1 operation in cell 00. (c) BL currents and (d) CR as a function of  $t_{HOLD}$  due to BLD for W1 operation in cell 00. (e) Dependence of  $t_{DT}$  on WL2 and BL for W1 operation. Since  $V_{WL1,W1} = V_{WL1,H} = -1 \ V$ , WL1 will not contribute towards WLD. Optimal biases for W1 operation are  $V_{WL2,W1} = 0 \ V$ ,  $V_{WL1,W1} = -1 \ V$ , and  $V_{BL,W1} = 1 \ V$ .

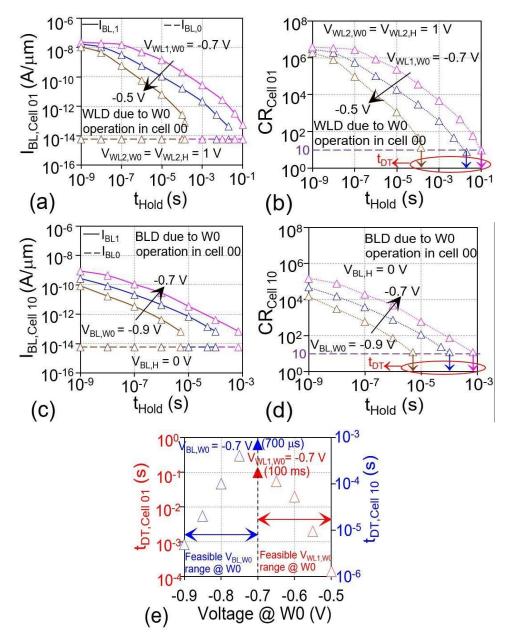

- Fig. 4.11 (a) Bit line currents ( $I_{BL,1}$ ,  $I_{BL,0}$ ) and (b) Current Ratio (CR = 99  $I_{BL,1}/I_{BL,0}$ ) as a function of hold time ( $t_{HOLD}$ ) due to WLD for W1 operation in. (c) BL currents and (d) CR as a function of  $t_{HOLD}$  due to BLD for W1 operation. (e) Dependence of  $t_{DT}$  on WL2 and BL for W1 operation. Since  $V_{WL2,W0} = V_{WL2,H} = 1$  V, WL2 will not contribute towards WLD. Optimal biases for W0 operation are  $V_{WL1,W0} = -0.7$  V,  $V_{WL2,W0} = 1$  V, and  $V_{BL,W0} = -0.7$  V.

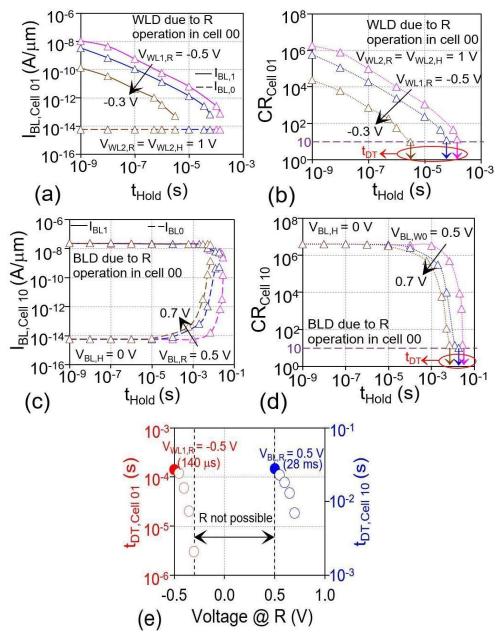

- Fig. 4.12 (a) Bit line currents ( $I_{BL,1}$ ,  $I_{BL,0}$ ) and (b) Current Ratio (CR = 100  $I_{BL,1}/I_{BL,0}$ ) as a function of hold time ( $t_{HOLD}$ ) due to WLD for W1 operation. (c) BL currents and (d) CR as a function of  $t_{HOLD}$  due to BLD for W1 operation. (e) Dependence of  $t_{DT}$  on WL2 and BL for W1 operation. Since  $V_{WL2,R} = V_{WL2,H} = 1 \text{ V}$ , WL2 will not contribute towards WLD. Optimal biases for R operation are  $V_{WL1,R} = -0.5 \text{ V}$ ,  $V_{WL2,R} = 1 \text{ V}$ , and  $V_{BL,R} = 0.5 \text{ V}$ .

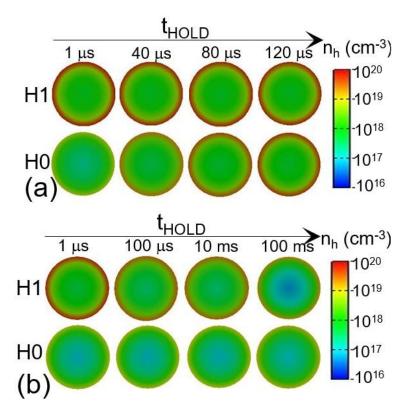

- Fig. 4.13 Mid-CG contour plots for hole concentration  $(n_h)$  for (a) 101 minimum  $t_{DT} = 120 \mu s$  (H0 degradation) and (b) maximum  $t_{DT} = 100 \text{ ms}$  (H1 deterioration).

- Fig. 4.14 Optimized biases for W1, W0 and R operations based on maximum t<sub>DT</sub> values for each operation shown in Figs. 4.10 (e), 4.11 (e) and 4.12 (e). (d) Current (I<sub>BL</sub>) transient in cell 00 for optimized RFET 1T-DRAM. Duration of W1 (t<sub>W1</sub>) and W0 (t<sub>W0</sub>) operations is 10 ns, while that of R operation (t<sub>R</sub>) is 5 ns.

## LIST OF TABLES

| Table No. | Table Title                                                                                   | Page No. |

|-----------|-----------------------------------------------------------------------------------------------|----------|

| Table 2.1 | Bias used for different operations in RFET based 1T-DRAM.                                     | 35       |

| Table 3.1 | Combination of $L_{PG}$ , $L_{GAP}$ , and $L_{CG}$ used in the analysis for $L_{T} = 100$ nm. | 49       |

| Table 3.2 | Bias used for 1T-DRAM in $L_S$ = 40 nm ( $L_{PG}$ = 30 nm, $L_{CG}$ = 20 nm).                 | 49       |

| Table 3.3 | Bias used for 1T-DRAM in $L_S = 80$ nm ( $L_{PG} = 10$ nm, $L_{CG} = 20$ nm).                 | 53       |

| Table 3.4 | Benchmarking of RFET based 1T-DRAM with existing topologies.                                  | 68       |

| Table 3.5 | Retention time (RT) of three different topologies without traps.                              | 72       |

| Table 3.6 | Retention time (RT) of three different topologies with traps.                                 | 72       |

| Table 4.1 | BL bias for cells 10 and 00 in H state and W1/W0/R, respectively ( $n_{\rm vl}$ = 3).         | 85       |

| Table 4.2 | WLs bias for cells 10 and 00 in H state and W1/W0/R, respectively ( $n_{\rm vl}$ = 3).        | 85       |

| Table 4.3 | BL bias for cells 10 and 00 in H state and W1/W0/R, respectively ( $n_{\rm vl}$ = 4).         | 92       |

| Table 4.4 | WLs bias for cells 10 and 00 in H state and W1/W0/R, respectively ( $n_{\rm vl}$ = 4).        | 92       |

| Table 4.5 | Benchmarking results of t <sub>DT</sub> in 1T-DRAM array.                                     | 103      |

Table 4.6 Comparison of write time ( $t_W$ ), read time ( $t_R$ ), and supply voltage ( $V_{DD}$ ) required for optimum RT with existing 1T-DRAM technologies.

### **NOMENCLATURE**

| λ                   | Characteristics/Natural Length                       | nm                |

|---------------------|------------------------------------------------------|-------------------|

| $\lambda_{CYL}$     | Natural Length of Cylindrical MOSFET                 | nm                |

| $\lambda_{DG}$      | Natural Length of Double Gate MOSFET                 | nm                |

| A                   | Constant                                             | $A^{\circ(-1/3)}$ |

| High-K              | Material with High Dielectric                        | Unitless          |

| $I_0$               | Read 0 Current                                       | A                 |

| $I_{I}$             | Read 1 Current                                       | A                 |

| $I_{BL,0}$          | Bit Line 0 Current                                   | A                 |

| $I_{BL,1}$          | Bit Line 1 Current                                   | A                 |

| $I_{DS}$            | Drain Current                                        | A                 |

| K                   | Scaling Factor                                       | Unitless          |

| $L_{CG}$            | Control Gate Length                                  | nm                |

| $L_G$               | Gate Length                                          | nm                |

| $L_{G,min}$         | Minimum Gate Length                                  | nm                |

| $L_{\it GAP}$       | Ungated Region Length                                | nm                |

| $L_{PG}$            | Program Gate Length                                  | nm                |

| $L_S$               | Storage Length                                       | nm                |

| $L_{S}\!\!/\!L_{T}$ | Ratio of Storage Length and Total Length             | Unitless          |

| $L_T$               | Total Length                                         | nm                |

| n                   | Semiconductor Region with Electrons as Majority      | Unitless          |

|                     | Carriers                                             |                   |

| $N_a$               | Acceptor Concentration                               | cm <sup>-3</sup>  |

| $n_e$               | Electron Concentration                               | cm <sup>-3</sup>  |

| $n_h$               | Hole Concentration                                   | cm <sup>-3</sup>  |

| $n_{VL}$            | Number of Voltage Levels                             | Unitless          |

| p                   | Semiconductor Region with Holes as Majority Carriers | Unitless          |

| $T_{BOX}$           | Buried Oxide Thickness                               | nm                |

| $t_{HOLD}$          | Hold Time                                            | S                 |

| $T_{OX}$            | Oxide Thickness                                      | nm                |

| $t_R$        | Read Time                          | S  |

|--------------|------------------------------------|----|

| $T_{Si}$     | Silicon Thickness                  | nm |

| $t_{W0}$     | Write 0 Time                       | S  |

| $t_{WI}$     | Write 1 Time                       | S  |

| $V_{BCG}$    | Back Control Gate Voltage          | V  |

| $V_{BCG,H}$  | Hold Back Control Gate Voltage     | V  |

| $V_{BCG,W0}$ | Write 0 Back Control Gate Voltage  | V  |

| $V_{BCG,WI}$ | Write 1 Back Control Gate Voltage  | V  |

| $V_{BL}$     | Bit Line voltage                   | V  |

| $V_{BL,WI}$  | Bit Line Write 1 Voltage           | V  |

| $V_{CG}$     | Control Gate Voltage               | V  |

| $V_D$        | Drain Voltage                      | V  |

| $V_{D,WI}$   | Write 1 Drain Voltage              | V  |

| $V_{D.H}$    | Hold Drain Voltage                 | V  |

| $V_{D.R}$    | Read Drain Voltage                 | V  |

| $V_{DD}$     | Supply Voltage                     | V  |

| $V_{DS}$     | Drain to Source Voltage            | V  |

| $V_{FCG}$    | Front Control Gate Voltage         | V  |

| $V_{FCG,WI}$ | Write 1 Front Control Gate Voltage | V  |

| $V_{FCG.H}$  | Hold Front Control Gate Voltage    | V  |

| $V_{FCG.R}$  | Read Front Control Gate Voltage    | V  |

| $V_{PG}$     | Program Gate Voltage               | V  |

| $V_{PG,WI}$  | Write 1 Program Gate Voltage       | V  |

| $V_{PG.H}$   | Hold Program Gate Voltage          | V  |

| $V_{PG.R}$   | Read Program Gate Voltage          | V  |

| $V_S$        | Source Voltage                     | V  |

| $V_{S.H}$    | Hold Source Voltage                | V  |

| $V_{S.R}$    | Read Source Voltage                | V  |

| $V_{TH}$     | Threshold voltage                  | V  |

| $V_{WLI}$    | Word Line 1 Voltage                | V  |

| $V_{WLI,H}$  | Word Line 1 Hold Voltage           | V  |

| $V_{WLI,R}$         | Word Line 1 Read Voltage          | V   |

|---------------------|-----------------------------------|-----|

| $V_{WL1,W0}$        | Word Line 1 Write 0 Voltage       | V   |

| $V_{WLI,WI}$        | Write 1 Word Line 1 Voltage       | V   |

| $V_{WL2}$           | Word Line 2 Voltage               | V   |

| $V_{WL2,H}$         | Word Line 2 Hold Voltage          | V   |

| $V_{WL2,R}$         | Word Line 2 Read Voltage          | V   |

| $V_{WL2,W0}$        | Word Line 2 Write 0 Voltage       | V   |

| $V_{WL2,W1}$        | Write 1 Word Line 2 Voltage       | V   |

| $W_D$               | Drain Depletion Width             | nm  |

| $W_S$               | Source Depletion Width            | nm  |

| $X_j$               | Junction Depth                    | nm  |

| $\Delta V$          | Potential Change                  | V   |

| $\mathcal{E}_{ins}$ | Permittivity of Insulator/Oxide   | F/m |

| $\mathcal{E}_{Si}$  | Permittivity of Silicon           | F/m |

| $V_{BL,W0}$         | Bit Line Write 0 Voltage          | V   |

| $V_{BL,R}$          | Bit Line Read Voltage             | V   |

| $I_{BL}$            | Bit Line Current                  | A   |

| $t_{DT}$            | Duration of Disturbance Tolerance | S   |

#### **ACRONYMS**

0C Zero Capacitor

1T *OneTransistor*

1T0C One Transistor Zero Capacitor

1T1C One Transistor One Capacitor

2G Twin Gate

2T Two Transistor

2T0C Two Transistor Zero Capacitor

3D Three-Dimensional

4T0C Four Transistor Zero Capacitor

ALU Arithmetic Logic Unit

AR Aspect Ratio

BCG Back Control Gate

BL Bit Line

BLD Bit Line Disturbance

BOX Buried Oxide Layer

BTBT Band-to-Band Tunneling

CB Conduction Band

CG Control Gate

CMOS Complementary Metal-Oxide-Semiconductor

CMP Chemical Mechanical Polishing

CR Current Ratio

DEC Digital Equipment Corporation

DG Double Gate

DIBL Drain-Induced Barrier Lowering

DRAM Dynamic Random Access Memory

DTB Disturb

EOT Equivalent Oxide Thickness

F Feature Size

FCG Front Control Gate

FD Fully Depleted

FDSOI Fully Depleted Silicon on Insulator

FET Field-Effect Transistors

FOM Figure of Merit

GAA Gate All Around

H Hold

H0 Hold 0

H1 Hold 1

HCE Hot Carrier Effect

IMOS Impact ionization Metal Oxide Semiconductor

M Metal

MAJ *Majority*

MBC Multi-Bridge Channel

MOS Metal-Oxide-Semiconductor

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

M-S Metal-Semiconductor

NDTB No Disturb

nMOS *N-Type Metal-Oxide-Semiconductor*

NW Nanowire

P Parameter

PD Partially Depleted

PG Program Gate

pMOS P-Type Metal-Oxide-Semiconductor

R Read

R0 Read 0

R1 Read 1

RFET Reconfigurable Field-Effect Transistor

RT Retention Time

RT/RT<sub>max</sub> Ratio of Retention Time with Maximum Retention Time

RT<sub>max</sub> Maximum Retention Time

S Semiconductor

SB Schottky Barrier

SBH Schottky Barrier Height

SCE Short Channel Effect

S<sub>FOM</sub> Figure of Merit for Process Sensitivity

SiO<sub>2</sub> Silicon DioxideSM Sense MarginSOC System on Chip

SOI Silicon on Insulator

SRAM Static Random Access Memory

T Temperature

TFET Tunnel Field Effect Transistor

TG Twin Gate

UTB *Ultra-Thin Box*

UTBB Ultra-Thin Body Buried Oxide Layer

VAX Virtual Address Extension

VB Valence Band

W0 Write 0W1 Write 1

WL Word Line

WL1 Word Line 1

WL2 Word Line 2

WLD Word Line Disturbance

WLs Word Lines

X Along the Channel Direction in Planar RFET

XOR Exclusive-OR

Z Along the Channel Direction in Nanowire RFET

Z<sup>2</sup>FET Zero Impact Ionization and Zero Subthreshold Swing Field-Effect Transistor

ΔFOM Change in Figure of Merit

$\Delta P$  Change in Parameter

#### Chapter 1

#### Introduction

The number of transistors in a semiconductor chip has increased tremendously due to in-depth understanding of transistor physics and operation, and key advancements in processing, fabrication, and characterization [1-8]. This increase in transistor density has followed the empirical prediction of G. Moore [9-20]. The transistor density in the chip has increased since the invention of Intel's 4004 microprocessor, which had 2300 transistors in an area of an eighth of an inch [21]. In stark contrast, Apple's M1 chip contains 57 billion transistors within a die size slightly less than one square inch [22].

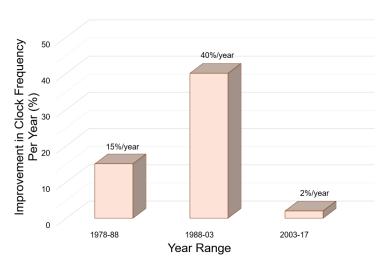

Fig. 1.1 Growth in processor clock frequency from 1978 to 2017 (39 years) [5].

While the semiconductor industry has leveraged innovations in transistors, interconnects, and fabrication processes [7-8], [23-29], the clock rate enhancement of microprocessors, as illustrated in Fig. 1.1, has increase and then decreased over the 39 years from 1978 to 2017. The available data shows a 15 percent increase per year in microprocessor clock rate in the initial years (1978 to 1988) of the microelectronic industry [5]. The clock rate further enhanced to 40 percent per year

from 1988 to 2003, and thereafter to a meager 2 percent improvement per year was observed from 2003 to 2017. The key point is that the increase in the clock rate (per year) has been relatively insignificant since 2003 [5]. The other interesting parameter is to compare the performance of modern processors with respect to the initial computer developed in 1977. The Virtual Address Extension (VAX) model 11/780 was one of the first pioneering computers developed in 1977 by the Digital Equipment Corporation (DEC) [5], [30]. Since 1978, the improvement in processor performance has been variable with respect to VAX 11/780.

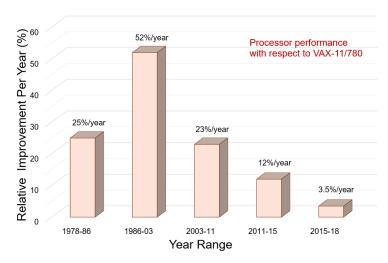

Fig. 1.2 Growth in processor performance from 1978 to 2018 (40 years) [5].

As shown in Fig. 1.2, the trends for the 40-year period (1978 to 2018) indicate that the initial years (1978 to 1986) saw an increase of 25 percent per year in processor performance relative to VAX 11/780 [5]. Thereafter, the enhancement in processor performance increased to a significantly high value of 52 percent per year (relative to VAX 11/780) from 1986 to 2003 [5]. The growth then subsided (slowed down) to 23 percent per year (with respect to VAX 11/780) from 2003 to 2011. Subsequently, the improvement in processor performance was 12 percent per year (concerning VAX 11/780) from 2011 to 2015, and 2.5 percent per year (relative to VAX 11/780) from 2015 to 2018 [5]. These results indicate that the rate of improvement in the performance of processors has been slowing down. The data also suggests that the semiconductor industry may not be able to continue following the empirical observation of Moore [20]. Although processor performance has not

seen significant enhancements, the micro/nano electronic industry has achieved remarkable progress through innovations in transistor architecture, fabrication, characterization, and packaging technologies.

#### 1.1 Downscaling Bulk Metal-Oxide-Semiconductor Transistor

A fundamental requirement for the transistor is to function as a switch, with 'low' current in the off-state and 'high' current in the on-state. Besides, the transition from one state to another is governed by capacitances, which should be small to facilitate fast switching [31]. The evolution of transistor architecture from conventional planar (two-dimensional) to nanosheet or nanowire (threedimensional), coupled with innovation through Silicon-on-Insulator (SOI) technology, has largely contributed to enhancing transistor density in modern chips [7]. The fabricated transistors in the 1970s had a gate length (L<sub>G</sub>) of several 100 micrometers. However, to enhance the transistor density in the chip without compromising the performance of transistors, a reduction in the dimensions of the transistor was inevitable. However, a decrease in gate length of a bulk Metal Oxide Semiconductor (MOS) Field Effect Transistor (FET) can result in the space charge region at the drain being close to the space charge region at the source [23]. This reduces the control of the gate over the channel, and an electron could leak from source to drain, which increased the off-current of the transistor. This condition, detrimental to the functioning of the transistor as a switch, is known as short channel effect (SCE) [6], [23], and its suppression is foremost to enable downscaling of MOSFET.

The scaling down of the gate length of the transistor resulted in two-dimensional effects that impacted the current-voltage characteristics. The most prominent among them was the lowering of threshold voltage (V<sub>TH</sub>) and drain-induced barrier lowering (DIBL) [6], [23]. Both these contributed to an undesired increase in the off-current of the transistor and a degradation of the on-to-off current ratio. In the on-state, the reduction of gate length is beneficial as it enables an increase in the current. However, care should be taken that the increase in drain

current is accompanied by a reduction in source/drain resistances [23]. Also, gate length scaling supports a decrease in capacitance. For capacitance, the gate length downscaling should be accompanied by a reduction in the fringing components as compared to the channel capacitance [23].

The downscaling of MOSFET was primarily attributed to the scaling theory proposed by Dennard et al. [32]. This resulted in the formulation of methodology for the miniaturization of MOSFETs. The theory of Dennard et al., [32] suggested to increase or decrease parameters of MOSFET by the scaling factor (K). The data from 1972 to 1992 (two decades) showed an increase in number of transistors (6000 to 3000000) and power consumption (20 mW to 10 W) by 50 times each for a reduction in gate length from 6 µm to 0.4 µm [23]. The actual scaling adopted by the semiconductor industry was different from the ideal theory proposed by Dennard et al. [32]. The primary contributor to this difference was supply voltage (V<sub>DD</sub>) downscaling. The supply voltage was maintained constant to obtain the benefit of high-speed operation [31-33]. Another challenge in V<sub>DD</sub> reduction was the reduction in V<sub>TH</sub>. The non-adherence of V<sub>DD</sub> downscaling was a factor contributing to the high power consumption. The increase in the number of transistors exceeded the projected factor K<sup>2</sup> [31-32]. For each technology generation, the transistor size was reduced by a factor of K (= 0.7, and the area by  $K^2$  (= 0.7 × 0.7  $\approx$  0.5). This would have resulted in an increase in transistor count by a factor of 2 (= 1/0.5). However, the actual transistor count increased by a factor of 4 due to an increase in chip area by a factor of 1.5 [31]. The increase in power consumption was also due to higher number of transistors on a chip.

The industry adopted actual (or pragmatic) scaling described above by clearly identifying challenges for bulk MOSFET downscaling below 0.1  $\mu$ m. An alternate methodology was suggested to enable MOSFET downscaling from 0.1  $\mu$ m to 40 nm [34-37]. The approach considered maintaining constant values of substrate doping concentration ( $10^{18}$  cm<sup>-3</sup>), gate oxide (3 nm), and supply voltage (1.5 V) to enable scaling of gate length from 0.1  $\mu$ m to 40 nm. The parameter which was aggressively scaled (×(1/4)) was junction depth (x<sub>i</sub>), i.e., from 40 nm (L<sub>G</sub> = 100)

nm) to 10 nm ( $L_G = 40$  nm) [34-37]. The result was complete control over SCEs and hot carrier effects (HCEs) with a 30% increase in the on-current. The downside of the approach was high resistance of ultra-shallow source/drain regions due to aggressively scaled junction depth. Various modifications in the downscaling approach were attempted [36-39] to overcome these challenges. One approach was to limit the aggressive scaling of L<sub>G</sub> and x<sub>i</sub> to 70 nm and 30 nm, respectively, and instead reduce oxide thickness (Tox) from 3 nm to 1.5 nm while maintaining constant V<sub>DD</sub> (1.5 V) and substrate doping (10<sup>18</sup> cm<sup>-3</sup>). This resulted in a high oncurrent of 1.4 mA/µm and an extremely small direct tunneling leakage current of 2  $nA/\mu m$  [31]. Although ultra-shallow (14 nm) bias controlled  $x_i$  was achieved with additional gates placed over the gate [40], the drawback of such an approach was low on-current (two to three orders lower) in comparison to conventional bulk MOSFET. Based on the different approaches and results of bulk MOSFET, the transistor architecture for downscaling was envisaged to have elevated source/drain regions with an insulator sidewall of 5 nm. For a bulk MOSFET with 5 nm of x<sub>i</sub>, the minimum L<sub>G</sub> should be around 25 nm with T<sub>OX</sub> limited to 1.2 nm to avoid SCEs [31]. Besides the technological challenges in ensuring the above criteria, capacitance is indeed critical for speed. The fringing capacitance should not be allowed to be a substantial component of the total gate capacitance. The channel doping concentration was limited to  $10^{18}\ \mathrm{cm^{\text{-}3}}$  to reduce parasitic capacitance, mobility degradation, and random dopant fluctuations governed by V<sub>TH</sub> variability [33].

#### 1.2 Silicon-on-Insulator MOSFET

The problems with the downscaling of bulk MOSFETs can be understood by the following equation, which relates the minimum gate length ( $L_{G,min}$ ) with key transistor parameters.

$$L_{G,min} = (A) (T_{ox}x_j(W_S + W_D)^2)^{(1/3)}$$

(1.1)

where  $A = 0.41 \text{ A}^{\circ(-1/3)}$ ,  $W_S$  and  $W_D$  are source and drain depletion widths [41-42]. For a given technology, doping  $(N_a)$  required for eq. (1.1) can be obtained [41] as

$$N_{a} \ge (1.8 \times 10^{17}) \left(\sqrt{V_{BI}} + \sqrt{V_{BI} + V_{DS}}\right)^{2} \left(\frac{x_{j}}{50 \text{ nm}}\right) \left(\frac{0.1 \mu m}{L_{G,min}} \frac{T_{OX}}{4 \text{ nm}}\right)^{3}$$

(1.2)

where V<sub>BI</sub> and V<sub>DS</sub> represent built-in voltage and drain bias, respectively.

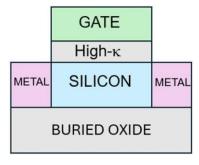

As gate length is scaled down, the substrate doping increases, which causes several issues for nanoscale MOSFET [1-3]. The problem associated with downscaling can be circumvented if the vertical extension of the depletion width can be limited without increasing the substrate doping. This is possible through SOI technology, which dissociates the dependence of substrate doping and depletion width, provided the semiconductor (Silicon) layer thickness is less than the depletion depth at zero bias. As shown in Fig. 1.3 (a)-(b), SOI MOSFET can be fabricated with thick and thin semiconductor layers [1], [3], [7]. The thick semiconductor region (Fig. 1.3 (a)) will allow partial depletion at zero applied bias and is classified as a partially depleted (PD) SOI MOSFET. The SOI MOSFET with a thin Silicon layer (Tsi) is fully depleted at zero bias, and hence, the architecture is referred to as a fully depleted (FD) SOI MOSFET [3], [7], [43-45]. In terms of scaling, FD SOI MOSFET holds promise as SCEs can be effectively controlled. SOI MOSFET architectures with a thin Silicon layer are generally referred to as ultra-thin body (UTB) MOSFETs [1], [7].

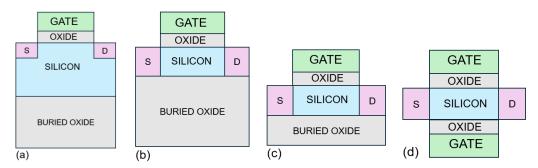

**Fig. 1.3** Schematic representation of SOI MOSFET with relatively (a) thick semiconductor layer, (b) thin semiconductor layer, (c) thin buried oxide layer, and (d) double gate architecture. The substrate region (below the buried oxide) is not shown as the focus is on the active semiconductor layer [7].

Apart from reducing the Silicon film thickness, the lateral electric field (associated with the voltage at the drain) also flows through the buried oxide (BOX)

layer. This path of the lateral electric field can be curtailed by reducing the thickness of the BOX layer [46] (Fig. 1.3 (c)). MOSFET comprising of thin Silicon (body) and thin BOX is generally referred to as ultra-thin body BOX (UTBB) MOSFET [1]. Further downscaling of the gate length while maintaining an undoped body can be achieved if the thickness of the buried oxide is kept similar to the front oxide thickness, and another (second) gate is fabricated below the thin buried oxide. This structure, shown in Fig. 1.3 (d), is referred to as the double gate (DG) SOI MOSFET [1], [47].

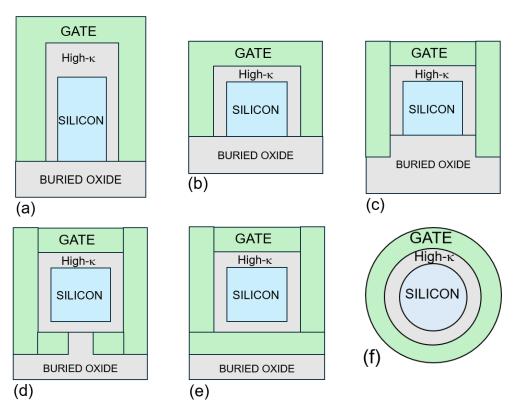

**Fig. 1.4** Schematic representation of multi-gate MOSFET cross-section (perpendicular to current flow) for (a) vertical dual gate, (b) triple gate, (c) pi gate, (d) omega gate, (e) quadruple gate, and (f) cylindrical nanowire architecture [1].

FDSOI technology resulted in lower parasitic capacitance, and the strong control of the gate over the channel potential, which was instrumental in lowering the off-current with respect to bulk Silicon technology [3], [7]. Further scaling of transistor dimensions was facilitated through a reduction in BOX thickness ( $T_{BOX}$ ) and semiconductor layer thickness ( $T_{Si}$ ). In addition to  $T_{Si}$  and  $T_{BOX}$ , the gate oxide

thickness ( $T_{OX}$ ) was also reduced through the incorporation of high permittivity (high- $\kappa$ ) material and metal gate. The most relevant parameter for the high- $\kappa$  gate stack is the equivalent oxide thickness (EOT) which allows a direct reference with respect to silicon dioxide ( $SiO_2$ ) layer. The available data for the 28 nm technology node specifies a  $T_{BOX}$  of 25 nm,  $T_{Si}$  of 7 nm, and EOT of 1.2 nm. Mathematically, the ability of a transistor architecture to limit SCEs can be evaluated through an estimation of natural/characteristic length ( $\lambda$ ) [41] through the solution of Poisson's equation with appropriate boundary conditions [48-50].  $\lambda$  depends on the vertical dimensions ( $T_{OX}$ ,  $T_{Si}$ ), permittivity of insulator ( $\epsilon_{ins}$ ) and Silicon ( $\epsilon_{Si}$ ) and on the location of conduction channel in the semiconductor. For a planar DG SOI MOSFET shown in Fig. 1.3 (d),  $\lambda_{DG}$  can be obtained [48] as,

$$\lambda_{DG} = \sqrt{\left(\frac{\varepsilon_{Si} T_{Si} T_{ox}}{2\varepsilon_{ins}}\right) \left(1 + \frac{\varepsilon_{ox} T_{Si}}{4\varepsilon_{Si} T_{ox}}\right)}$$

(1.3)

To limit SCEs,  $(L_G/2\lambda)$  should be at least greater than 5. Similarly, a cylindrical nanowire MOSFET [51] is expected to further downscale in comparison to planar MOS architectures as the gate surrounds the Silicon region from all sides [2], [52]. The natural length  $(\lambda_{CYL})$  for a cylindrical nanowire MOSFET under the approximation  $T_{Si}/2 >> T_{OX}$  [50] can be expressed as

$$\lambda_{CYL} = \sqrt{\left(\frac{\varepsilon_{Si} T_{Si} T_{ox}}{4\varepsilon_{ins}}\right) \left(1 + \frac{\varepsilon_{ox} T_{Si}}{4\varepsilon_{Si} T_{ox}}\right)}$$

(1.4)

Since the fabrication of vertical dual gate [53] and gate-all-around [54] structures, the MOSFET architecture has considerably evolved (since the late 90s) through the demonstration of planar double gate SOI transistor, vertical (three-dimensional) finFET (Fig. 1.4 (a)), trigate transistor (Fig. 1.4 (b)), pi-gate transistor (Fig. 1.4 (c)), omega gate MOSFET (Fig. 1.4 (f)), quadruple gate transistor (Fig. 1.4 (f)), and nanowire (cylindrical) MOSFET (Fig. 1.4 (f)) [1], [43-45]. These architectures (collectively referred to as multiple gate MOSFETs) essentially increased the control of the gate over the channel through a higher number of gates, and the influence of the drain (lateral) electric field over the channel was consequently suppressed.

**Fig. 1.5** Schematic representation of cross-section (perpendicular to current flow) of (a) multi-bridge-channel MOSFET [55-56], (b) forksheet MOSFET [57-59], and (c) complementary MOSFET [60-61].

While SCEs could be minimized through multiple gate transistors, the current drive in the on-state was limited by the volume of the semiconductor. An increase in semiconductor dimensions (volume) could certainly ease constraints for device fabrication, but could result in SCEs, and consequently, higher off-current. A way to overcome this problem was through the extension of transistor architecture in the vertical direction. This concept was effectively demonstrated in 2002 through the fabrication of a multi-bridge channel (MBC) transistor (Fig. 1.5 (a)) by Samsung [55-56]. Since then, different adaptations of the three-dimensional transistor architecture, such as nanosheet and forksheet transistor (Fig. 1.5 (b)) [57-59] and complementary MOSFET (Fig. 1.5 (c)) [60-61] have evolved. The critical aspect to be noted is that the aspect ratio (AR = height/width) of the semiconductor region in a scaled-down transistor has been largely limited to < 1, i.e., the height of the semiconductor film is lower than its width (separation between two lateral gates).

## 1.3 Schottky Barrier MOSFET

One of the major concerns of downscaling MOSFET is the reduction in channel resistance which tends to emphasize the importance of ideal source/drain contacts. This reduction can be described through the increase in sheet resistance of ultra-shallow source/drain regions [62-63]. Therefore, the use of metal source/drain can bypass the limitations of contact resistivity [64]. The source/drain Schottky contact can overcome this problem due to the nearly ideal silicide-silicon interface and low sheet resistance [65]. The reduction in thermal budget enabling integration with metal gate is another advantage of Schottky source/drain regions [66]. A MOSFET with metal source/drain instead of conventional doped source/drain is generally referred to as Schottky barrier (SB) MOSFET [67] is shown in Fig. 1.6. The concept of SB MOSFET was originally proposed by Nishi [68] in 1966. The patent was granted for the same in 1970. To enable circuits with SB MOSFETs either midgap silicide with barrier height nearly equal to half of the Silicon bandgap or complementary silicide (platinum silicide, erbium silicide, ytterbium silicide) which provide two different barrier heights for n-type (low barrier to electrons) or p-type (low barrier for holes) operation [67], [69]. SB MOSFETs have been shown to be cost effective, energy efficient and scalable in comparison to MOSFETs with doped source/drain regions [67], [70-71]. SB MOSFETs may find applications in low-temperature electronics as source/drain contacts do not freeze out at low temperatures [69].

While a metal source/drain can result in lower resistance than that offered by the doped counterpart, a barrier is always present during the device operation. Hence, the resistance essentially re-emerges in the device operation and lowers the current drive [69]. In addition, the problem of higher off-current in SB MOSFETs has also been reported in the literature [67], [69]. The higher junction leakage current in SB MOSFET can contribute to ambipolar behavior [69].

Fig. 1.6 Schematic representation of Schottky barrier (SB) MOSFET [67].

#### 1.4 Reconfigurable Transistors

In order to avoid control of source/drain dopants close to the gate edge, the use of metal source/drain is an interesting alternative. The workfunction of metal contact should be near the midgap energy of the semiconductor. SB MOSFETs, although an interesting choice for dopant free transistor, have been plagued by ambipolar behavior which needs to be suppressed through an appropriate mechanism [72]. Moreover, despite critical innovations in the transistor architecture and reduction of parasitic components, a fundamental limitation of metal-oxide-semiconductor (CMOS) technology complementary the requirement of separate n-type and p-type transistors to implement logic circuits. If the polarity (type of transistor) could be obtained through bias in the same structure (device) then separate transistors would not be needed for implementing logic circuits. This is true for MOSFETs with Ohmic or Schottky source/drain contacts. As conventional doped source/drain MOSFET is scaled down, the control of source/drain doping near to the gate edge would be challenging [72-77]. Additionally, since the hole mobility is typically lower than that of electrons in Silicon, the current drive of a p-type transistor is lower than that of n-type. The current drive of p-type transistor is generally enhanced by increasing the width of the transistor. This would result in an increase in the layout area of the transistor. Additionally, the semiconductor should be intrinsic to avoid any influence of doping on transistor operation and limit variability.

To achieve n-type or p-type conduction from the same device, the following three possibilities exist:

(i) Selective carrier injection through two independent gates modulating the metalsemiconductor contacts in 2-gated configuration:

In this architecture shown in Fig. 1.7 (a), one of the gates is required for selective carrier injection while the other blocks the flow of opposite type of carrier. This architecture does not require any gate over the middle of the semiconductor (channel) region. Since source/drain are symmetric, any one gate can be utilized to ensure selectivity, i.e., one type of carrier in the channel, while the other gate can

tune the conductance through the channel of allowed carriers. Fully symmetric current-voltage characteristics and logic circuits have been experimentally demonstrated through the concept.

(ii) Selective carrier injection through simultaneous modulation of metalsemiconductor contacts with an additional gate for channel charge control in a 3gated configuration:

In this topology shown in Fig. 1.7 (b), two gates modulate selectivity by enabling the desired carrier through the Schottky contact while the channel conduction is governed through the additional gate which controls the thermionic barrier. The number of gates in this topology is higher than the previous architecture. Vertically stacked nanowires have been experimentally demonstrated using this topology.

(iii) Carrier selection and injection through front and back gates through 2-gated configuration:

As shown in Fig. 1.7 (c), a back gate positioned below source/drain allows injection of both type carriers which are filtered (polarity checked) in channel through the bias at the top gate. The back gate facilitates ambipolar characteristics similar to that exhibited by SB MOSFET.

All the above architectures (Fig. 1.7 (a)-(c)) have been used to demonstrate a universal transistor, referred to as reconfigurable transistor (RFET), that can function either as n-type or p-type through applied bias. The essential aspect of RFET is to introduce mobile carriers through applied voltage [76]. Hence, depending on the polarity of voltage, either electrons or holes can be injected into the channel. A minimum of two independent gates are required to realize RFET operation [75].

The research on RFETs started in 2000 in Taiwan [78-79], and the early phase of development was from 2000 to 2008, growth was witnessed from 2010-2013 and functional diversification of RFETs was observed from 2014 to 2020 [76]. Initially, the concept of two gates was used to limit the high off-currents in SB transistors. One gate (called as main gate) was placed at the source side while the

other (sub-gate), separated from the main gate by passivation oxide, was placed over the entire channel [78]. The net result was a reduction in off-current and onto-off current ratio of  $10^6$  [79]. The word 'reconfigurable' was first introduced in 2011 by Heinzig *et al.*, in the work which demonstrated independent control of Schottky junctions in a 2-gated nanowire heterostructure transistor which exhibited on-to-off current ratio of  $10^9$  [80].

**Fig. 1.7** Schematic representation of (a) 2-gated RFET (b) 3-gated RFET, and (c) 2-gated (front and back) RFET architecture [74]. Notations: PG and CG represent program gate and control gate, respectively.

The circuit (inverter) functionality of RFETs was also demonstrated through nanowire transistors with nearly equal electron and hole conduction [81]. Also, a 3-gated RFET was fabricated with vertically stacked nanowires exhibiting n-type as well as p-type functionality with on-to-off current ratio of

10<sup>6</sup> and near ideal subthreshold swing [82]. In addition, exclusive-OR logic (XOR) operation was also demonstrated with 3-gated RFET [83-84]. It was shown that RFETs allow XOR and majority (MAJ) gates to be implemented with lower transistor count than traditional CMOS [82-83]. Research on RFETs has largely focused on fabrication and characterization [85-115], circuit realization [116-132], implementing ferroelectric dielectric layers [133-136], exploiting negative differential resistance [137-138], implementing binary neural network [139], application in hardware security [140], compact modeling [141-145], and analog/RF applications [146-148].

#### 1.5. Comparison with Conventional MOSFETs

A comparison of 3-gated RFET (Fig. 1.7 (b)) with conventional DG FDSOI transistor (Fig. 1.3 (d)) reveals that the total source-to-drain length (L<sub>T</sub>) is longer in RFET than that in MOSFET (for the same gate length). This is because of more gates, control gate (CG), and program gate (PG), and the mandatory separation between the gates ( $L_{GAP}$ ). Intuitively, the longer  $L_T$  may not appear to support the downscaling of RFET along the channel direction. However, the presence of a greater number of gates (control and program) allows for dynamic programming which enhances the multifunctionality of RFETs for circuit design [73-78]. In other words, comparison between RFET and MOSFET should be carried out at the circuit level and not through the evaluation of a single device. An inverter with RFET and conventional CMOS technology requires 2 transistors each along with a logical effort of 1 for both [120]. This might appear to be disadvantageous for RFET as a single device would require more footprint owing to the longer L<sub>T</sub>. However, the comparison between RFET and CMOS technology becomes interesting if a 3input NAND or 3-input NOR is designed.

Both logic realizations would require 4 RFETs as compared to 6 FDSOI transistors in CMOS technology [120]. Additionally, the total logical effort would be 5 for implementing 3-input NAND and 7 for 3-input NOR in

conventional CMOS technology. However, for RFET based logic design, the total logical effort would be 3 for implementing both NAND or NOR logic. Similarly, 2-input XNOR implementation requires 8 CMOS transistors whereas RFET count is expected to be 4.

In short, innovative approaches towards circuit design using RFETs are required for a fair performance comparison with CMOS technology. An interesting aspect of the same is through a comparison of 1-bit arithmetic logic unit (ALU) designed with RFET and CMOS technology. Results [120] indicate that 30% area benefit is achieved with respect to CMOS technology if 1-bit ALU is designed efficiently through dynamic programming facilitated by RFET. However, if the same circuit is used as applicable for CMOS technology with RFET then 71% more area is required due to longer L<sub>T</sub> of RFET. The reported results also indicate that the reduced critical path in efficient logic design through RFETs contributes to better performance of the 1-bit ALU. The functional range of RFET based 1-bit ALU has also been shown to be higher in comparison with traditional CMOS ALU [120]. In addition, another interesting study proposes the efficient approach of sea-of-tiles to improve manufacturability of RFET circuits [131].

**Fig. 1.8** Schematic representation of 3-gated RFET utilized for implementing capacitorless 1T-DRAM. Notations: PG and CG represent program gate and control gate, respectively.

### 1.6 Memory Architecture

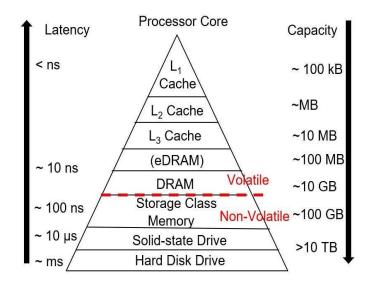

A von Neumann computing architecture is followed in modern computer systems for data processing. In this system, the data is processed by the processor core and stored in memory. In a memory hierarchy [149], memory with the lowest latency (static random access memory (SRAM)) is placed close to the processor core. In contrast, memory with higher latency is placed in lower levels of the memory hierarchy. The SRAM requires a higher number of transistors (8-16) to store the data, which reduces its area efficiency. The processor searches for data in higher levels (L1, L2, L3) of the memory hierarchy (Fig. 1.9). The memory with higher capacity (hard disk drive) lags in latency (in ms). The latency and capacity are both crucial for the processing of data through the processor core. This gap is filled by placing dynamic random access memory (DRAMs) between the SRAM (used for L1 cache to L3 cache levels) and hard disk drives, solid-state drives, and storage-class memory used at lower levels. DRAMs offer the benefits of lower latency (< 10 ns) and moderate capacity (~10 GB). Due to lower latency (< 10 ns) and higher integration density, DRAM is also used in level 4 cache as embedded DRAM memory [149].