# DESIGN OPTIMIZATION OF DOUBLE GATE JUNCTIONLESS MOSFET FOR ENHANCED SHORT CHANNEL IMMUNITY

Ph.D. Thesis

By NIVEDITA JAISWAL

# DISCIPLINE OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE NOVEMBER 2019

# DESIGN OPTIMIZATION OF DOUBLE GATE JUNCTIONLESS MOSFET FOR ENHANCED SHORT CHANNEL IMMUNITY

### A THESIS

Submitted in partial fulfillment of the requirements for the award of the degree of DOCTOR OF PHILOSOPHY

> by NIVEDITA JAISWAL

# DISCIPLINE OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE NOVEMBER 2019

# **INDIAN INSTITUTE OF TECHNOLOGY INDORE**

### **CANDIDATE'S DECLARATION**

I hereby certify that the work which is being presented in the thesis entitled **DESIGN OPTIMIZATION OF DOUBLE GATE JUNCTIONLESS MOSFET FOR ENHANCED SHORT CHANNEL IMMUNITY** in the partial fulfillment of the requirements for the award of the degree of **DOCTOR OF PHILOSOPHY** and submitted in the **DISCIPLINE OF ELECTRICAL ENGINEERING**, **Indian Institute of Technology Indore**, is an authentic record of my own work carried out during the time period from December 2015 to November 2019 under the supervision of Dr. Abhinav Kranti, Professor, Discipline of Electrical Engineering, Indian Institute of Technology Indore.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other institute.

Signature of the student with date (NIVEDITA JAISWAL)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

A711/1/19

Signature of Thesis Supervisor with date

#### (Prof. ABHINAV KRANTI)

NIVEDITA JAISWAL has successfully given her Ph.D. Oral Examination held on May 22, 2020.

Signature of Chairperson (OEB) Date: May 22, 2020

Signature of PSPC Member #1 Date: May 22, 2020

22/05/2020.

Signature of Head of Discipline Date: May 22, 2020

Signature of External Examiner Date: May 22, 2020

A1111

Signature of Thesis Supervisor Date: May 22, 2020

Bhum 22/05/2020

Signature of PSPC Member #2 Date: May 22, 2020

Signature of Convener, DPGC Date: May 22, 2020

#### ACKNOWLEDGEMENTS

Foremost, I would like to express my sincere gratitude to my Ph.D. thesis supervisor, Prof. Abhinav Kranti, for providing me an opportunity to join his research group at IIT Indore. I am deeply grateful for his guidance, motivation, positive criticism, and feedback towards my Ph.D. work. His support and effort have made me accomplish the research objectives in this thesis.

I sincerely thank my PSPC members, Dr. Prabhat Kumar Upadhyay, and Dr. Bhupesh Kumar Lad, for their insightful remarks on the Ph.D. work from various perspectives.

I gratefully acknowledge IIT Indore for providing me the necessary infrastructures and research facilities. I am thankful to all the faculty members of the Discipline of Electrical Engineering for their kind support during my Ph.D. work. I greatly appreciate all the staff members of IIT Indore for their generous help concerning academics and accommodations.

I express my sincere gratitude to the Ministry of Electronics and Information Technology (MeitY), Government of India, for providing fellowship grant under Visvesvaraya Ph.D. scheme for Electronics and IT. This thesis is an outcome of the research and development work undertaken in the project under the Visvesvaraya Ph.D. scheme of MeitY, being implemented by Digital India Corporation. I would also like to acknowledge Council of Scientific and Industrial Research (CSIR) for providing the international travel grant to present my research paper.

I am deeply grateful to my colleagues Bhuvaneshwari, Manish and Nupur for their kind support and motivation during the research work. I would also like to extend my gratitude towards other colleagues Praveen, Hasan, Sandeep, Mukta, Saurabh, Pranjal, Siddharth, Khushboo and Pranay for their kind co-operation and healthy working environment in the research lab.

I would like to express my heartfelt gratitude to my friend Abhishek for motivating me to pursue my career in research. A special thanks to my friend Lichchhavi for her homely care and pleasant stay at IIT Indore. I cannot forget to thank my other friends Shweta, Krishnendu, Pooja, Kalyani, Sujata, Komal, Anjali, Anubha, Nishant, Uday and Biswajit for their friendship and co-operation at IIT Indore.

I would like to express my deepest gratitude to my family members: my father Mr. Vinod Jaiswal, mother Mrs. Sandhya Jaiswal, younger sister Ritika and younger brother Vibhor, for their unconditional love, encouragement and support during the Ph.D. work. I am also heartily

grateful to my cousins Niharika and Abhijeet for their timely help and care during paper presentations related to the Ph.D. work.

At last, I am wholeheartedly grateful to Almighty God for giving me skills, strength and faith for this crucial phase of my life.

Nivedita Jaiswal

Dedicated to my family

#### **ABSTRACT OF THE DISSERTATION**

### Design Optimization of Double Gate Junctionless MOSFET for Enhanced Short Channel Immunity

The semiconductor industry has continuously been involved in the development and production of digital Integrated Circuits (ICs) for High Performance (HP) and Low Power (LP)/Ultra Low Power (ULP) logic applications. Due to the very different nature of constraints, LP compatible devices widely differ from the HP transistor architectures. The prime goal of LP technology is to trade-off speed performance for low standby power or low off-current ( $I_{OFF}$ ). A scaled-down transistor possessing ideal subthreshold swing (S) and a low value of Drain Induced Barrier Lowering (DIBL) is desirable for LP technology. However, due to the downscaling of the gate length  $(L_g)$ , the undesirable Short-Channel Effects (SCEs) are observed in the characteristics of Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET). SCEs cause a reduction in threshold voltage ( $V_{\rm th}$ ) with decreasing  $L_{\rm g}$  (i.e. threshold voltage roll-off,  $dV_{\rm th}$ ) and increasing  $V_{\rm ds}$ (i.e. DIBL), as well as degradation in S. A feasible solution to alleviate SCEs is to enhance electrostatic control over the channel region through multiple gates in a transistor. Multi-gate Junctionless (JL) transistors can be potential alternatives to conventional MOSFET for downscaling owing to the absence of traditional pn junctions, relaxed fabrication processes and thermal budgets, efficient control over the channel by multiple gates, and enhanced immunity towards SCEs. Literature has shown the potential of heavily doped (10<sup>19</sup> cm<sup>-3</sup>) JL MOSFET over conventional MOSFET for LP logic technology than for HP logic technology applications. A moderately doped JL MOSFET ( $10^{18}$  cm<sup>-3</sup> to  $5 \times 10^{18}$  cm<sup>-3</sup>) can further improve LP performance, reduce parameter variability and relax gate workfunction requirement. Dedicated optimizations of underlap regions and sidewall spacers in JL FETs are essential for LP technologies. Recently, JL MOSFET with innovative Shell Doping Profile (SDP) has experimentally demonstrated improved S, higher  $I_{ON}/I_{OFF}$  ratio, and lower parameter sensitivity than uniformly doped JL transistors, thus indicating favorable prospects for downscaling and LP technology.

In conventional JL transistors, due to the identical dopant type (preferably high doping) throughout the semiconductor film, the extension of depletion regions outside the gated portion can take place in the off-state. Consequently, effective channel length ( $L_{eff}$ ) becomes longer than  $L_g$ . An elongated  $L_{eff}$  in the subthreshold operating regime can suppress SCEs in these transistors and has the potential for LP technology while enabling downscaling. This unique and inherent property of JL transistors exists in mostly all JL architectures, whether traditional structures [11],

modified structures with Gate-Source/Drain (G-S/D) underlap, or novel JL FET with SDP. However, the value of  $L_{eff}$  in the subthreshold regime varies in different topologies. The thesis provides comprehensive and dedicated approaches to estimate as well as suppress SCEs in various Double Gate (DG) JL architectures (DG JL with G-S/D underlap and SDP), by adequately capturing  $L_{eff}$  in the subthreshold regime. The thesis also identifies critical design parameters that can be optimized for superior short channel performance, thereby providing optimally designed DG JL transistor for LP subthreshold logic applications.

A five-region semi-analytical model for subthreshold channel potential is developed to adequately capture  $L_{\text{eff}}$  for symmetric mode-operated DG JL MOSFET at any gate-underlap length. The five-region model can be adapted into three or four regions depending upon the lateral extent of depletion into the G-S/D underlap. The transfer characteristics obtained from approximate analytical solutions for subthreshold drain current ( $I_{ds}$ ) are utilized to extract the parameters indicating SCEs ( $dV_{th}$ , DIBL and S). The developed model results reasonably agree with simulation data. The thesis presents that channel doping and underlap length are two critical parameters that affect SCEs. An optimally long underlap along with moderate doping ( $10^{18}$  cm<sup>-3</sup>) can be used as an advantage to improve SCEs at sub-50 nm gate lengths.

The thesis develops a semi-analytical model to estimate SCEs for independent gate-operated asymmetric DG structure with G-S/D underlap. The model considers non-identical values for front and back gate workfunctions and oxide thicknesses, and S/D underlap lengths. The modeled  $I_{ds}$ ,  $V_{th}$ , and S adequately agree with the simulation data. The thesis highlights the role of back gate bias ( $V_{bg}$ ), channel doping ( $N_d$ ) and underlap length ( $L_{un}$ ) to improve the device performance through optimization of off-current ( $I_{OFF}$ ),  $V_{th}$  and S. Results propose an optimum choice of negative  $V_{bg}$  together with moderate  $N_d$  and sufficiently long  $L_{un}$  for short channel asymmetric DG JL device. The generalized model formalism in the subthreshold regime can be utilized to optimize the self-aligned DG JL device for LP subthreshold logic applications.

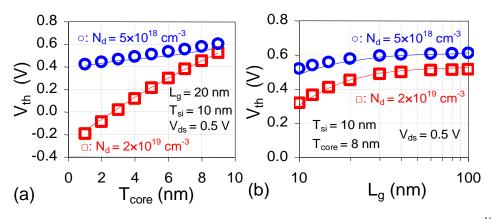

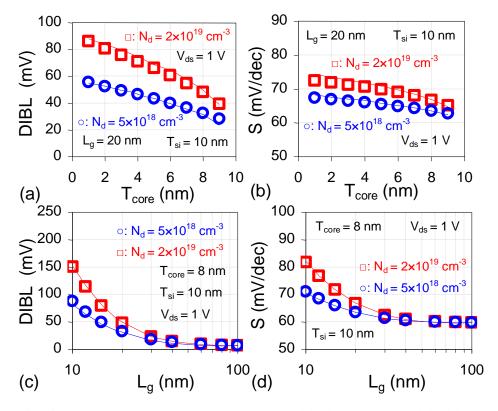

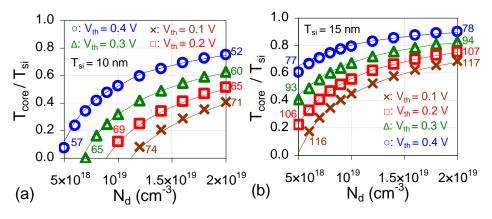

The thesis also presents a semi-analytical model for estimating  $L_{eff}$ -dependent SCEs in DG JL MOSFET with SDP (referred to as Core-Shell (CS) DG JL MOSFET). The developed model reasonably captures the channel potential and SCEs in CS DG JL MOSFETs for varying  $L_g$ , core thickness ( $T_{core}$ ), shell doping ( $N_d$ ) and biases. The modeled  $V_{th}$ , DIBL and S, derived from the transfer characteristics, are in good agreement with the simulation results. The thesis investigates the impact of  $N_d$  and  $T_{core}$  on the short channel performance of the CS DG JL MOSFET. Results suggest that the moderate  $N_d$  – narrow  $T_{core}$  pair can be preferred over high  $N_d$  – wide  $T_{core}$  for similar SCEs but at reduced  $V_{th}$  sensitivity.

### LIST OF PUBLICATIONS

#### A. <u>Peer-reviewed Journals:</u>

- Nivedita Jaiswal and Abhinav Kranti, "A Model for Gate-Underlap Dependent Short Channel Effects in Junctionless Transistor," IEEE Transaction on Electron Devices, vol. 65, no. 3, pp. 881-887, Mar. 2018.

- Nivedita Jaiswal and Abhinav Kranti, "Modeling Short-Channel Effects in Asymmetric Junctionless MOSFETs With Underlap," IEEE Transactions on Electron Devices, vol. 65, no. 9, pp. 3669-3675, Sep. 2018.

- Nivedita Jaiswal and Abhinav Kranti, "Modeling Short-Channel Effects in Core-Shell Junctionless MOSFET," IEEE Transactions on Electron Devices, vol. 66, no. 1, pp. 292-299, Jan. 2019.

#### **B. Proceedings in International Conferences:**

- Nivedita Jaiswal and Abhinav Kranti, "Influence of Gate-Source/Drain Underlap on Performance of Junctionless Transistor," In Abstract of 6<sup>th</sup> International Symposium on Integrated Functionalities (ISIF 2017), New Delhi, India, Dec. 2017, p. 126.

- Nivedita Jaiswal and Abhinav Kranti, "Scalability and V<sub>th</sub> Sensitivity Assessment of Core-Shell Junctionless MOSFET," In Extended Abstract of International Conference on Solid State Devices and Materials (SSDM 2019), Nagoya, Japan, Sep. 2019, pp. 653-654.

### **TABLE OF CONTENTS**

| TITLE PAGE           | Ι    |

|----------------------|------|

| DECLARATION PAGE     | II   |

| ACKNOWLEDGEMENT      | III  |

| DEDICATION PAGE      | V    |

| ABSTRACT             | VI   |

| LIST OF PUBLICATIONS | VIII |

| TABLE OF CONTENTS    | IX   |

| LIST OF FIGURES      | XIII |

| LIST OF TABLES       | XIX  |

| NOMENCLATURE         | XX   |

| ACRONYMS             | XXV  |

| Chap | oter 1: In | troduction                                                | 1  |

|------|------------|-----------------------------------------------------------|----|

| 1.1  | Motiva     | ation                                                     | 1  |

|      | 1.1.1      | More Moore                                                | 1  |

|      | 1.1.2      | Low Power Logic Technology                                | 3  |

| 1.2  | Basic I    | Background                                                | 4  |

|      | 1.2.1      | Short Channel Effects                                     | 4  |

|      | 1.2.2      | Junctionless Transistor                                   | 7  |

|      | 1.2.3      | Numerical Simulation using TCAD Tools                     | 12 |

|      | 1.2.4      | Semiconductor Device Modeling                             | 13 |

| 1.3  | Review     | v of the Past Work                                        | 15 |

|      | 1.3.1      | Optimization of Undoped Nanoscale FinFETs utilizing Gate- | 15 |

|      |            | Source/Drain Underlap                                     |    |

|      | 1.3.2      | Feasibility of JL Transistors for LP Logic Applications   | 16 |

|      | 1.3.3      | Analytical Modeling of JL Transistors                     | 17 |

| 1.4  | Resear     | ch Problem and Objectives                                 | 21 |

|      | 1.4.1      | Problem Formulation                                       | 21 |

|      | 1.4.2      | Thesis Objectives                                         | 24 |

| 1.5  | Organi     | zation of the Thesis                                      | 24 |

| Chap | oter 2: N  | Modeling the Dependence of Short Channel Effects on Gate- | 27 |

| Sour | ce/Drain   | Underlap Regions in Junctionless Transistor               |    |

| 2.1  | Introdu    | action                                                    | 27 |

| 2.2  | Model      | Development                                               | 29 |

|      | 2.2.1      | Gated Portion (Region-I)                                  | 29 |

|      | 2.2.2      | Depleted Portion of S/D Underlap Region (Region II/III)   | 31 |

|      | 2.2.3      | Non-depleted Portion of Underlap Region (Region IV/V)     | 32 |

|      | 2.2.4      | Boundary and Continuity Conditions                        | 33 |

| 2.3  | Estima     | tion of Gate-Underlap Dependent Device Characteristics    | 35 |

|      | 2.3.1      | Electrostatic Channel Potential Distribution              | 35 |

|      | 2.3.2      | Peculiar Cases and Modifications                          | 36 |

|      | 2.3.3      | Subthreshold Drain Current                                | 37 |

|      | 2.3.4      | Estimation of Short Channel Effects                       | 38 |

| 2.4  | Results    | s and Model Verification                                  | 39 |

|      | 2.4.1      | Simulation Details                                        | 40 |

|       | 2.4.2    | Preliminary Model Verification                               | 40 |

|-------|----------|--------------------------------------------------------------|----|

|       | 2.4.3    | Short Channel Effects                                        | 42 |

| 2.5   | Conclus  | sion                                                         | 46 |

| Chap  | ter 3: A | Generic Model to Optimize Short Channel Self-Aligned         | 47 |

| Asym  | metric D | ouble Gate Junctionless Transistor with Gate-Underlap        |    |

| 3.1   | Introduc | ction                                                        | 47 |

| 3.2   | Model I  | Derivation Considering Bias and Structural Asymmetries       | 49 |

|       | 3.2.1    | Gated Portion (Region-I)                                     | 49 |

|       | 3.2.2    | Depleted Portions of G-S/D Underlap (Region II/III)          | 51 |

|       | 3.2.3    | Non-Depleted Portions of G-S/D Underlap (Region IV/V)        | 51 |

|       | 3.2.4    | Channel Potential Distribution                               | 52 |

|       | 3.2.5    | Position of Subthreshold Conduction                          | 53 |

|       | 3.2.6    | Exceptional Cases and Modifications                          | 53 |

|       | 3.2.7    | Subthreshold Drain Current                                   | 54 |

| 3.3   | Results  | and Model Validation                                         | 55 |

|       | 3.3.1    | Electrostatic Potential Profiles under Asymmetries           | 55 |

|       | 3.3.1    | Short Channel Effects                                        | 58 |

|       | 3.3.2    | Dynamic Aspect of Threshold Voltage                          | 60 |

| 3.4   | Conclus  | sion                                                         | 62 |

| Chap  | ter 4: M | odeling-based Optimization of Short Channel Effects in Core- | 63 |

| Shell | Junction | less MOSFET                                                  |    |

| 4.1   | Introduc | ction                                                        | 63 |

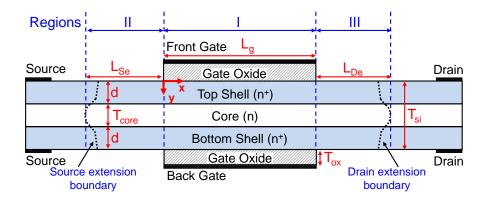

| 4.2   | Region-  | wise Modeling Assumptions                                    | 64 |

| 4.3   | Model I  | Derivation                                                   | 65 |

|       | 4.3.1    | Parabolic Potential Approximation                            | 66 |

|       | 4.3.2    | Gated Portion (Region-I)                                     | 67 |

|       | 4.3.3    | Source and Drain Extension Portions (Region II and III)      | 68 |

|       | 4.3.4    | Complete Solution for Central Channel Potential              | 70 |

|       | 4.3.5    | Electron Concentration                                       | 71 |

|       | 4.3.6    | Subthreshold Drain Current                                   | 71 |

| 4.4   | Results  | and Model Validation                                         | 72 |

|       | 4.4.1    | Preliminary Model Validation                                 | 72 |

|       | 4.4.2    | Short Channel Effects                                        | 76 |

|      | 4.4.3     | Design Guidelines                                         | 77 |

|------|-----------|-----------------------------------------------------------|----|

| 4.5  | Conclus   | ion                                                       | 78 |

| Chap | ter 5: Co | nclusion and Future Work                                  | 79 |

| 5.1  | Conclus   | ion                                                       | 79 |

| 5.2  | Scope for | or Future Work                                            | 84 |

|      | 5.2.1     | Incorporation of QCE in Core-Shell JL MOSFETs             | 84 |

|      | 5.2.2     | Modeling SCEs in Core-Shell JL Transistors including Non- | 85 |

|      |           | abrupt Doping Gradient                                    |    |

|      | 5.2.3     | Process-induced Variability Analysis in the Subthreshold  | 85 |

|      |           | Characteristics of JL MOSFETs                             |    |

| APPE | NDIX-A    |                                                           | 87 |

| A.1  | Approxi   | mating Numerical Integrals                                | 87 |

| A.2  | Effectiv  | e Built-in Voltage                                        | 87 |

|      | A.2.1     | Determination of Effective Built-in Voltage               | 87 |

|      | A.2.2     | Model Validation for Effective Built-in Voltage           | 90 |

| REFE | RENCE     | S                                                         | 91 |

### LIST OF FIGURES

| Figure No. | Figure Title                                                                 | Page No. |

|------------|------------------------------------------------------------------------------|----------|

| Fig. 1.1   | (a) Intel transistor chronological innovations over six                      | 2        |

|            | generations facilitating Moore's scaling [15]-[16]. (b) Scaling              |          |

|            | trends for Intel logic technologies showing High Volume                      |          |

|            | Manufacturing (HMV) wafer start date-wise improvement in                     |          |

|            | logic transistor density (MTr/mm <sup>2</sup> ) [16] and relative logic area |          |

|            | [15]. Data source: Intel (Bohr and Young, 2017 [15], and Bohr,               |          |

|            | 2018 [16]).                                                                  |          |

| Fig. 1.2   | Typical attributes of 22nm non-planar tri-gate transistor                    | 3        |

|            | optimized for various logic technologies: (a) NMOS and PMOS                  |          |

|            | off-current ( $I_{OFF}$ ) (b) NMOS on-current ( $I_{ON}$ ), and (c) PMOS     |          |

|            | on-current (I <sub>ON</sub> ). Data source: Intel (Jan et al., 2012 [17]).   |          |

| Fig. 1.3   | (a) Simplified schematic diagram of <i>n</i> -channel Single Gate            | 4        |

|            | (SG) Silicon-on-Insulator (SOI) MOSFET [21], [23], [24].                     |          |

|            | Illustration of short channel effects using two-dimensional                  |          |

|            | potential contours in the channel region for (b) long channel ( $L_{\rm g}$  |          |

|            | = 500 nm) and (c) short channel ( $L_g = 50$ nm) devices. In Fig.            |          |

|            | 1.3(b),(c), each color corresponds to a certain potential range,             |          |

|            | as indicated by above color codes. The simulations have been                 |          |

|            | carried out through Atlas TCAD tool [25].                                    |          |

| Fig. 1.4   | Variations of Conduction Band (CB) energy along the lateral                  | 5        |

|            | (x-) direction with drain bias for (a) long channel and (b) short            |          |

|            | channel MOSFETs. Comparison of transfer $(I_{ds}-V_{gs})$                    |          |

|            | characteristics: (c) long channel $(L_{g,L})$ versus short channel           |          |

|            | $(L_{g,S})$ cases and (d) low drain bias $(V_{ds1})$ versus high drain bias  |          |

|            | $(V_{\rm ds2})$ cases.                                                       |          |

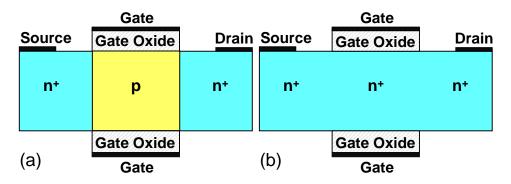

| Fig. 1.5   | Schematic diagram showing longitudinal cross-sectional view                  | 8        |

|            | of (a) conventional inversion mode $(n^+-p-n^+)$ MOSFET [21] and             |          |

|            | (b) junctionless $(n^+-n^+-n^+)$ transistors [31], elucidating               |          |

|            | difference in doping profile across the semiconductor film.                  |          |

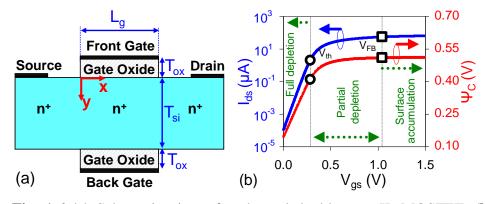

Fig. 1.6 (a) Schematic view of *n*-channel double gate JL MOSFET. (b) Typical variations of drain current (I<sub>ds</sub>) and central potential (ψ<sub>C</sub>) extracted at x = L<sub>g</sub>/2, y = T<sub>si</sub>/2 with gate bias at V<sub>ds</sub> = 50 mV, marked with threshold (symbol: ○) and flatband (symbol: □) voltages. Device parameters: L<sub>g</sub> = 50 nm, T<sub>ox</sub> = 2 nm, T<sub>si</sub> = 10 nm, N<sub>d</sub> (n<sup>+</sup>) = 10<sup>19</sup> cm<sup>-3</sup> and p+ polysilicon gate.

8

9

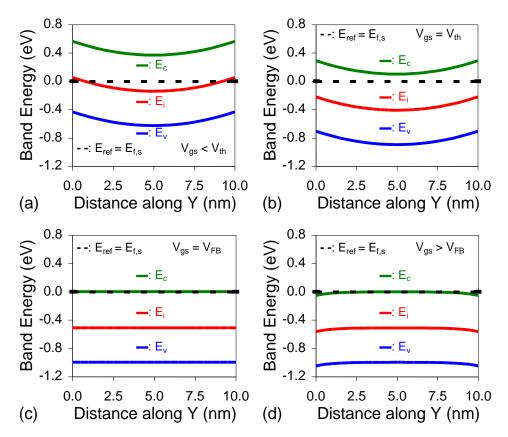

- **Fig. 1.7** Energy band diagrams extracted along the semiconductor film at mid-gate position ( $x = L_g/2$ ), illustrating typical conduction mechanism in an *n*-channel DG JL MOSFET for (a)  $V_{gs} = 0$  V ( $< V_{th}$ ), (b)  $V_{gs} = 0.285$  V ( $= V_{th}$ ), (c)  $V_{gs} = 1.04$  V ( $= V_{FB}$ ) and (d)  $V_{gs} = 1.5$  V ( $> V_{FB}$ ). Device parameters are the same, as mentioned in Fig. 1.6.

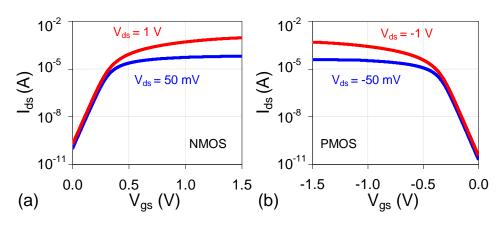

- Fig. 1.8 Transfer characteristics of (a) NMOS and (b) PMOS DG JL 10 transistors for  $V_{ds}$  of 50 mV and 1 V. Device specification:  $L_g =$ 50 nm,  $T_{ox} = 2$  nm,  $T_{si} = 10$  nm,  $T_{ox} = 2$  nm,  $N_d (n^+) = 10^{19}$  cm<sup>-3</sup>,  $N_a (p^+) = 10^{19}$  cm<sup>-3</sup>, and  $p^+ (n^+)$  polysilicon gates for NMOS (PMOS).

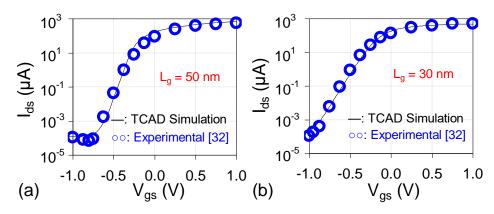

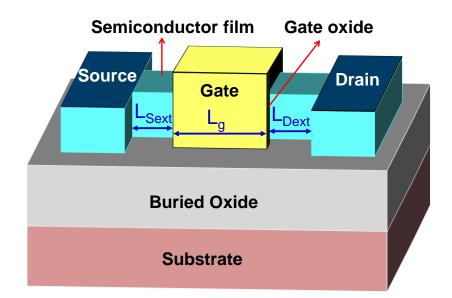

- Fig. 1.9 Comparison of transfer characteristics obtained from simulation 12 against published experimental data [32] for gate lengths of (a)  $L_{\rm g} = 50$  nm, and (b)  $L_{\rm g} = 30$  nm. Symbols indicate experimental data and solid lines show the numerical simulation data.

- Fig. 1.10 Three-dimensional (3D) schematic representation of undoped 15

IM SOI FinFET indicating the source and drain underlap of lengths, *L*<sub>Sext</sub> and *L*<sub>Dext</sub>, respectively [77], [78].

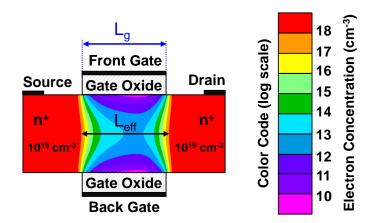

- **Fig. 1.11** 2D contour of electron concentration elucidating longer  $L_{eff}$  21 than  $L_g$  in JL MOSFET under off-state ( $V_{gs} = 0$  V) [123]. Device specifications are identical to those mentioned in Fig. 1.6. The numbers written for each color code boundary corresponds to the powers of 10.

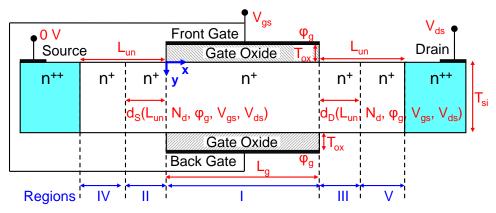

- **Fig. 2.1** Schematic view of *n*-channel DG JL transistor displaying I-V 28 regions examined for the model development under symmetric mode operation, i.e. same values of G-S/D underlap lengths  $(L_{un})$ , gate biases  $(V_{gs})$ , gate workfunctions  $(\varphi_g)$ , and gate oxide thicknesses  $(T_{ox})$ .

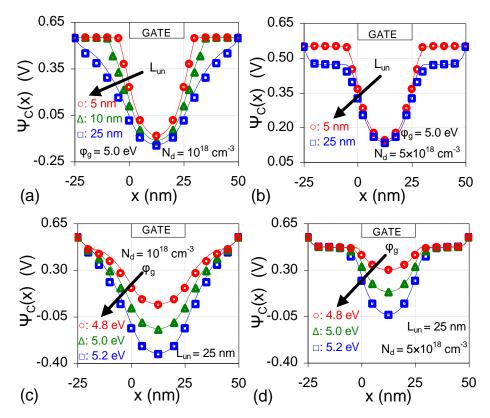

**Fig. 2.2** Variation in central potential along the *x*-direction for varying  $L_{un}$  and  $\varphi_g$  with  $L_g = 25$  nm,  $V_{gs} = V_{ds} = 0$  V, and (a), (c)  $N_d = 10^{18}$  cm<sup>-3</sup> and (b), (d)  $N_d = 5 \times 10^{18}$  cm<sup>-3</sup>. Solid lines represent developed model and symbols denote TCAD simulation data.

39

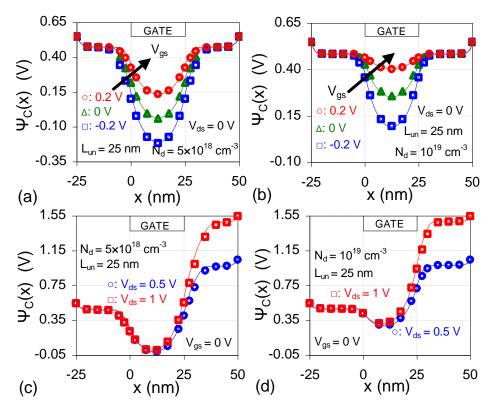

- **Fig. 2.3** Dependence of  $\psi_{\rm C}(x)$  along the *x*-direction on varying  $V_{\rm gs}$  and 40  $V_{\rm ds}$  at  $L_{\rm g} = 25$  nm,  $\varphi_{\rm g} = 5.2$  eV and (a), (c)  $N_{\rm d} = 5 \times 10^{18}$  cm<sup>-3</sup> and (b), (d)  $N_{\rm d} = 10^{19}$  cm<sup>-3</sup>. Lines denote model results and symbols show simulation data.

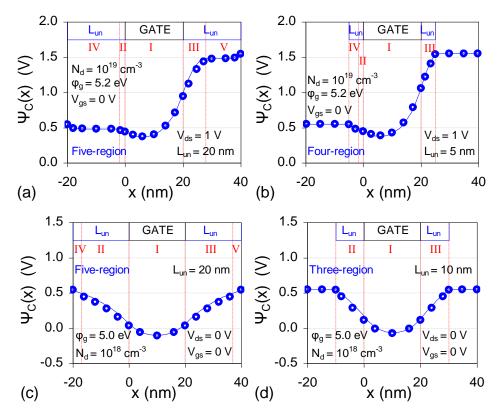

- **Fig. 2.4** Plots of  $\psi_{C}(x)$  illustrating possible peculiar cases captured by 41 the developed model at  $L_{g} = 20$  nm and  $V_{gs} = 0$  V for different  $(N_{d}, L_{un}, V_{ds})$  combinations: (a)  $(10^{19} \text{ cm}^{-3}, 20 \text{ nm}, 1 \text{ V})$ , (b)  $(10^{19} \text{ cm}^{-3}, 5 \text{ nm}, 1 \text{ V})$ , (c)  $(10^{18} \text{ cm}^{-3}, 20 \text{ nm}, 0 \text{ V})$ , and (d)  $(10^{18} \text{ cm}^{-3}, 10 \text{ nm}, 0 \text{ V})$ . Lines denote model results and symbols show simulation data.

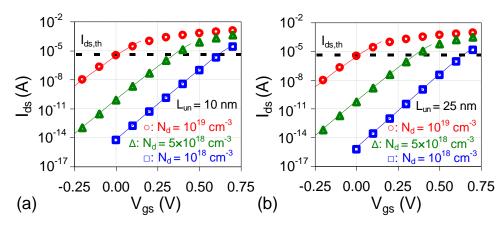

- **Fig. 2.5**  $I_{ds}-V_{gs}$  characteristics for three  $N_d$  values with (a)  $L_{un} = 10$  nm 42 and (b)  $L_{un} = 25$  nm. Other parameters:  $L_g = 25$  nm,  $V_{ds} = 1$  V and  $\varphi_g = 5.1$  eV. Lines denote model results and symbols show simulation data.

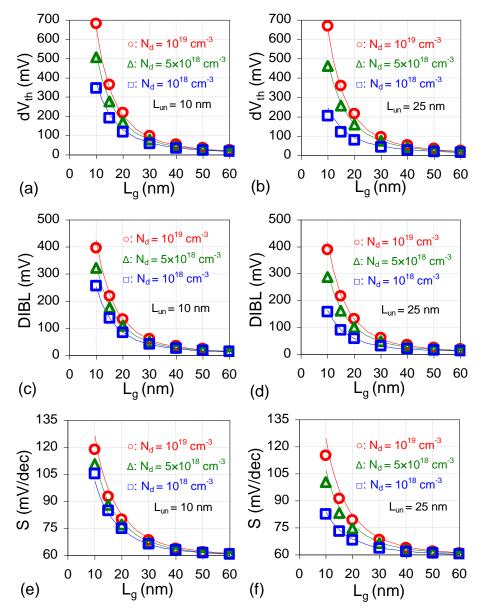

- **Fig. 2.6** Variation of SCEs with  $L_g$  for  $\varphi_g = 5.1$  eV at  $V_{ds} = 1$  V: (a)  $dV_{th}$ , 43 (c) DIBL and (e) S for  $L_{un} = 10$  nm, and (b)  $dV_{th}$ , (d) DIBL and (f) S for  $L_{un} = 25$  nm. Lines denote model results and symbols show simulation data.

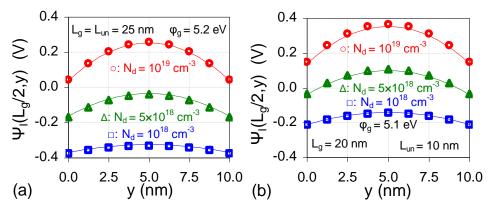

- Fig. 2.7 Channel potential along the y-direction at mid-gate position 44 elucidating doping-dependent channel spreading at  $V_{gs} = V_{ds} =$  0V for (a)  $L_g = L_{un} = 25$  nm, and (b)  $L_g = 20$  nm and  $L_{un} = 10$  nm. Lines show model results and symbols denote simulation data.

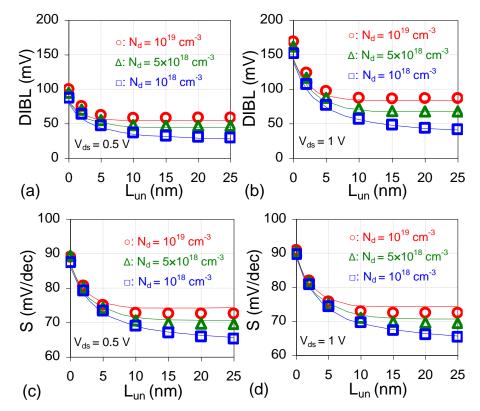

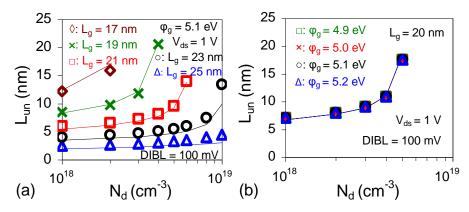

- **Fig. 2.8** Underlap-dependent short channel behavior for  $L_g = 25$  nm and 45  $\varphi_g = 5.1$  eV: (a) DIBL and (b) *S* at  $V_{ds} = 0.5$  V, and (c) DIBL and (d) *S* at  $V_{ds} = 1$  V. Lines denote model results and symbols show simulation data.

- Fig. 2.9Plot depicting the minimum values of  $L_{un}$  required for attaining45DIBL = 100 mV at  $V_{ds} = 1$  V as a function of  $N_d$  for various (a) $L_g$  and (b)  $\varphi_g$ . Lines show model results and symbols denote

XV

simulation data.

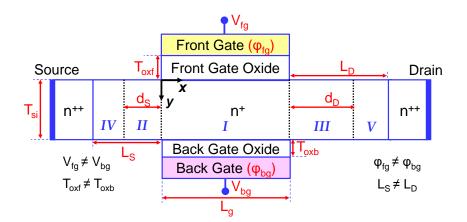

- Fig. 3.1 Schematic view of a self-aligned *n*-channel DG JL transistor 48 displaying I-V regions examined for the model derivation under asymmetric mode operation, i.e. different values of G-S/D underlap lengths ( $L_S \neq L_D$ ), and front and back gate biases ( $V_{fg} \neq$  $V_{\rm bg}$ ), oxide thicknesses ( $T_{\rm oxf} \neq T_{\rm oxb}$ ) and workfunctions ( $\varphi_{\rm fg} \neq$  $\varphi_{\rm bg}$ ).

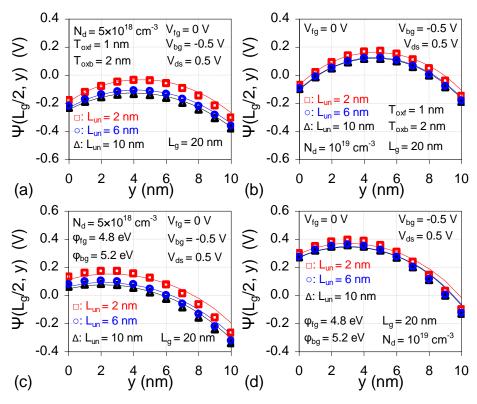

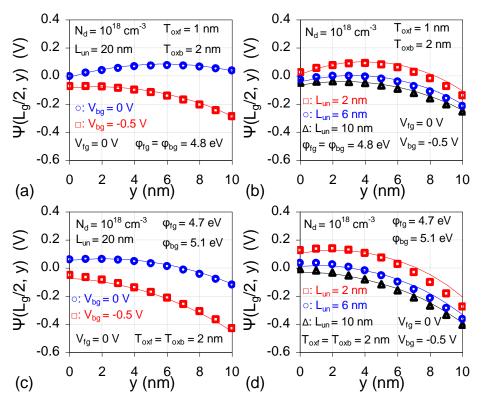

- **Fig. 3.2** Variation of electrostatic potential along the y-direction at x =55  $L_g/2$  with identical S/D underlap length  $L_{un}$  (=  $L_S = L_D$ ) for (a), (b)  $T_{\text{oxf}} \neq T_{\text{oxb}}$  and  $\varphi_{\text{g}} (= \varphi_{\text{fg}} = \varphi_{\text{bg}}) = 5.1 \text{ eV}$ , and (c), (d)  $\varphi_{\text{fg}} \neq \varphi$ bg and  $T_{\text{ox}}$  (=  $T_{\text{oxf}} = T_{\text{oxb}}$ ) = 2 nm. In figure parts (a), (c)  $N_{\text{d}}$  =  $5 \times 10^{18}$  cm<sup>-3</sup> and (b), (d)  $N_{\rm d} = 10^{19}$  cm<sup>-3</sup>. Lines show model results and symbols denote simulation data.

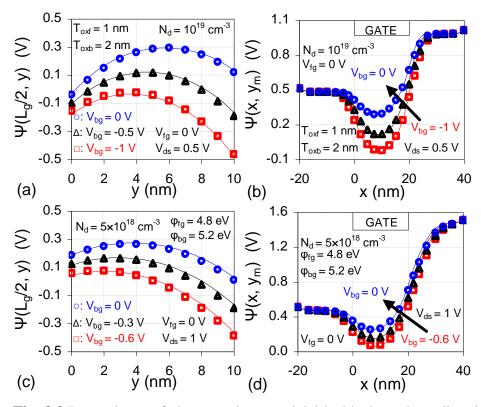

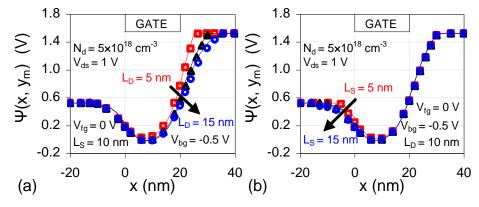

- Fig. 3.3 Dependence of electrostatic potential (a), (c) along the y-56 direction at  $x = L_g/2$ , and (b), (d) along the x-direction at  $y = y_m$ on  $V_{\text{bg}}$  for (a), (b)  $N_{\text{d}} = 10^{19} \text{ cm}^{-3}$ ,  $T_{\text{oxf}} \neq T_{\text{oxb}}$  and  $\varphi_{\text{g}} = 5.1 \text{ eV}$ , and (c), (d)  $N_d = 5 \times 10^{18} \text{ cm}^{-3}$ ,  $\varphi_{fg} \neq \varphi_{bg}$  and  $T_{ox} = 2 \text{ nm}$ . Other parameters:  $L_{\rm g} = L_{\rm un} = 20$  nm and  $T_{\rm si} = 10$  nm. Lines show model results and symbols denote simulation data.

- Fig. 3.4 Dependence of electrostatic potential along the y-direction at x57  $= L_{\rm g}/2$  on (a), (c),  $V_{\rm bg}$  and varying and (b), (d)  $L_{\rm un}$  for  $N_{\rm d} = 10^{18}$ cm<sup>-3</sup> (a), (b),  $T_{\text{oxf}} \neq T_{\text{oxb}}$  and  $\varphi_{\text{g}} = 4.8$  eV, and (c), (d)  $\varphi_{\text{fg}} \neq \varphi_{\text{bg}}$ and  $T_{ox} = 2$  nm. Other parameters:  $L_g = 20$  nm and  $T_{si} = 10$  nm. Lines show model results and symbols denote simulation data.

- Fig. 3.5 Variation of electrostatic potential along the y-direction at x =58  $L_g/2$  with (a) varying  $L_D$  but fixed  $L_S$ , and (b) varying  $L_S$  but fixed L<sub>D</sub>. Other parameters:  $L_g = 20$  nm,  $T_{ox} = 2$  nm and  $\varphi_g = 5.1$ eV. Lines indicate model results and symbols represent simulation data.

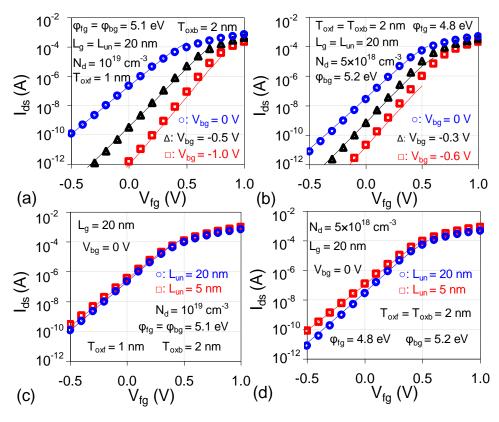

- Fig. 3.6 Subthreshold drain current versus front gate bias characteristics at  $V_{ds} = 1$  V for varying (a), (b)  $V_{bg}$  and (c), (d)  $L_{un}$  values. In figure parts (a), (c)  $T_{\text{oxf}} \neq T_{\text{oxb}}$  and  $N_{\text{d}} = 10^{19} \text{ cm}^{-3}$ , and (b), (d)  $\varphi$ - $_{fg} \neq \varphi_{bg}$  and  $N_d = 5 \times 10^{18}$  cm<sup>-3</sup>. Lines indicate model results and symbols represent simulation data.

XVI

58

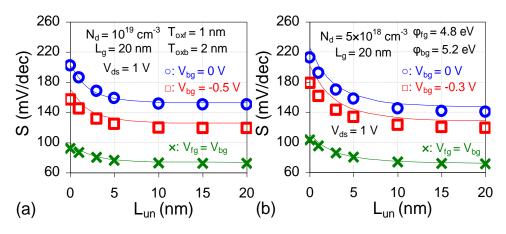

- **Fig. 3.7** Comparison of subthreshold swings for independently driven  $(V_{bg} \text{ have fixed bias value})$  and simultaneously driven  $(V_{fg} = V_{bg})$  gate operation, and for different  $L_{un}$  under gate asymmetries: (a)  $T_{oxf} \neq T_{oxb}$  and  $\varphi_g = 5.1$  eV, and (b)  $\varphi_{fg} \neq \varphi_{bg}$  and  $T_{ox} = 2$  nm. Lines indicate model results and symbols represent simulation data.

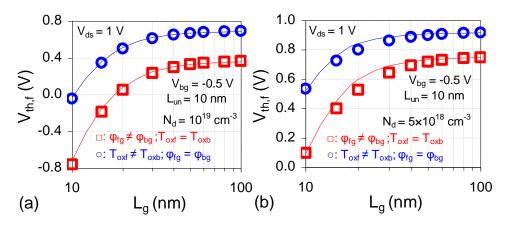

- Fig. 3.8 Plot of front gate threshold voltage as a function of  $L_g$  for (a)  $N_d$  59 = 10<sup>19</sup> cm<sup>-3</sup> and (b)  $N_d = 5 \times 10^{18}$  cm<sup>-3</sup> with gate asymmetries. Lines denote model results and symbols mark simulation data.

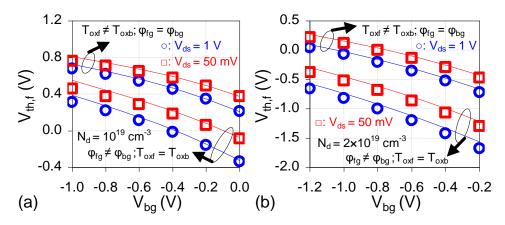

- Fig. 3.9 Plot of  $V_{\text{th,f}}$  versus  $V_{\text{bg}}$  at  $L_{\text{g}} = L_{\text{un}} = 20 \text{ nm}$ ,  $V_{\text{ds}} = 50 \text{ mV}$  and 1 60 V for (a)  $N_{\text{d}} = 10^{19} \text{ cm}^{-3}$  and (b)  $N_{\text{d}} = 2 \times 10^{19} \text{ cm}^{-3}$  with gate asymmetries. Lines denote model results and symbols indicate simulation data.

- **Fig. 3.10** Plot of  $V_{\text{th,f}}$  as a function of  $N_d$  at  $V_{ds} = 1$  V for  $L_{un} = 5$  nm and 61 20 nm, (a)  $T_{\text{oxf}} \neq T_{\text{oxb}}$ ,  $\varphi_g = 5.1$  eV and  $\varphi_g = 4.8$  eV, and (b)  $\varphi_{\text{fg}} \neq \varphi_{\text{bg}}$  and  $T_{\text{ox}} = 2$  nm. Lines denote model results and symbols indicate simulation data.

- **Fig. 4.1** Schematic view of *n*-channel CS DG JL MOSFET.

64

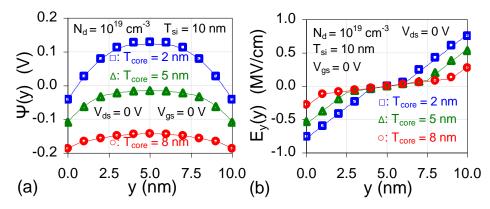

59

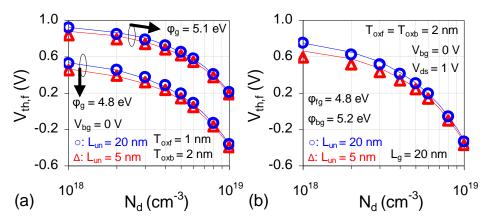

- **Fig. 4.2** Dependence of (a) potential and (b) vertical component of the 72 electric field  $(E_y)$  along the y-direction at  $x = L_g/2$  on varying  $T_{core}$  for  $L_g = 10$  nm. Symbols mark TCAD simulation data and lines denote model results.

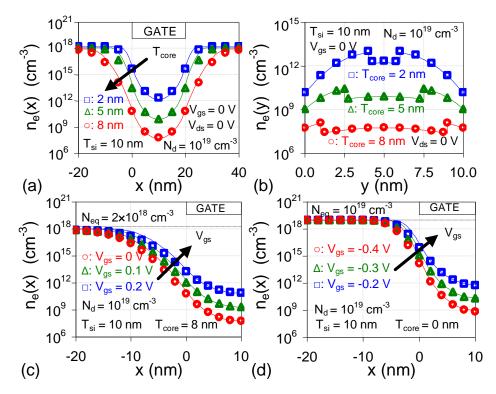

- **Fig. 4.3** Plot of electron concentration (a) along the *x*-direction at y = 73 $T_{si}/2$  and (b) along the *y*-direction at  $x = L_g/2$  for various  $T_{core}$ and  $L_g = 20$  nm. Enlarged view of part (a) illustrating  $n_e$  with varying  $V_{gs}$  for (c) CS ( $T_{core} = 8$  nm) and (d) conventional ( $T_{core}$ = 0 nm) DG JL topologies in the subthreshold region. Symbols depict simulation data and lines denote model results.

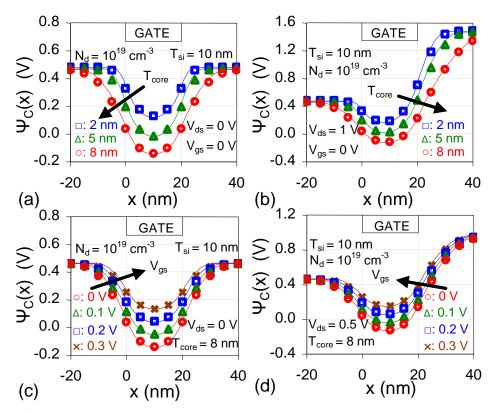

- **Fig. 4.4** Dependence of central potential along the *x*-direction at y = 74 $T_{si}/2$  and  $L_g = 20$  nm on (a), (b) various  $T_{core}$  for  $V_{gs} = V_{ds} = 0$  V, and (c), (d) different  $V_{gs}$  for  $T_{core} = 8$  nm. In figure part (b)  $V_{ds} = 1$  V and (d)  $V_{ds} = 0.5$  V. Symbols mark simulation data and lines denote model results.

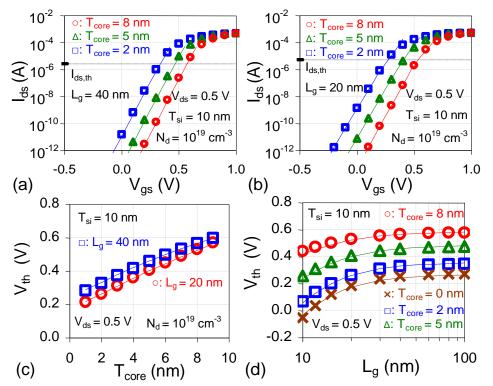

- **Fig. 4.5** Transfer characteristics at different  $T_{core}$  for (a)  $L_g = 40$  nm and 75

|          | (b) $L_g = 20$ nm. Plot of $V_{th}$ versus (c) $T_{core}$ and (d) $L_g$ . Symbols                                                          |    |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

|          | mark simulation data and lines denote model results.                                                                                       |    |

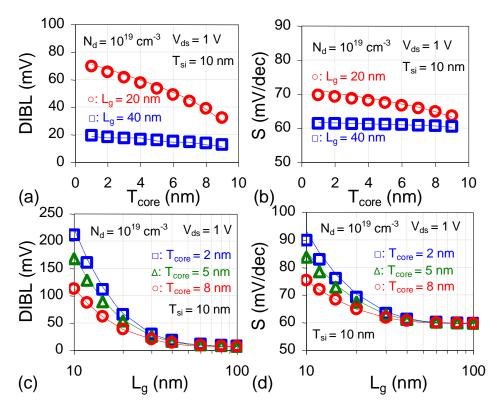

| Fig. 4.6 | Effect of $T_{core}$ and $L_g$ variations on (a), (c) DIBL and (b), (d) S.                                                                 | 75 |

|          | Symbols mark simulation data and lines denote model results.                                                                               |    |

| Fig. 4.7 | Variation of $V_{\text{th}}$ with varying (a) $T_{\text{core}}$ and (b) $L_{\text{g}}$ for $N_{\text{d}} = 5 \times 10^{18}$               | 76 |

|          | cm <sup>-3</sup> and $2 \times 10^{19}$ cm <sup>-3</sup> . Symbols mark simulation data and lines                                          |    |

|          | show model results.                                                                                                                        |    |

| Fig. 4.8 | Effect of $T_{core}$ and $L_g$ variations on (a), (c) DIBL and (b), (d) S                                                                  | 77 |

|          | for $N_{\rm d} = 5 \times 10^{18} \text{ cm}^{-3}$ and $2 \times 10^{19} \text{ cm}^{-3}$ . Symbols mark simulation                        |    |

|          | data and lines denote model results.                                                                                                       |    |

| Fig. 4.9 | Plot of $T_{\text{core}}/T_{\text{si}}$ versus $N_{\text{d}}$ for fixed values of $V_{\text{th}}$ at $V_{\text{ds}} = 1$ V, $L_{\text{g}}$ | 77 |

|          | = 20 nm, and (a) $T_{si}$ = 10 nm and (b) $T_{si}$ = 15 nm. Symbols mark                                                                   |    |

|          | simulation data and lines denote model results.                                                                                            |    |

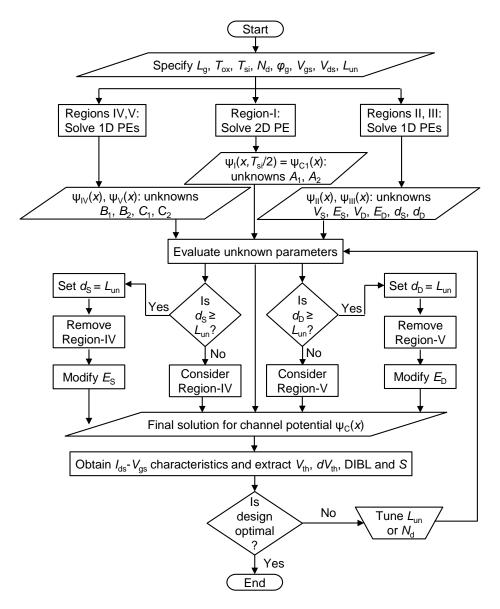

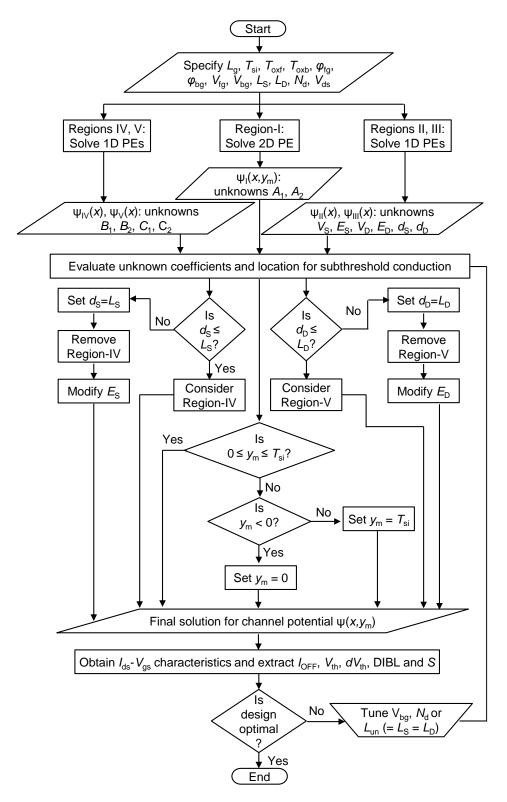

| Fig. 5.1 | Flowchart summarizing the modeling approach followed for the                                                                               | 80 |

|          | design optimization of DG JL under the symmetric mode                                                                                      |    |

|          | operation. The abbreviation PE(s) denotes Poisson's                                                                                        |    |

|          | equation(s).                                                                                                                               |    |

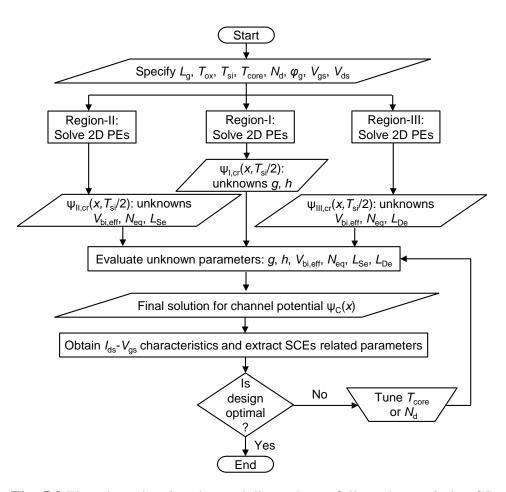

| Fig. 5.2 | Flowchart depicting generic model formulation for an optimally                                                                             | 82 |

|          | designed asymmetric DG JL MOSFET for LP logic application.                                                                                 |    |

|          | PE(s) indicates Poisson's equation(s).                                                                                                     |    |

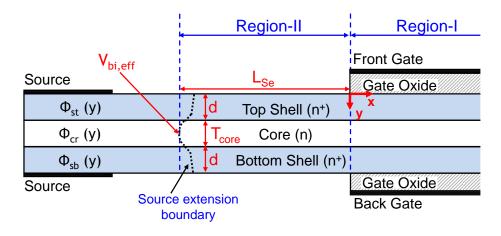

| Fig. 5.3 | Flowchart showing the modeling scheme followed to optimize                                                                                 | 83 |

|          | CS DG JL MOSFET with suppressed SCEs. PEs represents                                                                                       |    |

|          | Poisson's equations.                                                                                                                       |    |

| Fig. A.1 | Schematic illustration of effective built-in potential at the end                                                                          | 88 |

|          | of the source extension boundary of a CS DG JL MOSFET.                                                                                     |    |

|          | $V_{\rm bi,eff}$ on the drain side is identical to the source side on the drain                                                            |    |

|          | side (not shown in Fig. A.1).                                                                                                              |    |

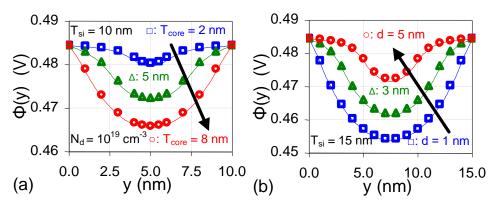

| Fig. A.2 | Dependence of electrostatic potential underneath S/D electrode                                                                             | 90 |

|          | (a) on different $T_{\text{core}}$ values for $T_{\text{si}} = 10$ nm, and (b) on varying $d$                                              |    |

|          | values for $T_{si} = 15$ nm with $N_d = 10^{19}$ cm <sup>-3</sup> . It is emphasized that                                                  |    |

|          | $d = (T_{\rm si} - T_{\rm core})/2$ . Symbols show simulations data and solid                                                              |    |

|          | lines represent model results.                                                                                                             |    |

|          |                                                                                                                                            |    |

### XVIII

# LIST OF TABLES

| Table No. | Table Title                                                  | Page No. |

|-----------|--------------------------------------------------------------|----------|

| Table 1.1 | Summary of few existing analytical models for JL transistors | 17-20    |

|           | available in the literature [86]-[122]                       |          |

| Table 1.2 | Key findings of some existing models for short-channel JL    | 22-23    |

|           | MOSFETs                                                      |          |

# NOMENCLATURE

| Symbols           | Description                                                           | Units    |

|-------------------|-----------------------------------------------------------------------|----------|

| a, b              | Arbitrary integration limits                                          | -        |

| $a_0, b_0, c_0,$  | Coefficients in parabolic potential approximation                     | V        |

| $a_1, b_1, c_1,$  | Coefficients in parabolic potential approximation                     | V/nm     |

| $a_1, b_1, c_1,$  | Coefficients in parabolic potential approximation                     | $V/nm^2$ |

| $A_1, A_2$        | Coefficients in generic solution for Region-I                         | V        |

| $B_1, B_2$        | Coefficients in generic solution for Region-IV                        | V        |

| $C_1, C_2$        | Coefficients in generic solution for Region-V                         | V        |

| $C_{ob}$          | Back gate oxide capacitance per unit area                             | $F/cm^2$ |

| $C_{of}$          | Front gate oxide capacitance per unit area                            | $F/cm^2$ |

| $C_{ox}$          | Gate oxide capacitance per unit area                                  | $F/cm^2$ |

| d                 | Shell depth (or) thickness of shell region                            | nm       |

| $D_1, D_2$        | Coefficients in generic solution for top shell potential along the y- | V        |

|                   | direction                                                             |          |

| $d_D$             | Lateral extension of depletion regions beyond the gate edges into     | nm       |

|                   | the drain side                                                        |          |

| $d_{Dmax}$        | Maximum allowable $d_D$ under long channel approximation              | nm       |

| ds                | Lateral extension of depletion regions beyond the gate edges into     | nm       |

|                   | the source side                                                       |          |

| d <sub>Smax</sub> | Maximum allowable $d_S$ under long channel approximation              | nm       |

| $dV_{th}$         | Threshold voltage roll-off                                            | mV       |

| $E_1$             | Coefficient in generic solution for core potential along the y-       | unitless |

|                   | direction                                                             |          |

| $E_2$             | Coefficient in generic solution for core potential along the y-       | nm       |

|                   | direction                                                             |          |

| $E_c$             | Conduction band energy                                                | eV       |

| $E_D$             | Electric field at $x = L_g + d_D$                                     | V/cm     |

| $E_{De}$          | Electric field at $x = L_g + L_{De}$                                  | V/cm     |

| $E_{f,s}$         | Electron Fermi-level at the source end                                | eV       |

| $E_g$             | Bandgap energy of Si                                                  | eV       |

|                   |                                                                       |          |

| $E_i$              | Intrinsic Fermi-level energy                                      | eV               |

|--------------------|-------------------------------------------------------------------|------------------|

| $E_{ref}$          | Reference energy                                                  | eV               |

| $E_S$              | Electric field at $x = -d_S$                                      | V/cm             |

| $E_{Se}$           | Electric field at $x = -L_{Se}$                                   | V/cm             |

| $E_{ u}$           | Valence band energy                                               | eV               |

| $E_y$              | Vertical component of electric field                              | MV/cm            |

| f                  | Operating frequency                                               | Hz               |

| $F_{1}, F_{2}$     | Coefficients in generic solution for bottom shell potential along | V                |

|                    | the y-direction                                                   |                  |

| Fi, Fii, Fiii,     | Notations used to represent integrals along the x-direction in    | unitless         |

|                    | subthreshold drain current expression                             |                  |

| g, h               | Notations used in general solution for channel potential          | V                |

| GI, GII, GIII      | Notations used to represent integrals along the y-direction in    | nm               |

|                    | subthreshold drain current expression                             |                  |

| H(z)               | Arbitrary function dependent on variable 'z'                      | -                |

| i                  | Notations used to indicate regions I, II or III                   | -                |

| I <sub>ds,th</sub> | Drain current corresponding to threshold voltage                  | $\mu A$          |

| IOFF               | Off-current                                                       | nA               |

| ION                | On-current                                                        | mA               |

| j                  | Notations used to indicate regions II and III                     | -                |

| k                  | Boltzmann's constant                                              | J/K              |

| $k_1$              | Notation used in equations for calculating $L_{Se}$ and $L_{De}$  | nm <sup>-1</sup> |

| $k_2$              | Notation used in equations for calculating $L_{Se}$ and $L_{De}$  | unitless         |

| k3s, k3d, k4       | Notations used in equations for calculating $L_{Se}$ and $L_{De}$ | nm               |

| k5s, k5d           | Notations used in equations for calculating $L_{Se}$ and $L_{De}$ | $nm^2$           |

| $k_a, k_c$         | Notations used in transcendental equations in $d_S$ and $d_D$     | $V/nm^2$         |

| kb, ke, kg         | Notations used in transcendental equations in $d_S$ and $d_D$     | V/nm             |

| kd, kf, kh1, kh2   | Notations used in transcendental equations in $d_S$ and $d_D$     | V                |

| $L_{eff}$          | Effective channel length                                          | nm               |

| $L_D$              | Gate-to-drain underlap length                                     | nm               |

| L <sub>De</sub>    | Lateral drain extension at the centre of the undoped core         | nm               |

| L <sub>Dext</sub>  | Undoped drain underlap length                                     | nm               |

| $L_g$              | Gate length                                                       | nm               |

| $L_{g,L}$          | Gate length for long channel device                               | nm               |

|                    | 27272                                                             |                  |

| $L_{g,S}$              | Gate length for short channel device                           | nm                      |

|------------------------|----------------------------------------------------------------|-------------------------|

| $L_S$                  | Gate-to-source underlap length                                 | nm                      |

| L <sub>Se</sub>        | Lateral source extension at the centre of the undoped core     | nm                      |

| LSext                  | Undoped source underlap length                                 | nm                      |

| Lun                    | Gate-source/drain underlap length                              | nm                      |

| Na                     | Acceptor-type doping concentration                             | <i>cm</i> <sup>-3</sup> |

| N <sub>C</sub>         | Effective density of states for electrons conduction band      | <i>cm</i> <sup>-3</sup> |

| $N_0$                  | Core doping                                                    | <i>cm</i> <sup>-3</sup> |

| $N_d$                  | Donor-type doping concentration (or) shell doping              | <i>cm</i> <sup>-3</sup> |

| ne                     | Electron concentration                                         | <i>cm</i> <sup>-3</sup> |

| $N_{eq}$               | Equivalent core doping seen by the gate in central core region | <i>cm</i> <sup>-3</sup> |

| $n_i$                  | Intrinsic carrier concentration in Si                          | <i>cm</i> <sup>-3</sup> |

| $n_{i0}$               | Intrinsic carrier concentration in Si core region              | <i>cm</i> <sup>-3</sup> |

| <b>n</b> <sub>id</sub> | Intrinsic carrier concentration in Si top/bottom shell region  | <i>cm</i> <sup>-3</sup> |

| N <sub>sd</sub>        | Source/Drain donor-type doping                                 | <i>cm</i> <sup>-3</sup> |

| $N_V$                  | Effective density of states for holes in valence band          | <i>cm</i> <sup>-3</sup> |

| q                      | Electronic charge                                              | С                       |

| S                      | Subthreshold swing                                             | mV/dec                  |

| $S_1$                  | Subthreshold swing for low drain bias case                     | mV/dec                  |

| $S_2$                  | Subthreshold swing for high drain bias case                    | mV/dec                  |

| $S_L$                  | Subthreshold swing for long channel device                     | mV/dec                  |

| $S_S$                  | Subthreshold swing for short channel device                    | mV/dec                  |

| Т                      | Temperature                                                    | K                       |

| $T_{box}$              | Buried gate oxide thickness                                    | nm                      |

| T <sub>core</sub>      | Thickness of core region                                       | nm                      |

| $T_{ox}$               | Gate oxide thickness                                           | nm                      |

| Toxb                   | Back gate oxide thickness                                      | nm                      |

| Toxf                   | Front gate oxide thickness                                     | nm                      |

| $T_{si}$               | Si film thickness                                              | nm                      |

| $V_{bg}$               | Back gate voltage                                              | V                       |

| $V_{biD}$              | Built-in potential corresponding to channel doping $N_d$       | V                       |

| $V_{bi,eff}$           | Effective built-in potential                                   | V                       |

| V <sub>biSD</sub>      | Built-in potential corresponding to S/D doping $N_{sd}$        | V                       |

| $V_D$                  | Potential at $x = L_g + d_D$                                   | V                       |

|                        |                                                                |                         |

| $V_{De}$           | Potential at $x = L_g + L_{De}$                                  | V        |  |

|--------------------|------------------------------------------------------------------|----------|--|

| V <sub>ds1</sub>   | Low drain bias                                                   | V        |  |

| $V_{ds2}$          | High drain bias                                                  | V        |  |

| $V_{f}$            | Electron quasi-Fermi potential                                   | V        |  |

| $V_{FB}$           | Flatband voltage with respect to Fermi level of bulk silicon     | V        |  |

| $V_{fb}$           | Flatband voltage of gate with respect to intrinsic silicon       | V        |  |

| $V_{fb,bg}$        | Flatband voltage of back gate with respect to intrinsic silicon  | V        |  |

| $V_{fb,fg}$        | Flatband voltage of front gate with respect to intrinsic silicon | V        |  |

| $V_{fg}$           | Front gate voltage                                               | V        |  |

| $V_{gs}$           | Gate voltage/bias                                                | V        |  |

| $V_S$              | Potential at $x = -d_S$                                          | V        |  |

| $V_{Se}$           | Potential at $x = -L_{Se}$                                       | V        |  |

| $V_T$              | Thermal voltage                                                  | mV       |  |

| $V_{th}$           | Threshold voltage                                                | V        |  |

| V <sub>th1</sub>   | Threshold voltage for low drain bias case                        | V        |  |

| $V_{th2}$          | Threshold voltage for high drain bias case                       | V        |  |

| $V_{th,L}$         | Threshold voltage for long channel device                        | V        |  |

| $V_{th,S}$         | Threshold voltage for short channel device                       | V        |  |

| $W_g$              | Gate (channel) width                                             | $\mu m$  |  |

| X                  | Lateral direction                                                | -        |  |

| у                  | Vertical direction                                               | -        |  |

| Уm                 | Position of subthreshold conduction along y-direction            | nm       |  |

| β                  | Reciprocal of thermal voltage, $V_T$                             | $V^{-1}$ |  |

| Δ                  | Spacing between n+1 samples in trapezoidal rule                  | -        |  |

| $\Delta S$         | Degradation in subthreshold swing                                | mV/dec   |  |

| $\Delta V_{bi}$    | Change in built-in potential between $V_{biSD}$ and $V_{biD}$    | mV       |  |

| Eox                | Permittivity of gate oxide                                       | F/cm     |  |

| Esi                | Permittivity of silicon                                          | F/cm     |  |

| κ                  | Dielectric constant                                              | unitless |  |

| $\lambda_D$        | Extrinsic Debye length                                           | nm       |  |

| $\lambda_{Dd}$     | Extrinsic Debye length in shell region                           | nm       |  |

| $\lambda_{D0}$     | Extrinsic Debye length in core region                            | nm       |  |

| $\lambda_N$        | Natural length                                                   | nm       |  |

| $\lambda_{\gamma}$ | <i>Natural length at any location</i> $y = \gamma$               | nm       |  |

| XXIII              |                                                                  |          |  |

| $\mu_n$              | Mobility of electrons                                              | $cm^2/V$ -s |

|----------------------|--------------------------------------------------------------------|-------------|

| $\mu_{nd}$           | Electron mobility in shell region                                  | $cm^2/V$ -s |

| $\mu_{n0}$           | Electron mobility in core region                                   | $cm^2/V$ -s |

| ηs, η <sub>D</sub>   | Notations used in general solution for channel potential           | V           |

| $arphi_{bg}$         | Back gate metal workfunction                                       | V           |

| $arphi_{fg}$         | Front gate metal workfunction                                      | V           |

| $arphi_g$            | Gate metal workfunction                                            | eV          |

| $\phi_{bg}$          | Effective back gate voltage                                        | V           |

| $\phi_{fg}$          | Effective front gate voltage                                       | V           |

| $\phi_{gs}$          | Effective gate voltage                                             | V           |

| Xsi                  | Electron affinity's in Si                                          | eV          |

| $\psi, \Phi$         | Electrostatic potential                                            | V           |

| $\psi_b$             | Back surface potential                                             | V           |

| Ψc                   | Central potential                                                  | V           |

| $\psi_f$             | Front surface potential                                            | V           |

| $\psi_{Long}$        | Long channel central potential                                     | V           |

| $\psi_{Long,\gamma}$ | <i>Long channel central potential at any location</i> $y = \gamma$ | V           |

| $\psi_m$             | Channel potential at $y = y_m$                                     | V           |

| $\psi_S$             | Surface potential                                                  | V           |

| $\psi_\gamma$        | <i>Channel potential at any location</i> $y = \gamma$              | V           |

|                      |                                                                    |             |

# ACRONYMS

| Abbreviation     | Description                                       |

|------------------|---------------------------------------------------|

| 1D               | One-dimensional                                   |

| 2D               | Two-dimensional                                   |

| 3D               | Three-dimensional                                 |

| BTBT             | Band-to-Band Tunneling                            |

| СВ               | Conduction Band                                   |

| CMOS             | Complementary Metal Oxide Semiconductor           |

| CS               | Core-Shell                                        |

| CRV              | Contact Resistivity Variability                   |

| CSG              | Cylindrical Surrounding Gate                      |

| DG               | Double Gate                                       |

| DIBL             | Drain Induced Barrier Lowering                    |

| Eq.              | Equation                                          |

| FET              | Field-Effect Transistor                           |

| Fig.             | Figure                                            |

| G-S/D            | Gate-Source/Drain                                 |

| GAA              | Gate-All-Around                                   |

| HfO <sub>2</sub> | Hafnium oxide                                     |

| HP               | High Performance                                  |

| HVM              | High Volume Manufacturing                         |

| IC               | Integrated Circuit                                |

| IoT              | Internet-of-things                                |

| IM               | Inversion Mode                                    |

| JL               | Junctionless                                      |

| LP               | Low Power                                         |

| MOSFET           | Metal Oxide Semiconductor Field-Effect Transistor |

| mM               | more Moore                                        |

| n                | Donor-type                                        |

| NMOS             | n-type MOSFET                                     |

| NW               | Nanowire                                          |

|                  |                                                   |

| р                | Acceptor-type                     |

|------------------|-----------------------------------|

| PE(s)            | Poisson's Equation(s)             |

| PMOS             | p-type MOSFET                     |

| PPAC             | Performance, Power, Area and Cost |

| QCE              | Quantum Confinement Effect        |

| RDFs             | Random Dopant Fluctuations        |

| S/D              | Source/Drain                      |

| SDP              | Shell Doping Profile              |

| SCEs             | Short Channel Effects             |

| SDEs             | Source/Drain Extensions           |

| SG               | Single Gate                       |

| SiGe             | Silicon-Germanium                 |

| Si               | Silicon                           |

| SiO <sub>2</sub> | Silicon dioxide                   |

| SoC              | System-on-Chip                    |

| SOI              | Silicon-on-Insulator              |

| SP               | Standard Performance/Power        |

| TCAD             | Technology Computer Aided Design  |

| TG               | Triple Gate or Tri-gate           |

| ULP              | Ultra Low Power                   |

| VB               | Valence Band                      |

| WFV              | Workfunction Variability          |

|                  |                                   |

#### **Chapter 1**

### Introduction

#### **1.1 MOTIVATION**

The progressions in semiconductor industry are contributed by the farsighted vision of Gordon E. Moore, who projected that the transistors' density in an Integrated Circuit (IC) doubles every two years, which was later revised to 18 months [1], [2]. Since 1965, the famous 'Moore's law' has motivated the semiconductor industry to achieve smaller, denser and cheaper chips with higher computing performance, lower power, improved reliability and enhanced functionalities every couple of years [3]-[5]. Moore's law has also guided the semiconductor industry to define future goals for research and development of semiconductor devices [5]. The ever-shrinking of transistor dimensions has continued to transform the technology for over half-a-century extending from smartphones to supercomputers [3], [4]. Dennard's constant field scaling theory, proposed in 1974 [6], provided necessary assistance to fulfill criteria laid down by Moore's law until the early 2000s [7], [8]. Traditionally, downscaling has been adequate to obtain efficient ICs in terms of density, power, speed, functionality, etc., but is no longer viable in sub-50nm regimes due to the technological challenges in transistor scaling, interconnection, lithography, and circuit and memory designs [9]-[11]. In the present scenario, it is becoming increasingly challenging to keep pace with Moore's scaling projection. Thus, the semiconductor industry is in search of 'more Moore' technologies [12]-[15].

#### 1.1.1 More Moore

Instead of relying on the inherent benefits achieved by dimensional scaling, more Moore (mM) focuses on the advanced Complementary

Metal-Oxide-Semiconductor (CMOS) techniques [5], [13], [14]. mM solutions attempt to aggressively push the fundamental IC scaling limits at a reduced cost per transistor for the next-generation technologies [13], [14]. The applications involving efficient computing, extensive memory usage and enormous or instant data handling impose goals for mM technologies, such as mobile applications, Internet-of-things (IoT), big-data applications, high-performance computing, etc. [13]. To sustain mM scaling, logic and memory technologies must meet the Performance, Power, Area and Cost (PPAC) requirements in every 2-3 years for each node scaling [13].

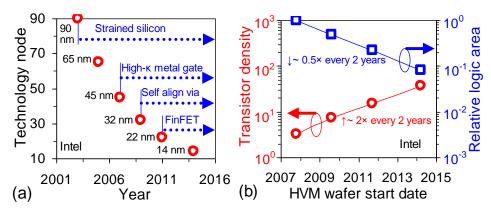

**Fig. 1.1 (a)** Intel transistor chronological innovations over six generations facilitating Moore's scaling [15]-[16]. **(b)** Scaling trends for Intel logic technologies showing High Volume Manufacturing (HMV) wafer start date-wise improvement in logic transistor density (MTr/mm<sup>2</sup>) [16] and relative logic area [15]. Data source: Intel (Bohr and Young, 2017 [15], and Bohr, 2018 [16]).

mM technologies involve the introduction of innovative structures, novel materials and new physical effects in CMOS platform [12]-[16]. The viable options for mM technologies at device architectural levels are multigate transistor (e.g. Fin Field-Effect Transistor (FET)), strained silicon, high- $\kappa$  gate oxide (e.g. HfO<sub>2</sub>), channel materials beyond silicon (e.g. SiGe, germanium, III-V materials, graphene), novel device topologies (e.g. junctionless transistor, tunnel FET) and beyond [12]-[16]. Fig. 1.1(a) summarizes the transistor innovations by Intel over the six generations to continue Moore's scaling via mM solutions after the saturation of traditional scaling in the early 2000s [15], [16]. The transistor innovations have led to almost 0.5 times improvement in the logic area scaling and approximately 2 times increment in the logic transistor density (MTr/mm<sup>2</sup>) in every two years [15], [16] (Fig. 1.1(b)). The scaling trends have also resulted in improved transistor performance, lower cost per transistor and reduced active power (by lowering the dynamic capacitance) [15], [16].

#### 1.1.2 Low Power Logic Technology

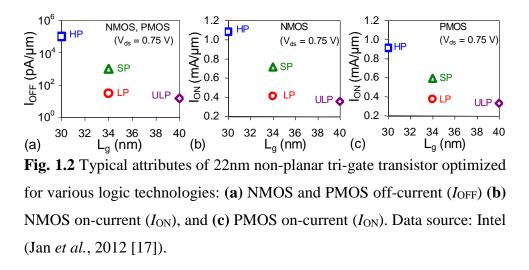

The semiconductor industry has continuously been involved in the development and production of digital ICs for both low power and high speed logic technology applications. Fig. 1.2(a)-(c) compares 22nm System-on-Chip (SoC) non-planar tri-gate transistors (both NMOS and PMOS) optimized for Ultra-Low Power (ULP), Low Power (LP), Standard Performance/Power (SP) and High Performance (HP) logic technologies in terms of gate length ( $L_g$ ),  $I_{OFF}$  and  $I_{ON}$  [17]. The off- and on-currents are evaluated at a supply (or drain) voltage ( $V_{ds}$ ) of 0.75 V. Due to the different nature of constraints; LP transistors widely differ from the HP transistors [17]. In particular, the performance of portable devices is constrained by battery usage, and hence, demands low power technology innovations [13]. The prime goal of LP technology is to trade-off speed performance for low standby power or low I<sub>OFF</sub> [13]. A scaled-down transistor possessing ideal subthreshold swing and a low value of drain induced barrier lowering is desirable for LP technology [17]. At the same I<sub>ON</sub> and a fixed operating frequency, an improved subthreshold swing can provide a better  $I_{ON}/I_{OFF}$  ratio at relatively low  $V_{ds}$  [18]. A feasible solution to achieve the same is to have enhanced electrostatic channel controllability through multiple gates in a transistor [19]-[22].

#### **1.2 BASIC BACKGROUND**

This section discusses a few essential topics before stating the objective and scope of the thesis. The section thereby facilitates a better understanding of the research work presented in this thesis.

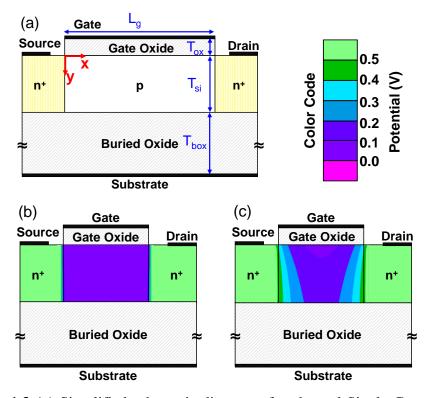

**Fig. 1.3 (a)** Simplified schematic diagram of *n*-channel Single Gate (SG) Silicon-on-Insulator (SOI) MOSFET [21], [23], [24]. Illustration of short channel effects using two-dimensional potential contours in the channel region for (**b**) long channel ( $L_g = 500$  nm) and (**c**) short channel ( $L_g = 50$  nm) devices. In Fig. 1.3(b),(c), each color corresponds to a certain potential range, as indicated by the above color codes. The simulations have been carried out through Atlas TCAD tool [25].

#### **1.2.1 Short Channel Effects**

Short Channel Effects (SCEs) are the undesirable behavior observed in the characteristics of Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) due to a reduction in the gate length, i.e. for short channel devices [26]-[28]. Fig. 1.3(a) depicts a simplified schematic view of *n*-channel SG SOI MOSFET [21], [23], [24]. To understand SCEs, two-dimensional (2D) potential contours are presented in Fig. 1.3(b) and Fig. 1.3(c) under zero applied biases ( $V_{gs} = V_{ds} = 0$  V) condition for long ( $L_g = 500$  nm) and short ( $L_g = 50$  nm) channel MOSFETs, respectively. Other device parameters are channel doping (*p*-type) of 10<sup>16</sup> cm<sup>-3</sup>, source/drain doping (*n*-type) of 10<sup>20</sup> cm<sup>-3</sup>, gate oxide thickness ( $T_{ox}$ ) of 2 nm, silicon film thickness ( $T_{si}$ ) of 10 nm, buried oxide thickness ( $T_{box}$ ) of 300 nm and midgap value (4.72 eV) of gate workfunction.

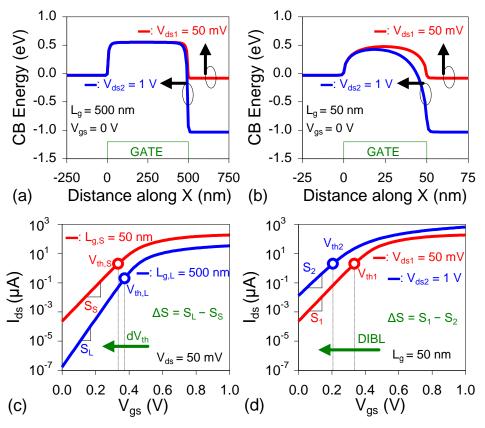

**Fig. 1.4** Variations of Conduction Band (CB) energy along the lateral (x-) direction with drain bias for (**a**) long channel and (**b**) short channel MOSFETs. Comparison of transfer ( $I_{ds}$ - $V_{gs}$ ) characteristics: (**c**) long channel ( $L_{g,L}$ ) versus short channel ( $L_{g,S}$ ) cases and (**d**) low drain bias ( $V_{ds1}$ ) versus high drain bias ( $V_{ds2}$ ) cases.

In long channel devices, source and drain regions are distant from each other such that their electric fields have negligible effects over the channel potential underneath the gate. The electrostatics is mostly controlled by the gate and is one-dimensional (1D) (i.e. varying mainly along the vertical (*y*-direction) [26]. The variation of potential in the *y*-direction for the long channel case in Fig. 1.3(b) is not significantly observed due to the choice of identical scale in Fig. 1.3(b),(c). However, due to the proximity of source and drain regions at shorter gate lengths, their electric fields interfere with the gate electric field and compete for the depletion charge in the channel [21], [22]. The lateral encroachment of source and drain electric fields deteriorates control of the gate over the channel. The potential distribution becomes 2D, rather than 1D (in Fig. 1.3(c)), having significant variations in vertical as well as lateral directions [26].

Fig. 1.4(a)-(b) compares the off-state ( $V_{gs} = 0$  V) energy barrier seen by the electrons for low ( $V_{ds} = 50$  mV) and high ( $V_{ds} = 1$  V) drain biases for long and short channel cases, respectively. In the long channel case, the channel electrostatics is controlled by the gate field, and therefore, the energy band is flat in most of the channel (Fig. 1.4(a)). Only the near ends of the channel (adjacent to source/drain regions) are affected by the source and drain electric fields. The energy barrier height remains unaffected even if the drain field strengthens with increasing drain bias (when  $V_{ds}$ changes from 50 mV to 1 V). However, for a short channel case (Fig. 1.4 (b)), the intervention of source and drain electric fields against the gate field causes the barrier height to lower, as compared to the long channel case. The energy barrier lowering heightened when the drain-channel junction is more reverse biased (i.e.  $V_{ds}$  rises from 50 mV to 1 V).

SCEs can be observed in the device characteristics through a reduction in threshold voltage and degradation of subthreshold swing [21], [22], [26]-[28], as indicated in Fig. 1.4(c),(d):

i) Reduction in threshold voltage [21], [22], [26]-[28]: Threshold voltage ( $V_{\text{th}}$ ) signifies the gate voltage at which significant drain current flows through the transistor, and the device is considered to be turned on [27], [28]. In Fig. 1.4(c),(d),  $V_{\text{th}}$  is usually extracted from  $I_{\text{ds}}$ - $V_{\text{gs}}$  curve of the transistor using the constant current method [29]. In a long channel device,  $V_{\text{th}}$  is independent of the gate length. While in a

short channel device, the lowered energy barrier causes easy injection of carriers (electrons in *n*-channel MOSFET) from source to drain [26]-[28]. This barrier lowering tends to raise the subthreshold current, thereby forcing transistor to turn-on at a relatively low gate bias, and hence, at reduced threshold voltage. The reduction in  $V_{\text{th}}$  with decreasing  $L_{\text{g}}$  (relative to long channel case) is known as the 'threshold voltage roll-off ( $dV_{\text{th}}$ )' [26], [27], as elucidated in Fig. 1.4(c). The reduction in  $V_{\text{th}}$  heightened when a high drain bias is applied, and the effect is termed as 'Drain Induced Barrier Lowering (DIBL)' [26]-[28], as illustrated in Fig. 1.4(d). The short channel threshold voltage is a function of gate length as well as drain bias.

ii) Degradation in the subthreshold swing [21], [22], [26]-[28]: Subthreshold swing (*S*), or inverse subthreshold slope or simply subthreshold slope, is defined as the gate voltage required for changing the drain current by a decade, below threshold [22], [26]. Subthreshold swing is a direct indication of gate controllability over the channel region. It has a minimum limit of 2.3 times the thermal voltage (~60 mV/dec at room temperature) under perfect gate-channel electrostatic coupling (ideal case) [22], [26]. In a long channel device, the subthreshold drain current varies exponentially with the gate bias and is independent of drain bias (provided  $V_{ds} >$  few times the thermal voltage) [28]. While in short channel devices, the gate does not solely control the channel electrostatics, and hence, a degraded *S* value (> 60 mV/dec) is usually achieved [26], [28]. In short channel MOSFET, subthreshold swing increases with both decreasing gate length and increasing drain bias [28], as depicted in Fig. 1.4(c),(d) by  $\Delta S$ .

#### **1.2.2 Junctionless Transistor**

State-of-art transistors have reached to such dimensions where the formations of pn junctions with doping concentration gradients changing within a few nanometers are necessary. The need for ultra-sharp pn junctions imposes severe limitations on fabrication processes and thermal budgets. In 2009, Colinge *et al.* [30] experimentally demonstrated a new multi-gate nanowire transistor architecture named as the 'Junctionless'

(JL) transistor. They were shown to exhibit full CMOS functionality without radically altering the CMOS process technology [30], [31]. Fundamentally, a JL transistor is a gated resistor without any junctions [31]. Unlike conventional inversion-mode (IM) devices (in Fig. 1.5(a)), JL MOSFET (in Fig. 1.5(b)) possesses identical doping types and concentrations in the gated, source and drain regions. Since the doping gradients between the channel and source/drain regions are non-existent, no diffusion can take place.

**Fig. 1.5** Schematic diagram showing longitudinal cross-sectional view of (a) conventional inversion mode  $(n^+-p-n^+)$  MOSFET [21] and (b) junctionless  $(n^+-n^+-n^+)$  transistors [31], elucidating difference in doping profile across the semiconductor film.

**Fig. 1.6 (a)** Schematic view of *n*-channel double gate JL MOSFET. (b) Typical variations of drain current ( $I_{ds}$ ) and central potential ( $\psi_C$ ) extracted at  $x = L_g/2$ ,  $y = T_{si}/2$  with gate bias at  $V_{ds} = 50$  mV, marked with threshold (symbol:  $\circ$ ) and flatband (symbol:  $\Box$ ) voltages. Device parameters:  $L_g = 50$ nm,  $T_{ox} = 2$  nm,  $T_{si} = 10$  nm,  $N_d$  ( $n^+$ ) =  $10^{19}$  cm<sup>-3</sup> and p+ polysilicon gate.

The key considerations to be taken care while fabricating a JL transistor [31] are as follows:

- a) Appropriate selection of gate metal workfunction [31]: Due to identical doping type across the semiconductor film, JL MOSFET behaves as a normally-on device. A high (low) value of gate workfunction for *n*-channel (*p*-channel) JL device is needed to turn off the device and to obtain positive (negative) values of the threshold voltage.

- b) Narrow and thin semiconductor film [31]: A sufficiently narrow and thin semiconductor film should be utilized such that the gate electric field can fully deplete the majority carriers from the channel.

- c) Heavy doping [31]: To supply significant drive current in the on-state of the device, the semiconductor film is preferred to be heavily doped.

**Fig. 1.7** Energy band diagrams extracted along the semiconductor film at mid-gate position ( $x = L_g/2$ ), illustrating typical conduction mechanism in an *n*-channel DG JL MOSFET for (**a**)  $V_{gs} = 0$  V ( $< V_{th}$ ), (**b**)  $V_{gs} = 0.285$  V ( $= V_{th}$ ), (**c**)  $V_{gs} = 1.04$  V ( $= V_{FB}$ ) and (**d**)  $V_{gs} = 1.5$  V ( $> V_{FB}$ ). Device parameters are the same, as mentioned in Fig. 1.6.