# STEP UP PWM DC-DC CONVERTERS BASED ON QUASI Z-SOURCE AND QUADRATIC BOOST CONVERTER

Ph.D. Thesis

## By KESHAV PATIDAR

## DISCIPLINE OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE FEBRUARY 2015

# STEP UP PWM DC-DC CONVERTERS BASED ON QUASI Z-SOURCE AND QUADRATIC BOOST CONVERTER

## A THESIS

Submitted in partial fulfillment of the requirements for the award of the degree of DOCTOR OF PHILOSOPHY

> by KESHAV PATIDAR

DISCIPLINE OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY INDORE FEBRUARY 2015

### ACKNOWLEDGEMENTS

Firstly, I would like to express my sincere gratitude to my supervisor Prof. Amod C. Umarikar for the encouragement, valuable guidance and support throughout the research work. I have been privileged enough to work with him and I am sure the rigorous research attitude that I have learnt from him will inspire me for the rest of my life.

I would like to show my gratitude to the members of the committee, Prof. Ram Bilas Pachori and Prof. Anand Parey for their advices and technical feedback. I extend my thanks to the institute for all the resources that helped me in successful completion of my degree.

I acknowledge Prof. S. Vasudevan for his support and encouragement during my research work. I am very much grateful to Mr. Raghvendra, Mr. Shailendra, Ms. Ujwalla and Mr. Suryavanshi for their support.

I would like to thank my friends T. Karthik, Varun Bajaj, Dheeraj Sharma, Shivnarayan, Sunil Yadav, Vinod Sharma for lending me their generous support whenever needed.

Finally, I would like to thank my family members for their kind support, patience and understanding.

Dedicated to my Parents

### ABSTRACT

Step-up DC-DC converters are having increasing demand because of its applications in photovoltaic (PV) power generation, fuel cell based energy conversion, uninterrupted power supplies (UPS) and battery powered equipment. In general, a conventional boost converter can be adopted to provide a high step-up voltage gain with a large duty ratio. However, the conversion efficiency and the step-up voltage gain are limited due to the constraints of the losses of power switches and diodes, the equivalent series resistance of inductors and capacitors, and the reverse-recovery problem of diodes.

Therefore, a step-up converter with a low duty ratio to achieve high efficiency and high voltage gain is very important for these applications. In order to improve the conversion efficiency at low power, non-isolated converters are preferred for these high step-up applications. Among non-isolated topologies reported in literature for step up applications, Z-source converter and Quasi Z-source converter topologies are comparatively new with many desirable features.

The work in the thesis focuses on study and development of new configurations based on Quasi Z-source DC-DC converters and quadratic boost converter for high step-up applications. Fourth order step up converter based on quasi Z-source converter is presented with its small signal mode and controller design in second chapter of thesis. The fourth-order converter poses many desirable features. Proposed converter's design equations are established and same are validated through laboratory prototypes. The work also focuses on control of these converters, One Cycle Control technique is used for controlling output voltage of Z-source and quasi Z-source based converters.

Further, tapped-inductor and coupled-inductor variations of QZS based fourth order DC-DC converter are proposed. Tapped-inductor is utilized for voltage gain enhancement of fourth-order converter. In tapped-inductor based configuration voltage gain of the converter is depend upon duty ratio and turns ratio. Voltage gain expressions for ideal and non-ideal tapped-inductor based converter is derived and experimentally verified. The main aim of coupled-inductor based converter is to reduce input current ripple of fourth order quasi z-source converter. Theoretical analysis of current ripple in coupled inductor is presented and also verified using simulation and hardware results.

A high step up converter based on fourth order quasi Z-source converter and boost converter is derived. Performance of non-ideal converter is theoretically analyze and demonstrated. Small signal model of the converter is utilized for controller design of high step up converter. Two converter configurations based on quadratic boost converter and tapped-inductor are introduced in sixth chapter of thesis. Performance of both converters for different load resistance and for different combination of turns ratio is studied.

## **TABLE OF CONTENTS**

| ABSTRACT        | i   |

|-----------------|-----|

| LIST OF FIGURES | vii |

| LIST OF TABLES  | Xv  |

| NOMENCLATURE    |     |

| ACRONYMS        | xxi |

## **Chapter1: Introduction and literature review**

| 1.1 Introduction                        | 1  |

|-----------------------------------------|----|

| 1.2 Review of step-up DC-DC converters  | 2  |

| 1.2.1 Non-isolated converter topologies | 3  |

| 1.2.2 Isolated converter topologies     | 14 |

| 1.3 Scope and objectives of thesis      | 20 |

| 1.4 Contribution of thesis              | 21 |

| 1.5 Organization of thesis              | 22 |

## Chapter 2:A Fourth Order PWM DC-DC Boost Converter

### derived from Quasi Z-Source Topology

| 2.1 Introduction                                                            | 25  |

|-----------------------------------------------------------------------------|-----|

| 2.2 Idealized circuit analyses                                              | .27 |

| 2.2.1 For time interval $0 \le t \le DT$                                    | .27 |

| 2.2.2 For time interval $DT \le t \le T$                                    | .30 |

| 2.2.3 Peak and average values of currents and voltages for switch           | .33 |

| 2.2.4 Design of Capacitance values                                          | .34 |

| 2.3 Boundary between CCM / DCM and analysis in DCM                          | .34 |

| 2.3.1 Minimum inductance value for CCM                                      | .34 |

| 2.3.2 DC voltage transfer ratio in DCM and expression for remaining current | .35 |

| 2.4 Power losses and dc voltage transfer ratio for non-ideal converter      | .38 |

| 2.4.1 Power losses in QZ-source based dc-dc converter in CCM                | .38 |

| 2.4.2 DC voltage transfer function of non-ideal converter                   | .40 |

| 2.5 Small-signal model and controller design                                | .41 |

| 2.5.1 Small-signal model                                | 41      |

|---------------------------------------------------------|---------|

| 2.5.2 Controller design                                 | 43      |

| 2.6 Results and comparison                              | 47      |

| 2.6.1 Simulation and experimental results               | 47      |

| 2.6.2 Comparison with PWM Z-source DC-DC converter [30] | 54      |

| 2.7 Conclusion                                          | 57      |

| Chapter 3                                               |         |

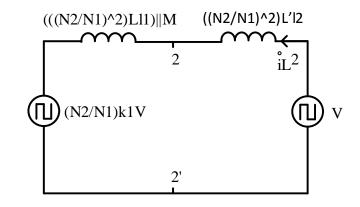

| 3.1 Tapped-inductor Quasi-Z-source Based PWM DC-DC con  | iverter |

| 3.1.1 Introduction                                      | 59      |

| 3.1.2 Operating principle of the converter              | 60      |

| 3.1.3 Steady state analysis of the converter            | 62      |

| 3.1.5 Performance analysis of the converter             | 68      |

| 3.1.1 Introduction                                                |

|-------------------------------------------------------------------|

| 3.1.2 Operating principle of the converter                        |

| 3.1.3 Steady state analysis of the converter                      |

| 3.1.5 Performance analysis of the converter                       |

| 3.1.6 Simulation and experimental results72                       |

| 3.1.7 Conclusion                                                  |

| 3.2: A step-up PWM DC-DC converter with zero input current ripple |

| 3.2.1 Introduction                                                |

| 3.2.2 Coupled inductor based high step-up converter               |

| 3.2.2.1 Steady state analysis of the converter                    |

| 3.2.3 Analysis of current ripple                                  |

| 3.2.3.1 Current ripple in continuous conduction mode              |

| 3.2.3.2 Current ripple in discontinuous conduction mode           |

| 3.2.4 Experimental set-up                                         |

| 3.2.5 Simulation and experimental results                         |

| 3.2.6 Conclusion                                                  |

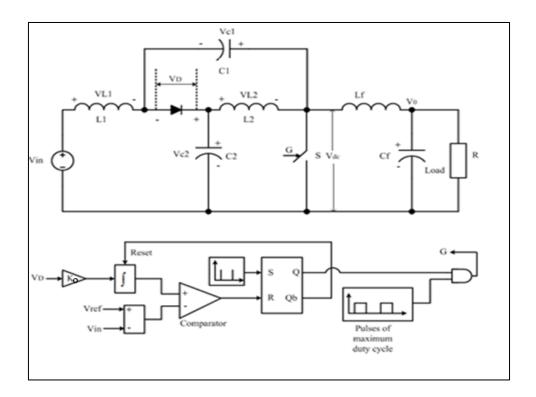

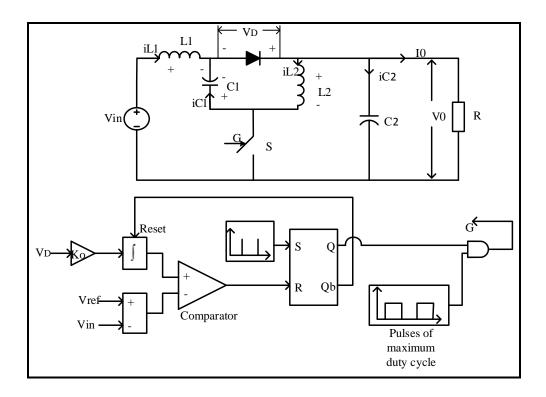

## Chapter 4: One Cycle control of Z-source, Quasi-Z-source and fourthorder step-up DC-DC Converters

| 4.1 Introduction                                                      | 97           |

|-----------------------------------------------------------------------|--------------|

| 4.2 One Cycle Control Method                                          |              |

| 4.3 One Cycle Control of Z Source DC-DC Converter                     | 100          |

| 4.4 One Cycle Control of Quasi-Z Source DC-DC converter and fourth or | rder Step-up |

| DC-DC Converter                                    | 104  |

|----------------------------------------------------|------|

| 4.5 Simulation and experimental Results            | .108 |

| 4.5.1 Z Source DC-DC Converter                     | .109 |

| 4.5.2 Quasi Z source DC-DC converter               | .111 |

| 4.5.3 OCC for fourth-order step up DC-DC converter | .117 |

| 4.6 Discussion                                     | .121 |

| 4.7 Conclusion                                     | .123 |

## Chapter 5: A High Step-up PWM DC-DC converter based on

## Quasi-Z-source Topology

| 5.1 Introduction                                                         | 125 |

|--------------------------------------------------------------------------|-----|

| 5.2 Steady-state analysis and boundary condition for DCM                 | 126 |

| 5.2.1 Steady state analysis                                              | 126 |

| 5.2.3 Converter passive elements design                                  | 130 |

| 5.2.4 Boundary condition between CCM/DCM                                 | 132 |

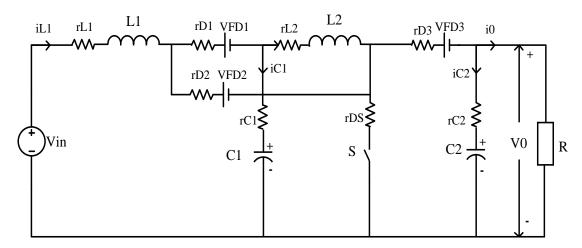

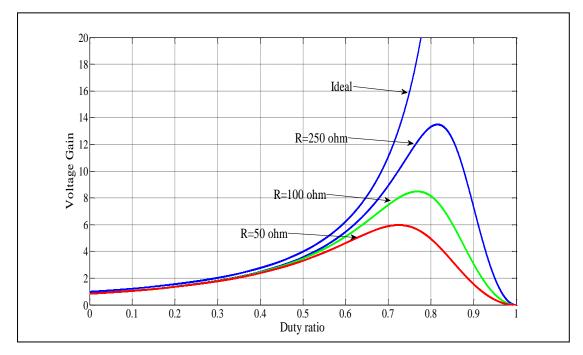

| 5.3 Power loss analysis and Voltage gain of non-ideal converter          | 133 |

| 5.3.1 Power loss analysis for converter in CCM                           | 133 |

| 5.3.2 DC voltage transfer gain of non-ideal high step up DC-DC converter | 136 |

| 5.4 Small-signal model and controller design                             | 137 |

| 5.4.1 Small-signal model                                                 | 137 |

| 5.5 Simulation and Experimental Results                                  | 143 |

| 5.6 Conclusion                                                           | 156 |

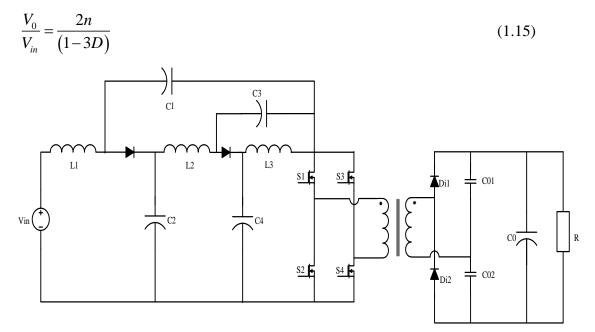

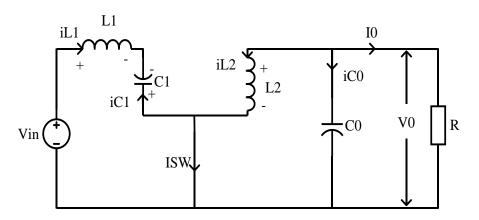

## Chapter 6: High step-up converters based on quadratic boost

### converter

| 6.1 Introduction1                                                            | 57  |

|------------------------------------------------------------------------------|-----|

| 6.2 Principle of operation and Steady state analysis1                        | 58  |

| 6.2.1 Semi-tapped quadratic boost converter1                                 | 59  |

| 6.2.2 Fully-tapped quadratic boost converter1                                | 61  |

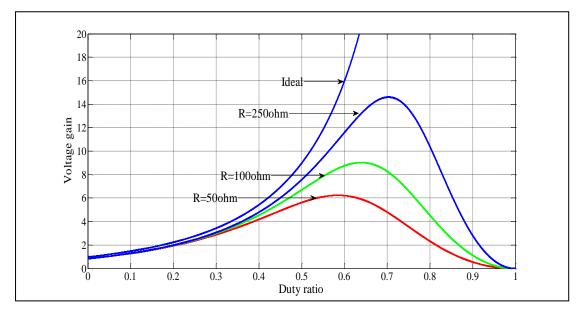

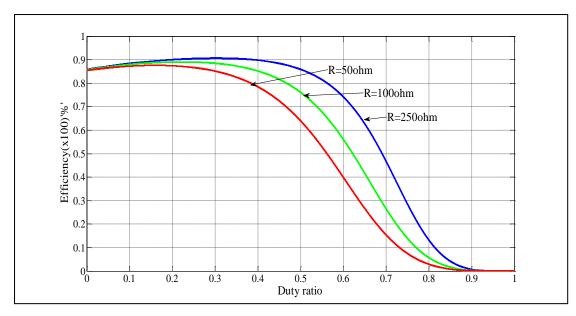

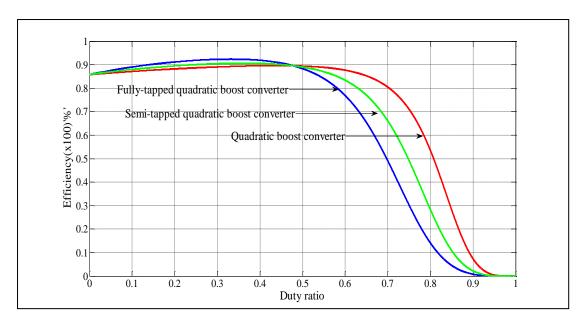

| 6.3 Voltage gain and efficiency of converters1                               | 64  |

| 6.3.1 Voltage gain and efficiency of quadratic boost converter               | 165 |

| 6.3.2 Voltage gain and efficiency for semi-tapped quadratic boost converter1 | 68  |

| 6.3.3 Voltage gain and efficiency of fully- tapped quadratic boost converter172 |

|---------------------------------------------------------------------------------|

| 6.4 Comparison between quadratic boost, semi-tapped quadratic boost and fully-  |

| tapped quadratic boost converter174                                             |

| 6.4.1 Comparison of voltage gain and efficiency174                              |

| 6.4.2 Comparison for voltage stress on active and passive switches              |

| 6.5 Simulation and experimental results                                         |

| 6.6 Conclusion                                                                  |

| Chapter 7: Conclusions                                                          |

| Conclusions |

|-------------|

|-------------|

| 191 |

|-----|

|     |

|     |

|     |

|     |

|     |

## LIST OF FIGURES

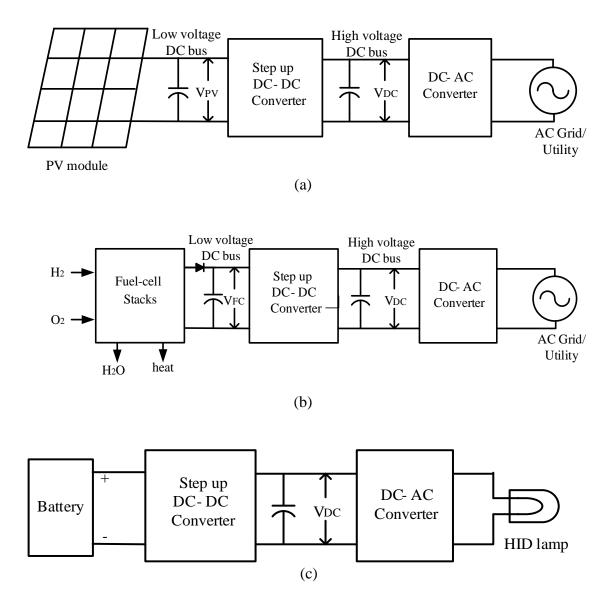

| 1.1      | : Applications of high step-up DC-DC converters (a) PV power generatio |     |

|----------|------------------------------------------------------------------------|-----|

| 1.2      | system,(b) Fuel-cell power generation system and (c) HID lamp ballast  |     |

| 1.2      | : Boost converter                                                      |     |

| 1.3(a)   | : Interleaved boost converter                                          | 4   |

| 1.3(b)   | : Coupled-inductor interleaved boost converter                         | .4  |

| 1.4      | : Three level boost converter                                          | .5  |

| 1.5(a)   | : Cascaded boost converter                                             | 6   |

| 1.5(b)   | : Quadratic boost converter                                            | 6   |

| 1.6(a)   | : Switched-inductor boost converter                                    | .7  |

| 1.6(b)   | : Switched-inductor with active network circuit converter              | 7   |

| 1.7(a)   | : Coupled-inductor high step-up converter                              | .8  |

| 1.7(b)   | : High step-up flyback-boost converter using coupled inductor          | .8  |

| 1.8(a)   | : High step-up converter with switched capacitor                       | .9  |

| 1.8(b)   | : High step-up converter with multilevel cell                          | 9   |

| 1.9(a)   | : High step-up converter presented in [19]                             | 10  |

| 1.9(b)   | : High step-up converter presented in [22]                             | .11 |

| 1.10(a)  | : High step-up converter presented in [24]                             | .11 |

| 1.10 (b) | : High step-up converter presented in [25]                             | .12 |

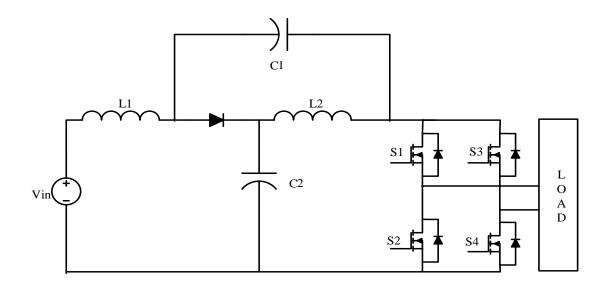

| 1.11(a)  | : Z-source DC-DC converter                                             | .13 |

| 1.11(b)  | : Quasi Z-source DC-DC converter                                       | .13 |

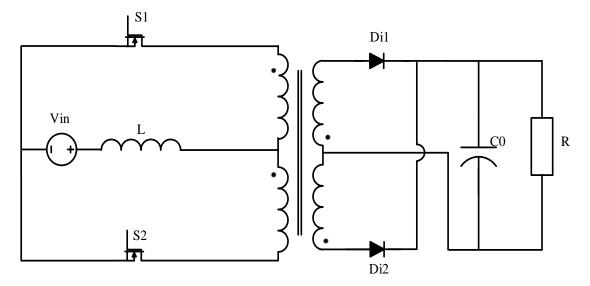

| 1.12(a)  | : Full-bridge isolated step-up converter                               | .14 |

| 1.12(b)  | : Isolated step-up converter based on push-pull configuration          | 15  |

| 1.12 (c) | : Active clamp isolated step-up converter                              | .15 |

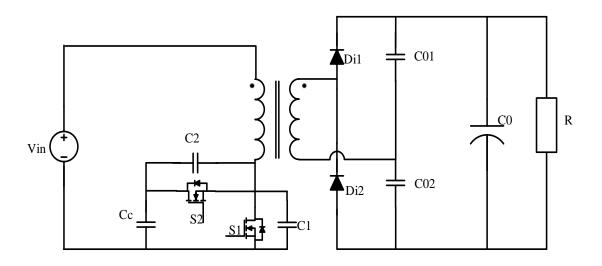

| 1.13(a)  | : Half-bridge resonant converter                                       | .16 |

| 1.13(b)  | : Resonant half-bridge dual converter                                  | .17 |

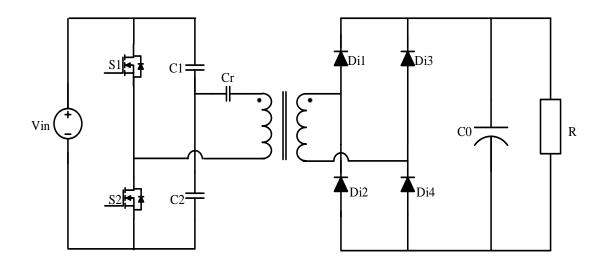

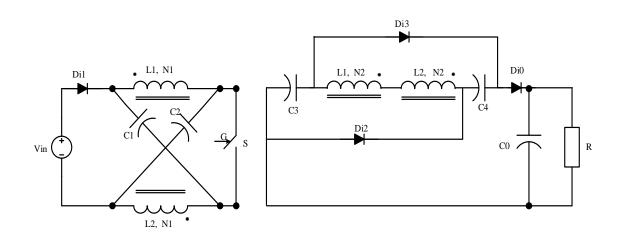

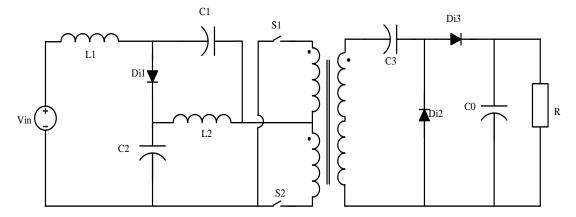

| 1.14(a)  | : Z-source isolated DC-DC converter                                    | .17 |

| 1.14 (b) | : Quasi Z-source isolated DC-DC converter                              | .18 |

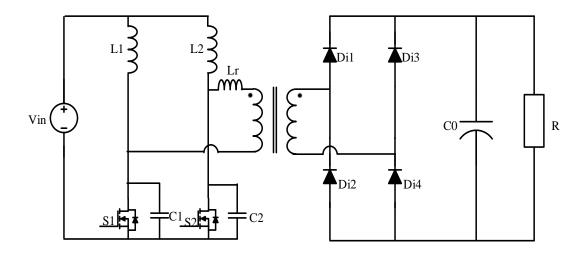

| 1.14(c)  | : QZSI based isolated high step-up DC-DC converter                     | .19 |

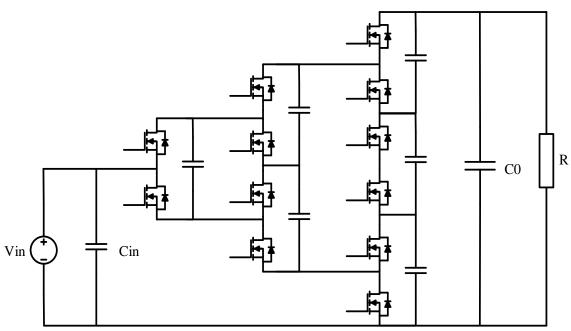

| 1.14(d)  | : Cascaded QZS network based high step-up converter                    | 19  |

| 1.14(e) | : QZS push-pull based high step-up converter                                          |

|---------|---------------------------------------------------------------------------------------|

| 2.1     | : Single phase Quasi Z-source inverter                                                |

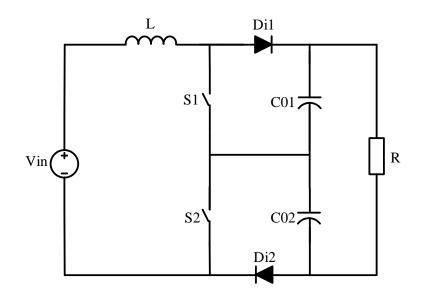

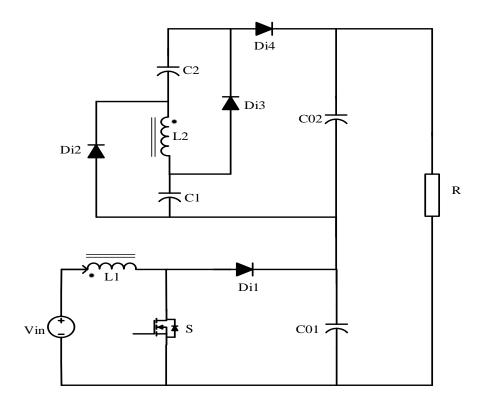

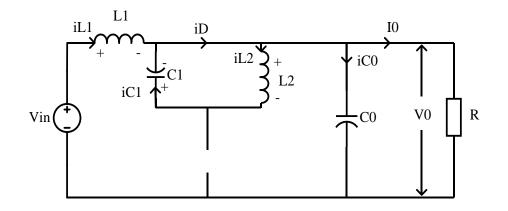

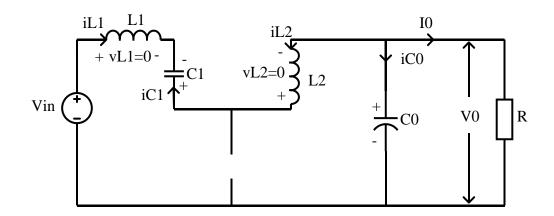

| 2.2     | : Fourth order step-up converter                                                      |

| 2.3(a)  | : Equivalent circuit of converter when S is ON27                                      |

| 2.3(b)  | : Equivalent circuit of converter when S is OFF for CCM28                             |

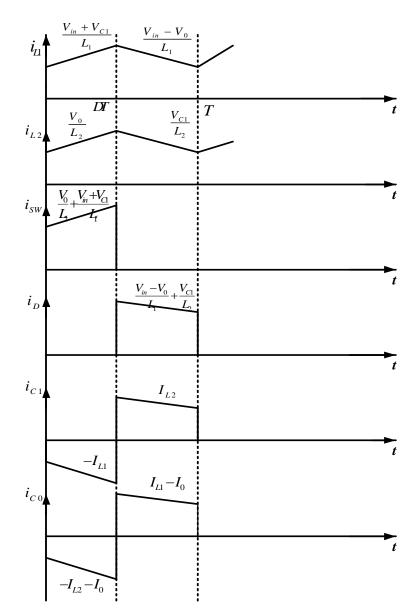

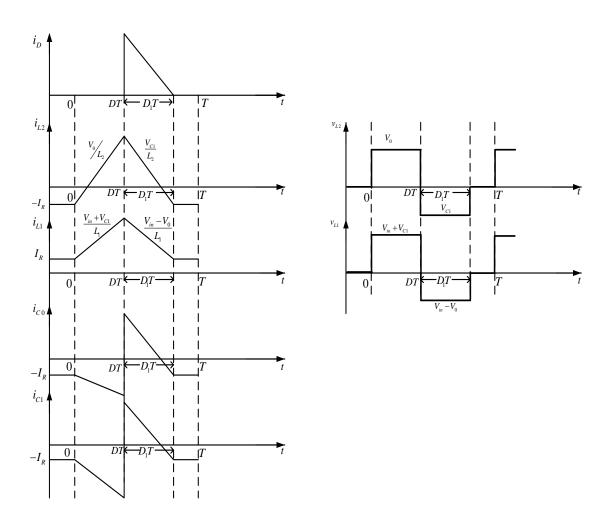

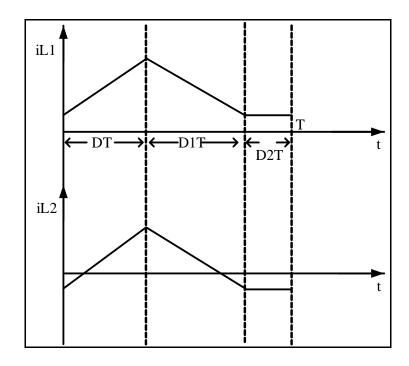

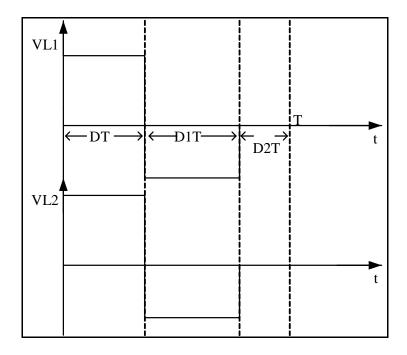

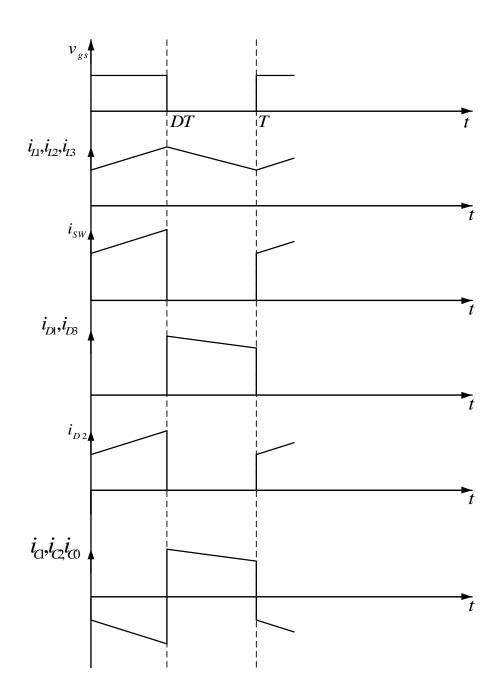

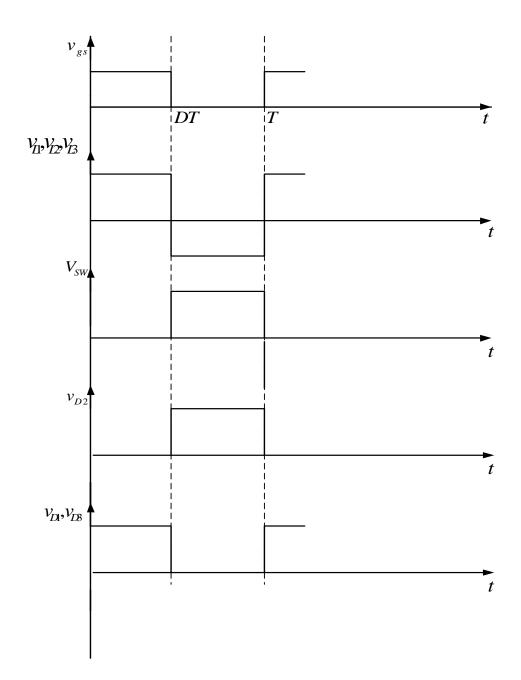

| 2.4(a)  | : Idealized current Waveforms for CCM                                                 |

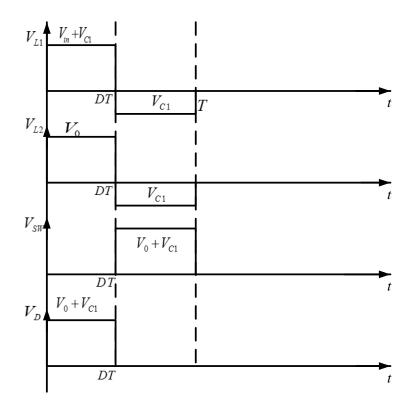

| 2.4(b)  | : Idealized voltage waveforms for CCM                                                 |

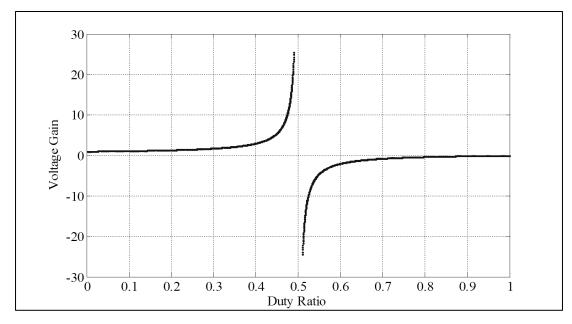

| 2.5     | : Voltage Gain                                                                        |

| 2.6(a)  | : Equivalent circuit of converter for DCM35                                           |

| 2.6(b)  | : Idealized current waveforms for DCM                                                 |

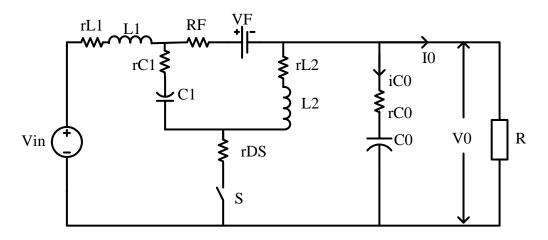

| 2.7     | : Equivalent circuit for Non-ideal converter                                          |

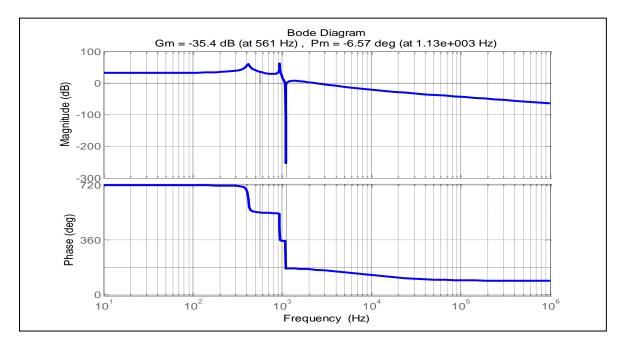

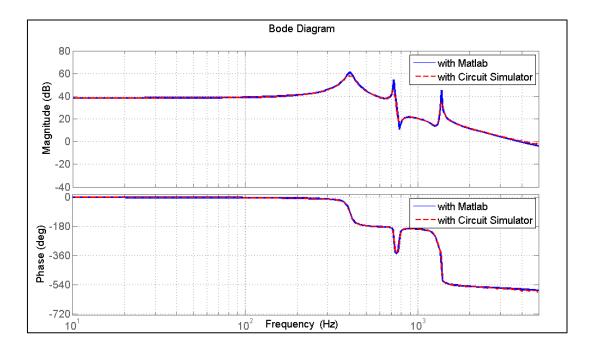

| 2.8(a)  | : Frequency response of system without controller44                                   |

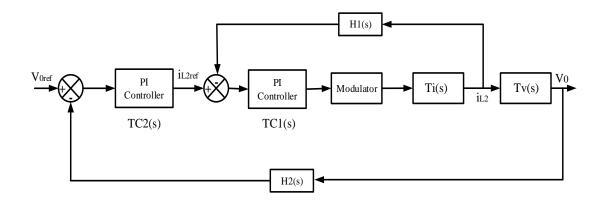

| 2.8(b)  | : Complete two loop control for average current control45                             |

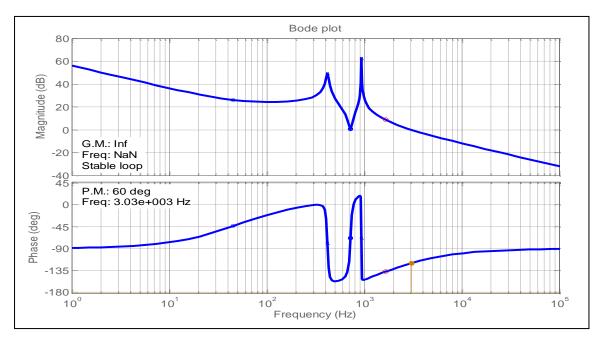

| 2.8(c)  | : Bode plot of current control loop with PI controller45                              |

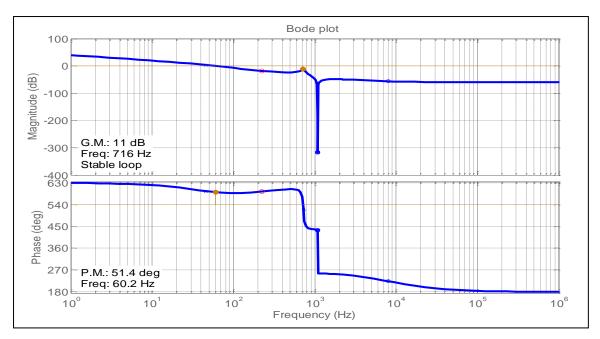

| 2.8(d)  | : Bode plot of voltage control loop with PI controller                                |

| 2.9(a)  | : Frequency response of overall system46                                              |

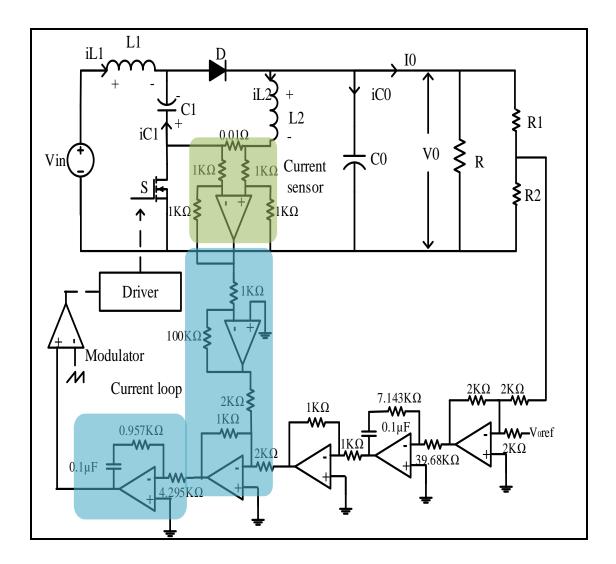

| 2.9(b)  | : Switching regulator using PWM QZS converter47                                       |

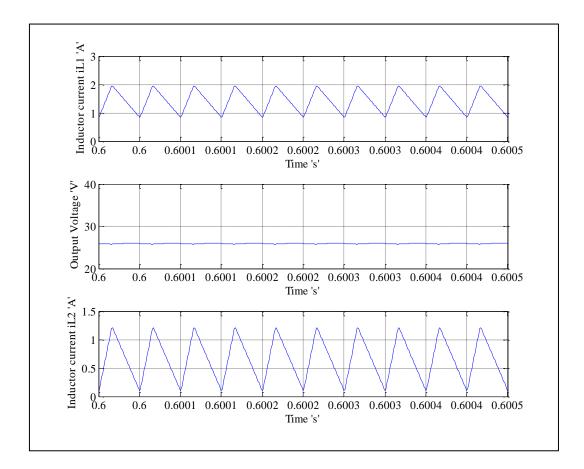

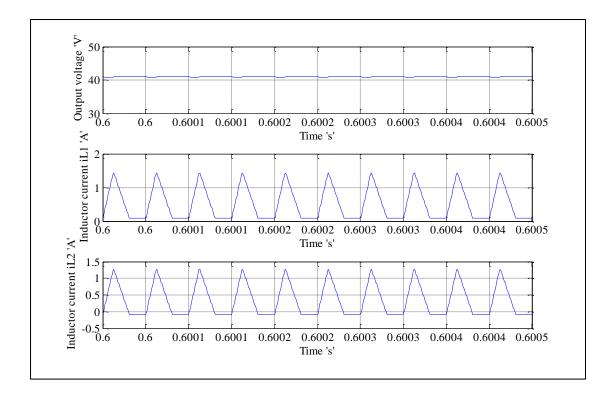

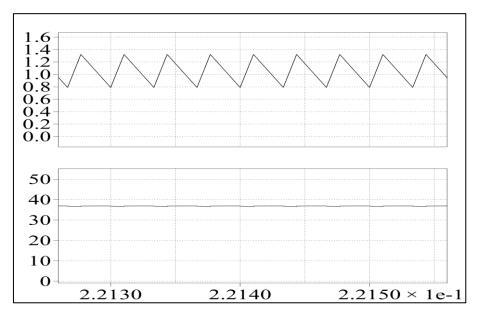

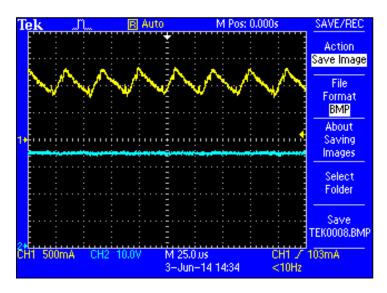

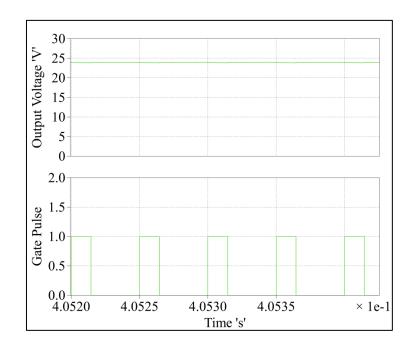

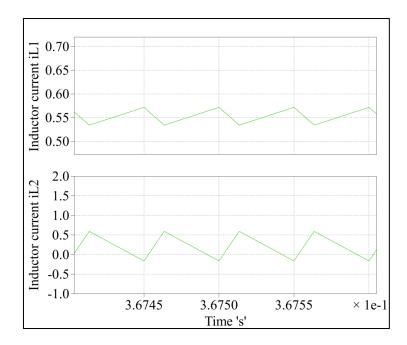

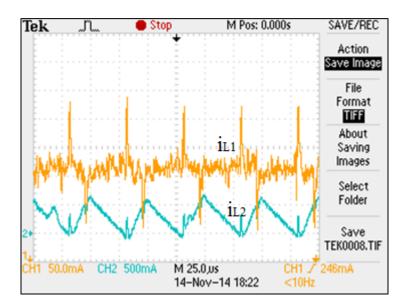

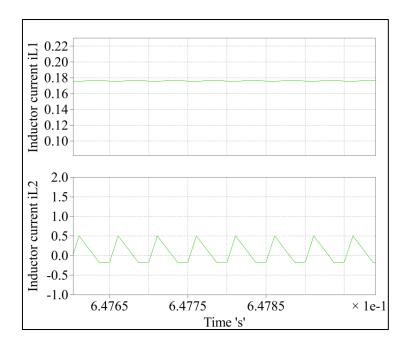

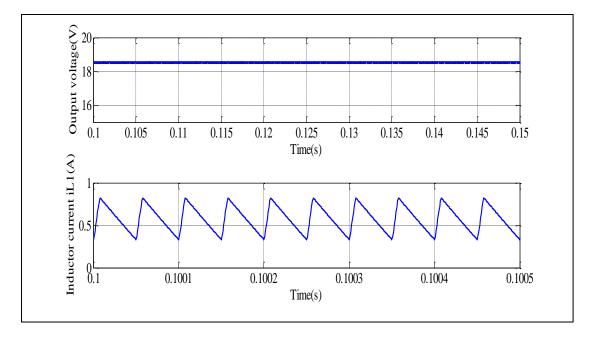

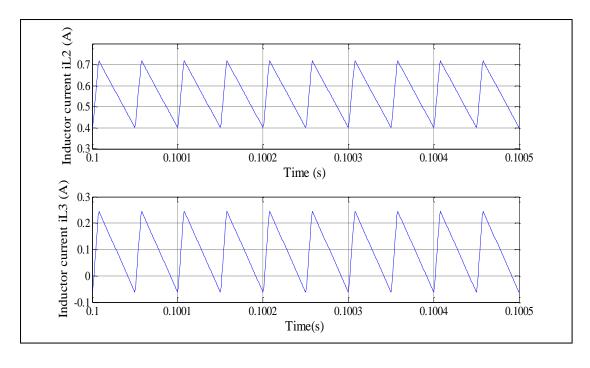

| 2.10    | : Simulation results in CCM for D=0.3 and $V_{in}$ =15V of output voltage,            |

|         | inductor current i <sub>L1</sub> and i <sub>L2</sub>                                  |

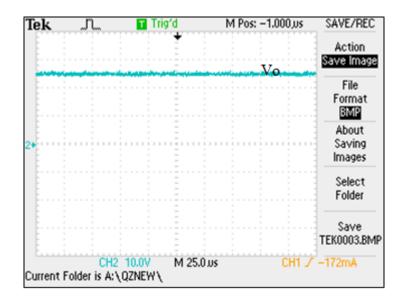

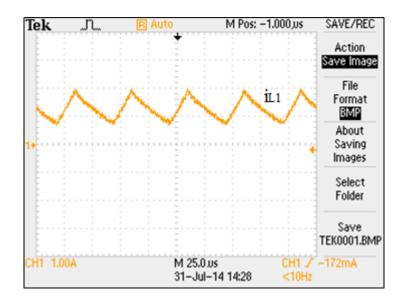

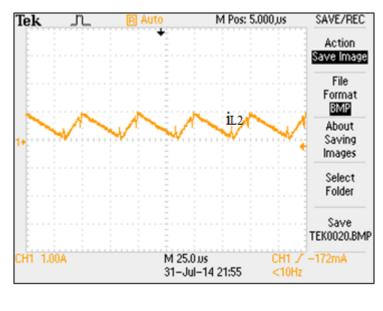

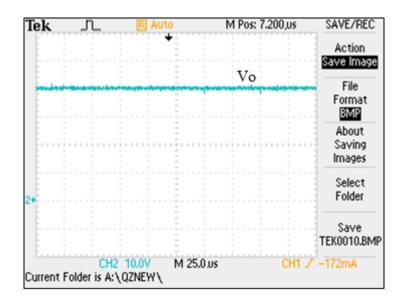

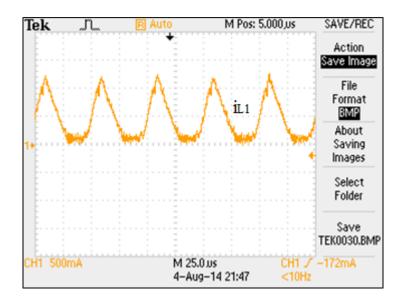

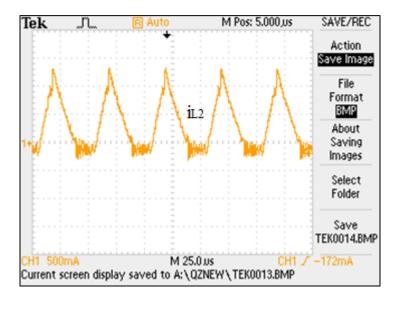

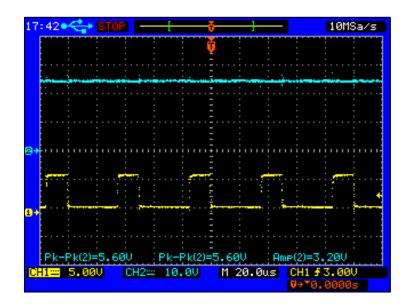

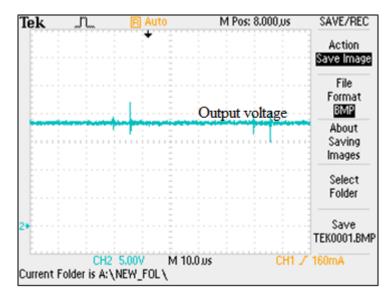

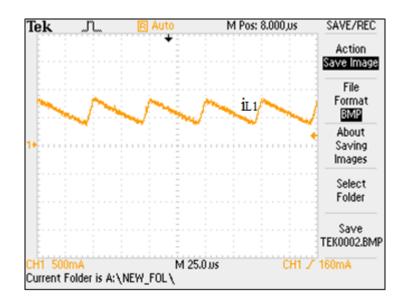

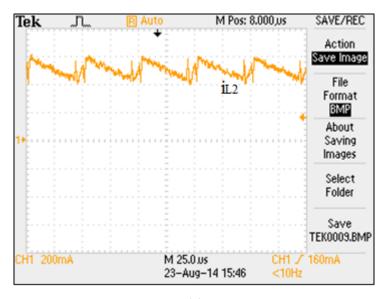

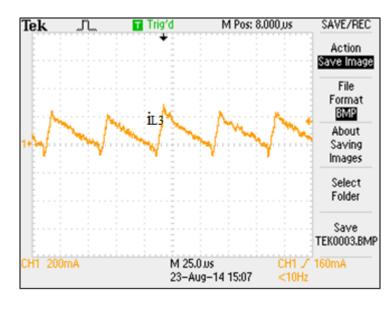

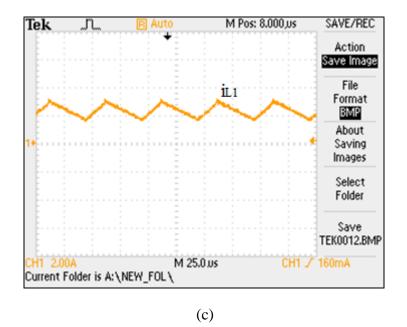

| 2.11    | : Experimental results in CCM for D=0.3 and $V_{in}$ =15V of (a) output voltage,      |

|         | (b) inductor current $i_{L1}$ and (c) $i_{L2}$                                        |

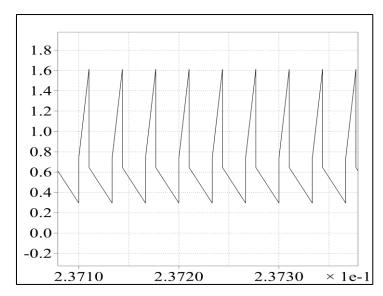

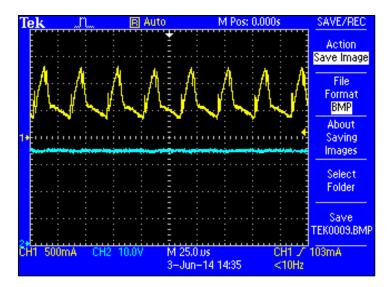

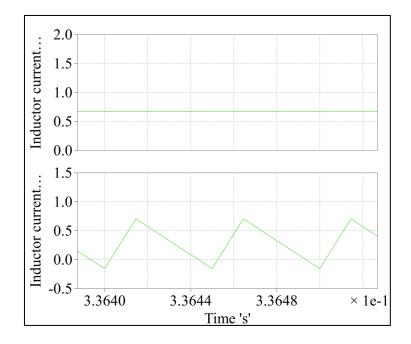

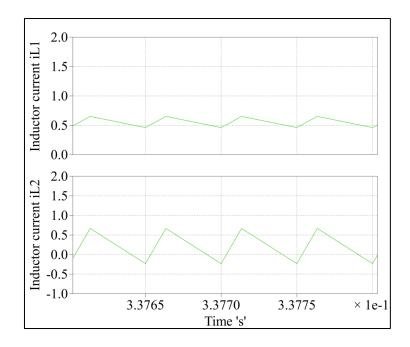

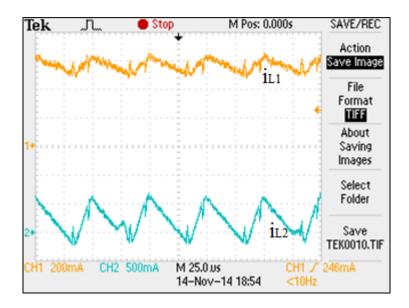

| 2.12    | : Simulation results in DCM for D=0.24 and $V_{in}$ =15V of output voltage,           |

|         | inductor current i <sub>L1</sub> and i <sub>L2</sub>                                  |

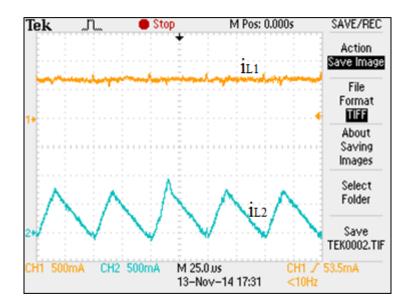

| 2.13    | : Experimental results in DCM for D=0.24 and $V_{in} {=} 15 V$ of (a) output voltage, |

|         | (b) inductor current $i_{L1}$ and (c) $i_{L2}$                                        |

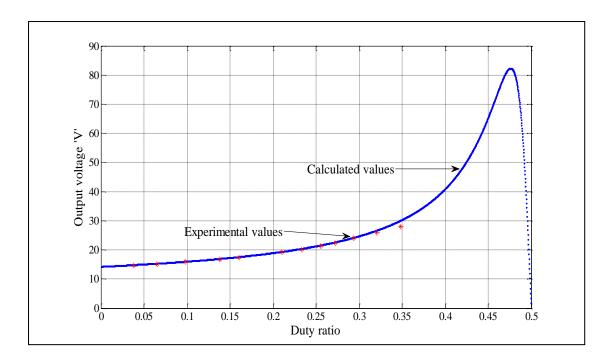

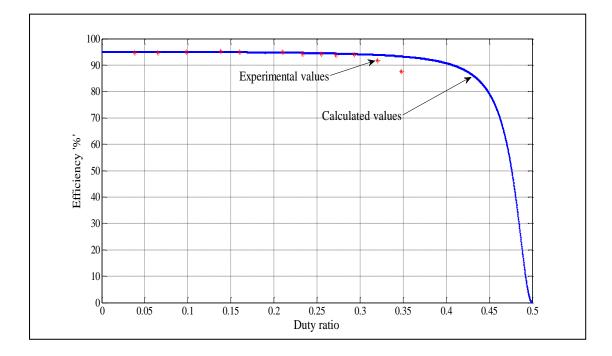

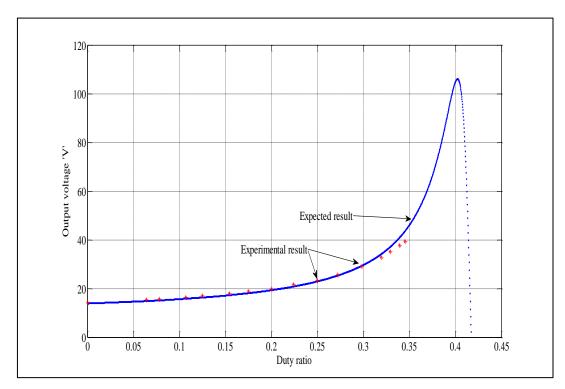

| 2.14(a) | : Output voltage $V_0$ as a function of D for $V_{in}$ = 15 V                         |

| 2.14(b) | : Efficiency as a function of D53                                                     |

| 2.15    | : PWM Z-source DC-DC converter                                                        |

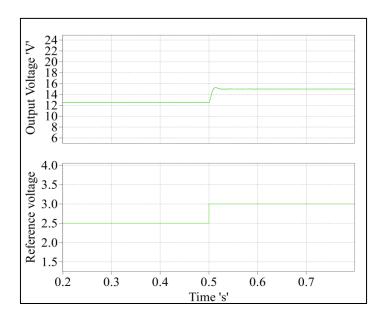

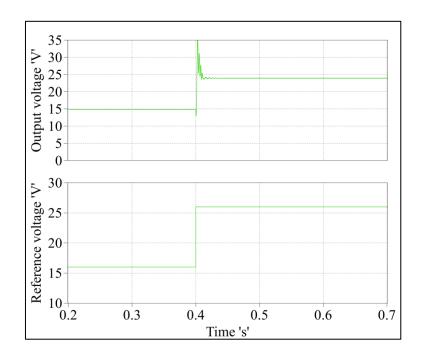

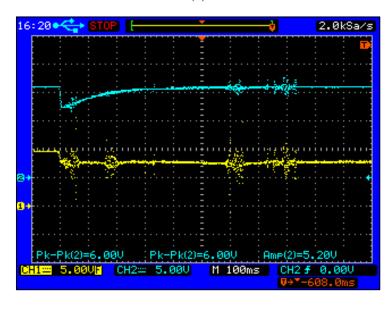

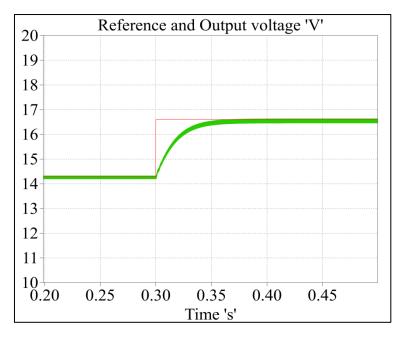

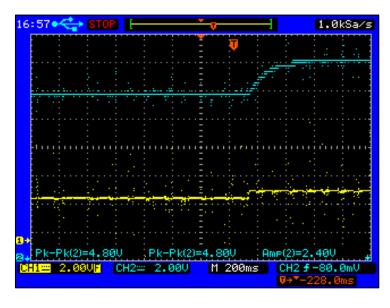

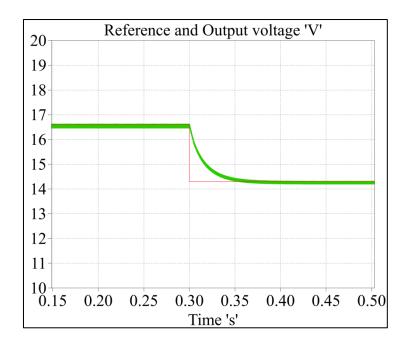

| 2.16(a) | : Simulation result for step change in reference                                      |

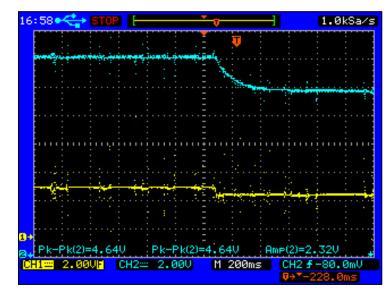

| 2.16(b) | : Experimental results for step change in reference                                   |

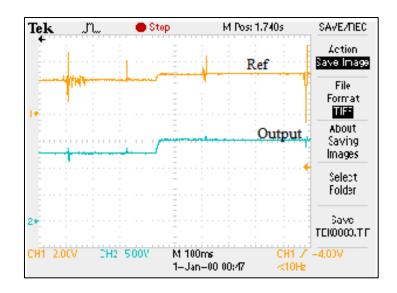

| 2.16(c) : Simulation result for step change in reference                             |

|--------------------------------------------------------------------------------------|

| 2.16(d) : Experimental results for step change in reference                          |

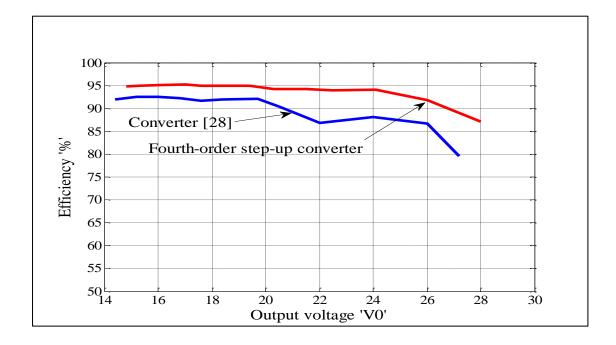

| 2.17 : Comparison of efficiency for different output voltage                         |

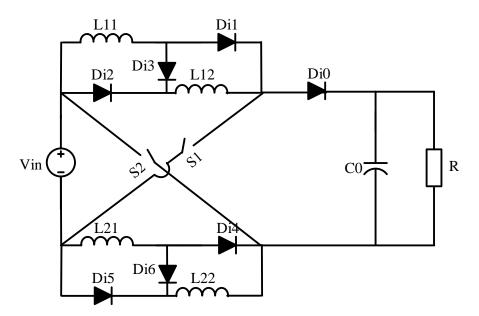

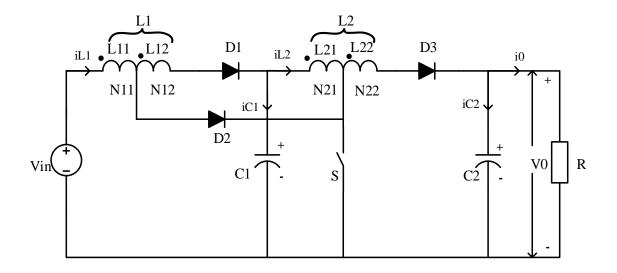

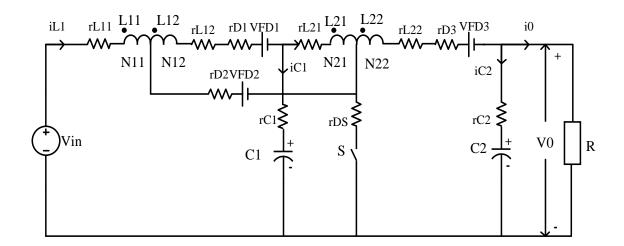

| 3.1.1 : Tapped-inductor QZS DC-DC Converter                                          |

| 3.1.2 : Equivalent circuit of converter for switch-ON duration                       |

| 3.1.3 : Equivalent circuit of converter for switch-OFF duration                      |

| 3.1.4(a) : Key current waveforms of converter                                        |

| 3.1.4(b) : Key voltage waveforms of converter                                        |

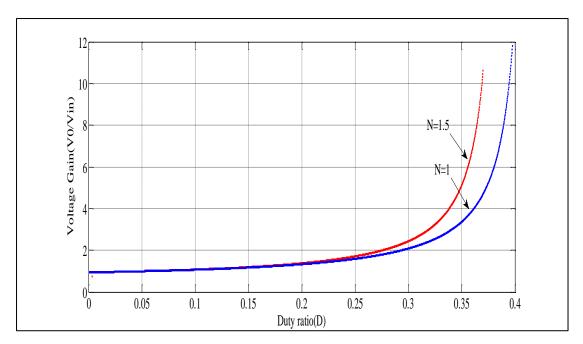

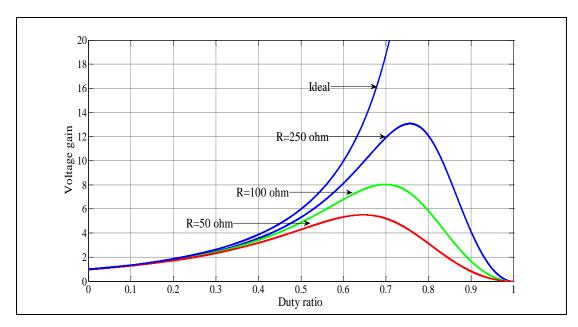

| 3.1.5 : Variation in voltage gain for different values of n                          |

| 3.1.6 : Equivalent circuit of converter with non-idealities                          |

| 3.1.7 : Gain of non-ideal converter for different values of n71                      |

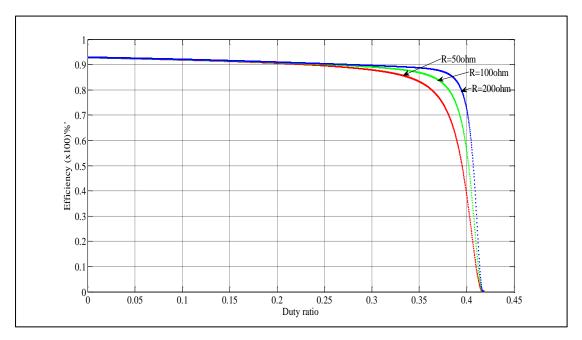

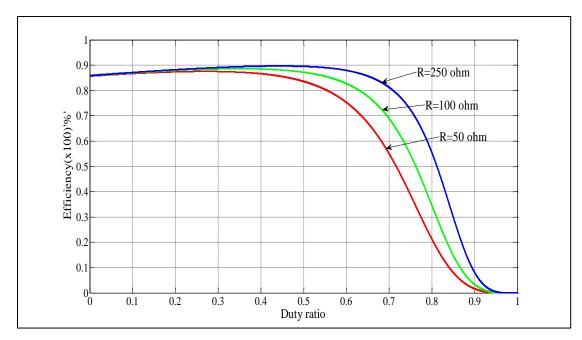

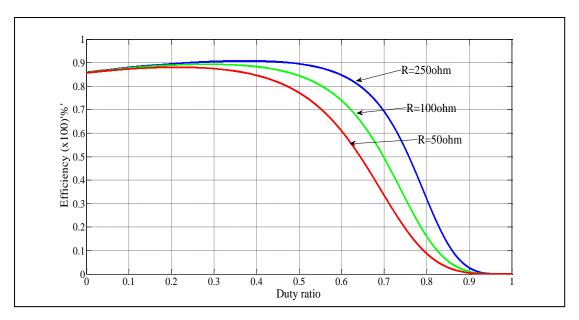

| 3.1.8 : Variation in efficiency with duty ratio for different loads                  |

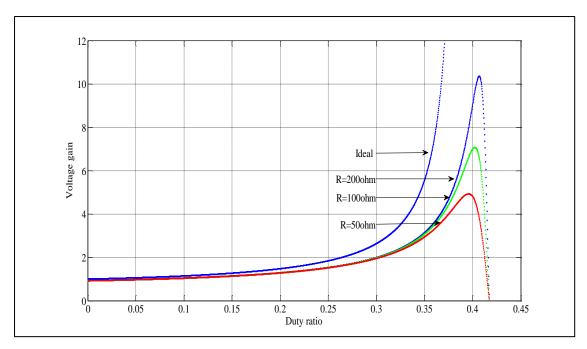

| 3.1.9 : Variation in gain with duty ratio for different loads                        |

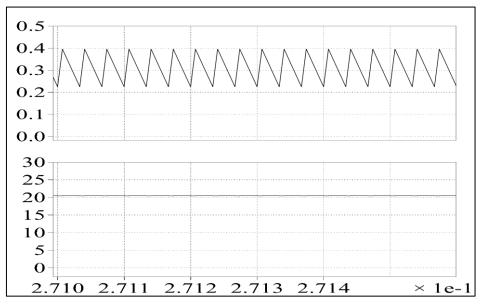

| 3.1.10(a): Simulation results of input current and output voltage for D=0.272        |

| 3.1.10(b): Simulation results of tapped-inductor current and for D=0.20              |

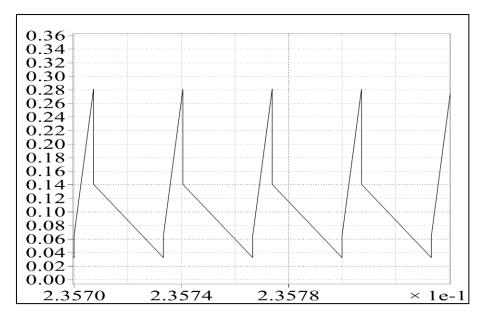

| 3.1.11(a): Experimental results of input current for D=0.2 and n =1                  |

| 3.1.11(b):Experimental results for tapped-inductor current for D=0.2 and n =174      |

| 3.1.12(a): Simulation results of input current and output voltage for D=0.3074       |

| 3.1.12(b):Simulation results of tapped-inductor current for D=0.3 and n =1.575       |

| 3.1.13(a): Experimental results of input current and output voltage for D=0.375      |

| 3.1.13(b): Experimental results of tapped-inductor current for D=0.3 and n = $1.576$ |

| 3.1.14 : Variation in output voltage with duty ratio for n =1                        |

| 3.1.15 : Variation in efficiency with duty ratio for $n = 1$                         |

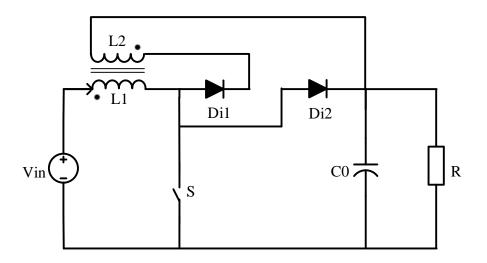

| 3.2.1 : Fourth-order step-up PWM DC-DC converter                                     |

| 3.2.2 : Inductor's voltage waveform                                                  |

| 3.2.3 : Coupled-inductor based step-up converter                                     |

| 3.2.4(a) : Equivalent circuit of converter for switch-ON                             |

| 3.2.4(b) : Equivalent circuit of converter for switch-OFF                            |

| 3.2.5 : Equivalent circuit of coupled inductor                                       |

| 3.2.6(a) : Simplified equivalent circuit of coupled inductor referred to primary86   |

| 3.2.6(b) : Simplified equivalent circuit of coupled inductor referred to             |

|                                                                                      |

| 3.2.7     | : Inductor's current waveforms in DCM                                     | 89  |

|-----------|---------------------------------------------------------------------------|-----|

| 3.2.8     | : Inductor's voltage waveform for DCM                                     | 89  |

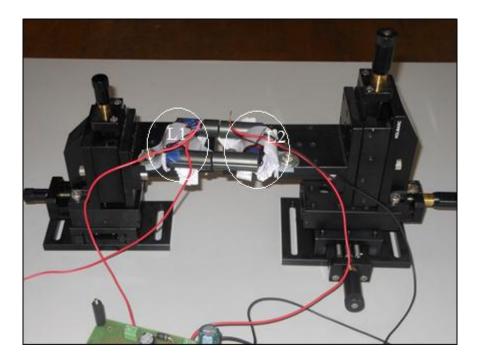

| 3.2.9     | : Experimental set-up for coupling coefficient adjustment                 | 90  |

| 3.2.10(a  | ): Simulation result of output voltage for D=0.29 and Vin=15V             | 91  |

| 3.2.10(b  | ): Experimental result of output voltage for D=0.29 and Vin=15V           | 92  |

| 3.2.11 (a | a): Simulation result for zero ripple input current                       | 92  |

| 3.2.11(b  | ): Experimental result for zero ripple input current                      | 93  |

| 3.2.12(a  | ): Simulation result for negative ripple input current                    | 93  |

| 3.2.12(b  | ): Experimental result for negative ripple input current                  | 94  |

| 3.2.13(a  | ): Simulation result for k <n<sub>2/N<sub>1</sub></n<sub>                 | 94  |

| 3.2.13(b  | ): Experimental result for k <n2 n1<="" td=""><td>95</td></n2>            | 95  |

| 3.2.14(a  | ):Simulation result for zero ripple condition in DCM                      | 95  |

| 3.2.14(b  | ): Experimental result for zero ripples condition in DCM                  | 96  |

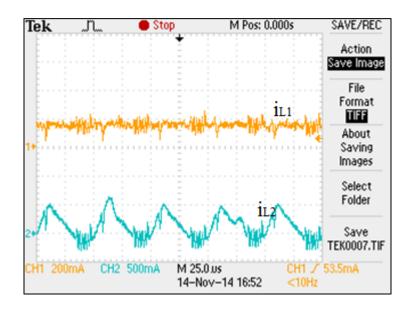

| 4.1       | : Typical block diagram of OCC                                            | 98  |

| 4.2 (a)   | : Z-source DC-DC converter                                                | 100 |

| 4.2(b)    | : Z-source DC-DC converter circuit when S is close                        | 101 |

| 4.2(c)    | : Z-source DC-DC converter circuit when S is open                         | 101 |

| 4.3       | : Z source converter with one cycle controller                            | 103 |

| 4.4(a)    | : Quasi Z-source DC-DC converter                                          | 104 |

| 4.4(b)    | : Quasi Z-source DC-DC converter when switch is closed                    | 104 |

| 4.4(c)    | : Quasi Z-source DC-DC converter when switch S is open                    | 105 |

| 4.5       | : Quasi Z source converter with one cycle controller                      | 106 |

| 4.6       | : One cycle control of fourth-order step-up DC-DC converter               | 107 |

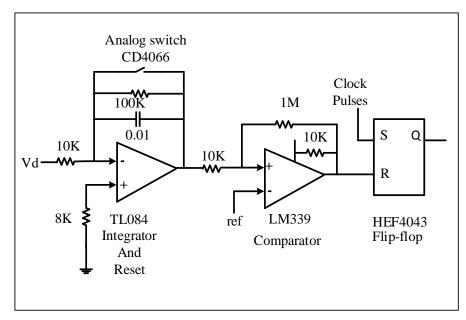

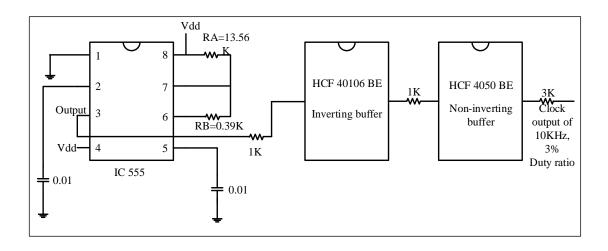

| 4.7 (a)   | : Core of One Cycle control circuit                                       | 109 |

| 4.7 (b)   | : Clock pulse generation circuit                                          | 109 |

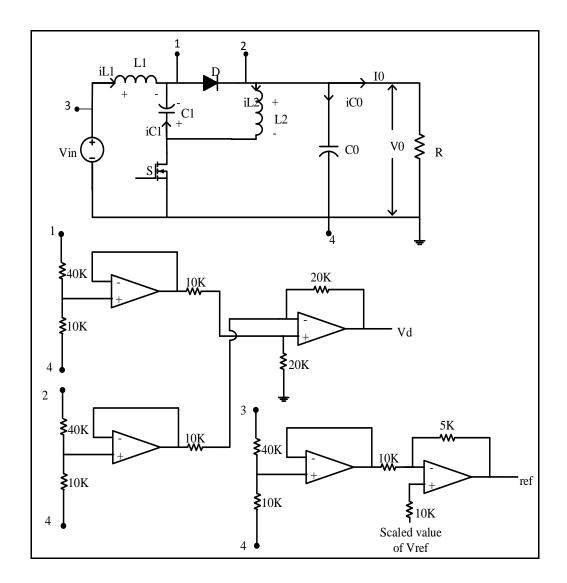

| 4.7 (c)   | : Diode voltage sensing and (V <sub>ref</sub> -V <sub>in</sub> ) circuit  | 110 |

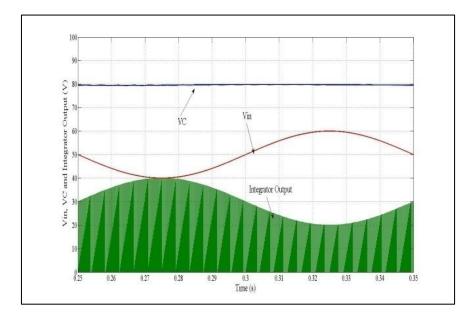

| 4.8       | : Response of capacitor voltage with Vin                                  | 111 |

| 4.9       | : Response of capacitor voltage with Vref                                 | 112 |

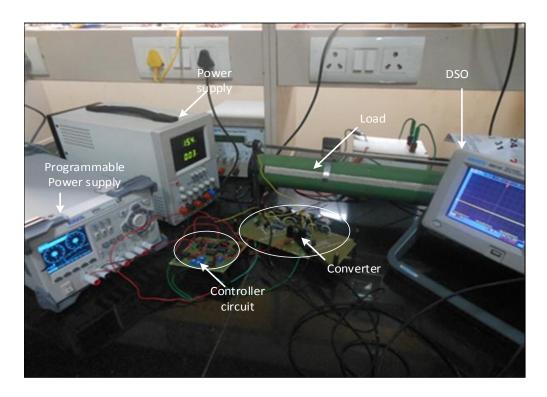

| 4.10      | : Experimental setup for One cycle control                                | 112 |

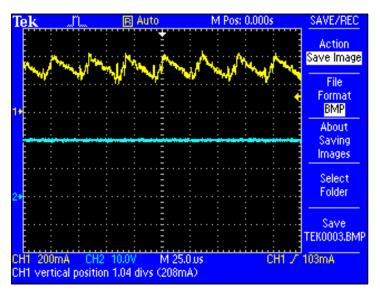

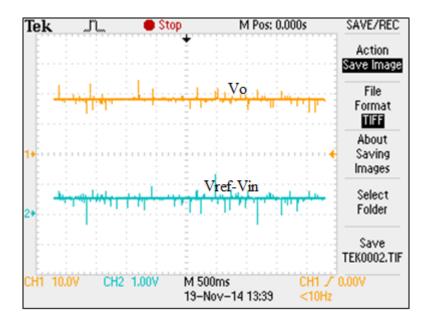

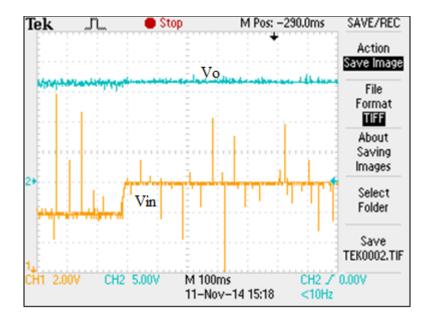

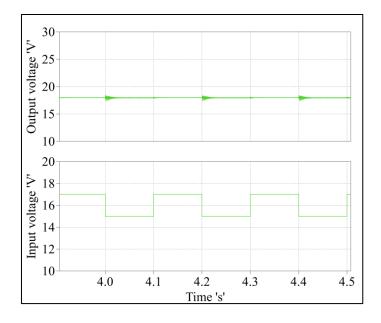

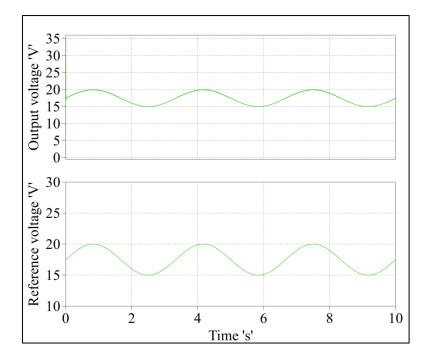

| 4.11(a)   | : Simulation result of output voltage with step change in $V_{\text{in}}$ | 113 |

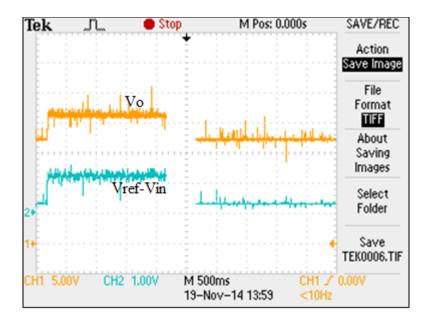

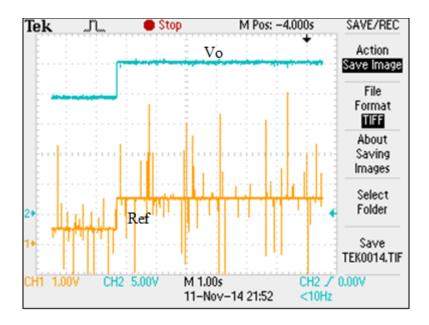

| 4.11(b)   | : Experimental result for step change in input.                           | 114 |

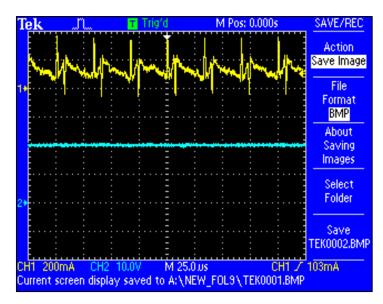

| 4.12(a) | : Response of output voltage with V <sub>ref</sub>                       | 114 |

|---------|--------------------------------------------------------------------------|-----|

| 4.12(b) | : Experimental result for step change in reference voltage               | 115 |

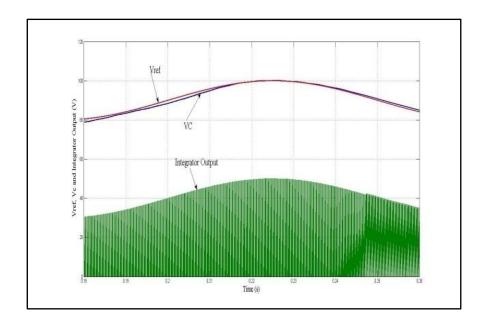

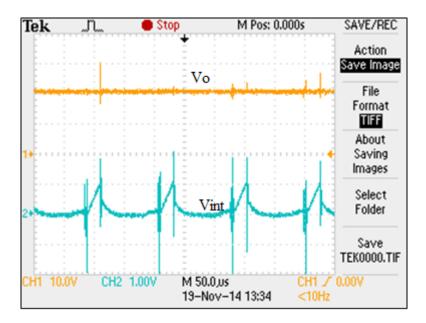

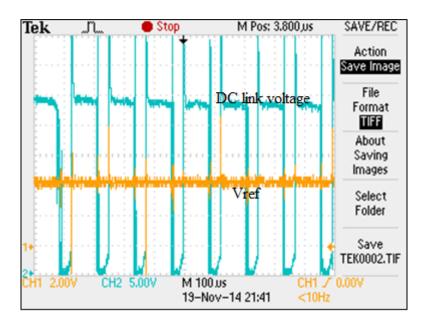

| 4.13(a) | : Output voltage and Integrator waveform                                 | 115 |

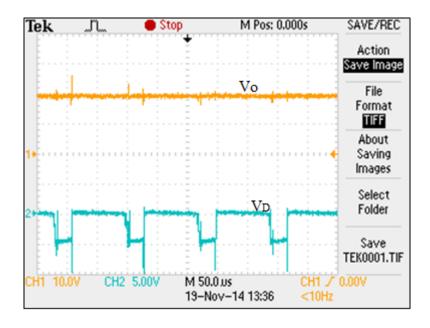

| 4.13(b) | : Voltage across diode and Output voltage                                | 116 |

| 4.13(c) | : Output voltage waveform                                                | 116 |

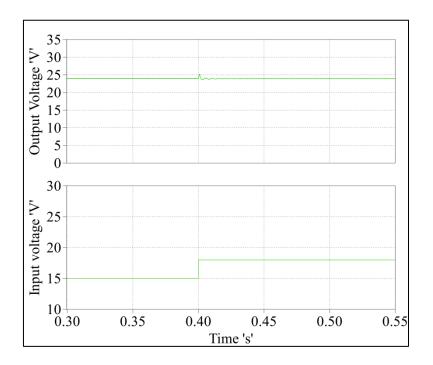

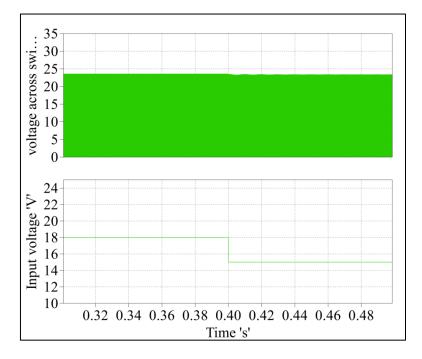

| 4.14(a) | : Response of DC-link voltage for step change in input voltage           | 117 |

| 4.14(b) | : Experimental result of DC-link voltage for given reference             | 117 |

| 4.15(a) | : Response to step change in input voltage                               | 118 |

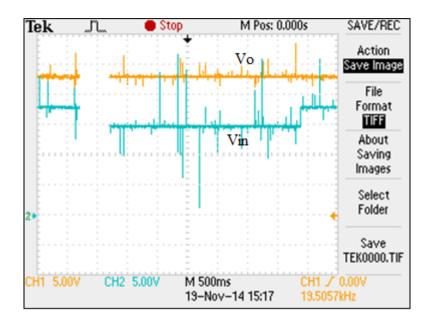

| 4.15(b) | : Experimental result for step change in input voltage                   | 119 |

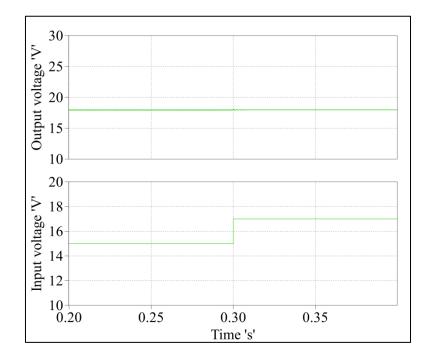

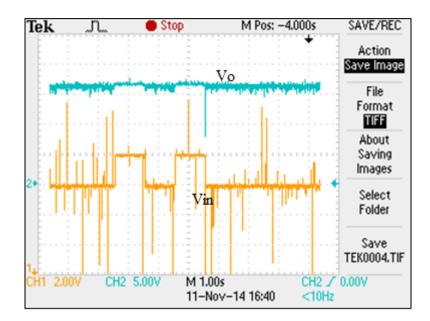

| 4.16(a) | : Simulation result for change in input voltage                          | 119 |

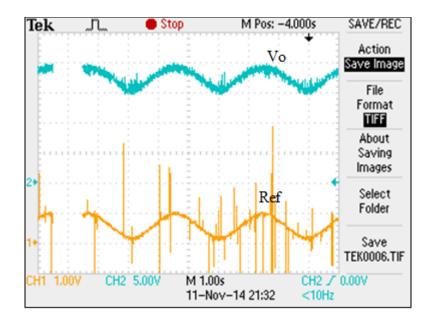

| 4.16(b) | : Experimental result for change in input voltage                        | 120 |

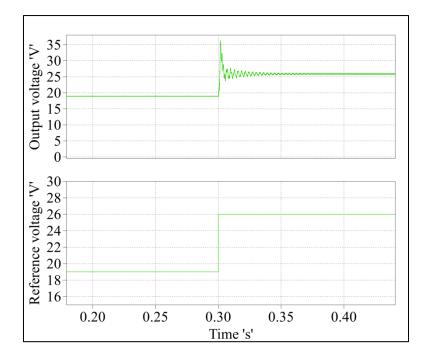

| 4.17(a) | : Simulation result for step change in reference voltage                 | 120 |

| 4.17(b) | : Experimental result for step change in reference voltage               | 121 |

| 4.18(a) | : Simulation result for continuous change in reference voltage           | 121 |

| 4.18(b) | : Experimental result for continuous change in reference voltage         | 122 |

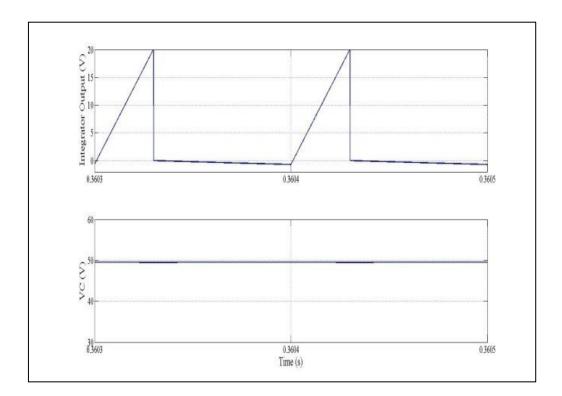

| 4.19    | : Integrator output and Capacitor voltage                                | 123 |

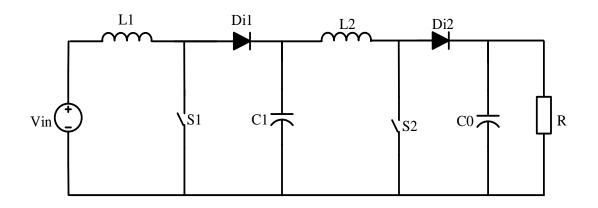

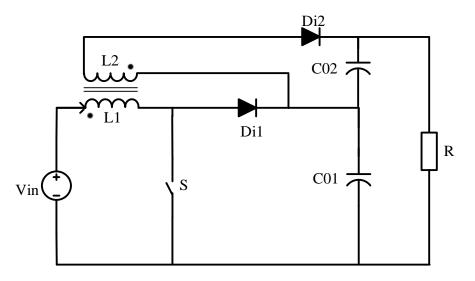

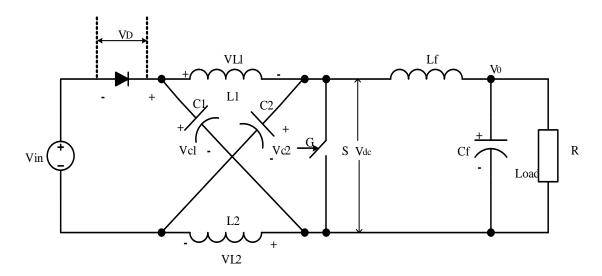

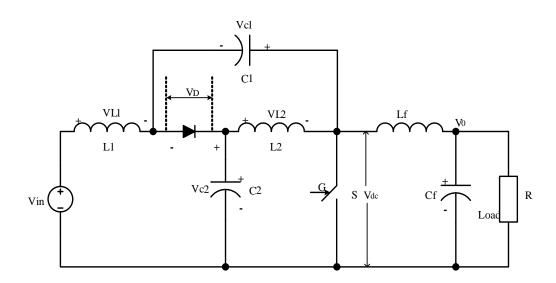

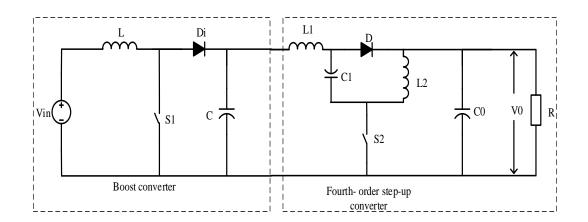

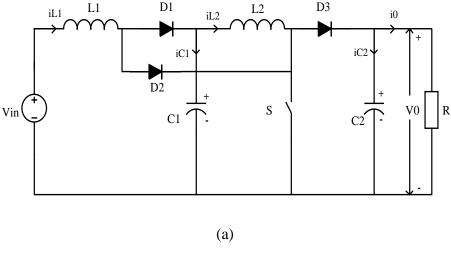

| 5.1     | : Cascade connection of boost and fourth-order step-up converter         | 125 |

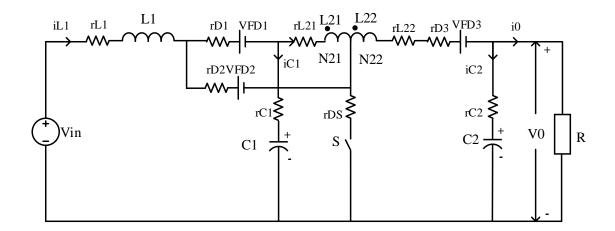

| 5.2     | : Proposed Converter                                                     | 126 |

| 5.3     | : Equivalent circuit of converter during switch-on                       | 127 |

| 5.4     | : Equivalent circuit of converter during switch-off                      | 127 |

| 5.5(a)  | : Nature of Current waveforms of proposed converter                      | 129 |

| 5.5(b)  | : Nature of Voltage waveforms of proposed converter                      | 130 |

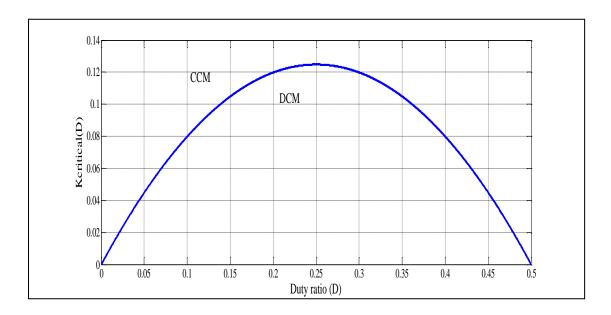

| 5.6     | : Variation of K <sub>c</sub> critical with Duty ratio D                 | 132 |

| 5.7     | : Equivalent circuit of converter with non-idealities                    | 133 |

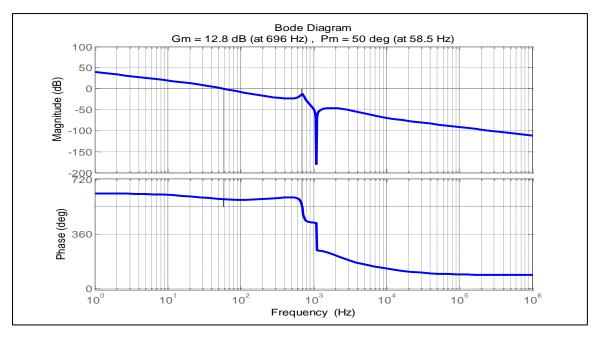

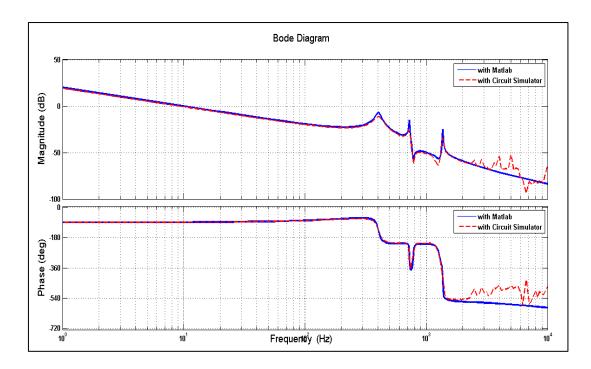

| 5.8(a)  | : Open loop control to output voltage frequency response                 | 141 |

| 5.8(b)  | : Compensated frequency response                                         | 142 |

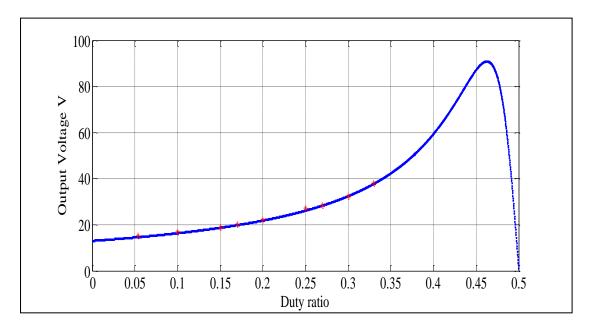

| 5.9(a)  | : Output voltage as a function of D for input voltage 15V                | 144 |

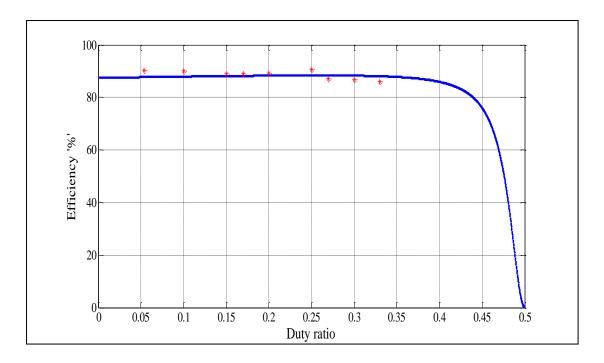

| 5.9(b)  | : Efficiency as a function of D                                          | 145 |

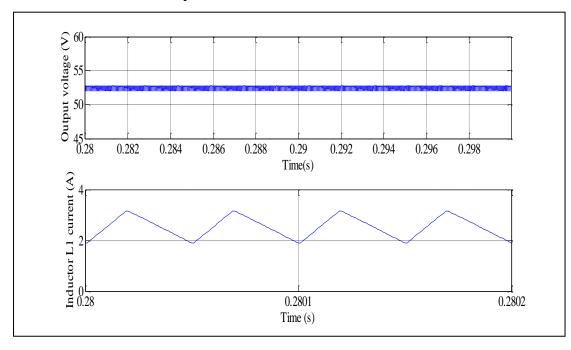

| 5.10    | :(a) Simulation results, (b) Simulation results of inductor current iL2  |     |

|         | and iL3 for D=0.126                                                      | 145 |

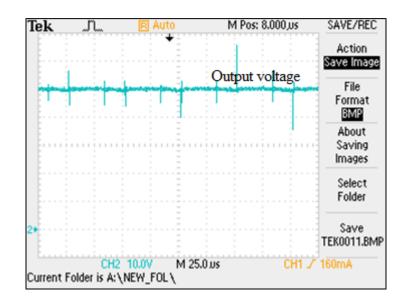

| 5.11    | : (a) Experimental output voltage (b) Inductor current IL1, (c) Inductor | •   |

|         | current IL2,(d)Inductor current IL3 for D=0.12614                             | 6          |

|---------|-------------------------------------------------------------------------------|------------|

| 5.12    | : (a) Simulation results, (b) Experimental output voltage, (c) Inductor L1    |            |

|         | current for D=0.3611                                                          | 48         |

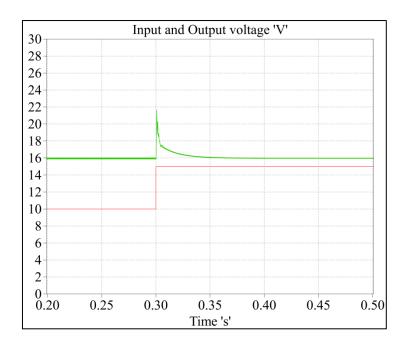

| 5.13    | : Controller response for step increase in input voltage, (a) Simulation resu | ılts,      |

|         | (b) Experimental results                                                      | 50         |

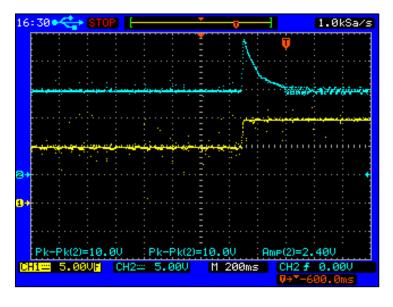

| 5.14    | : Controller response for step decrease in input voltage, (a) Simulation      |            |

|         | results, (b) Experimental results1                                            | 51         |

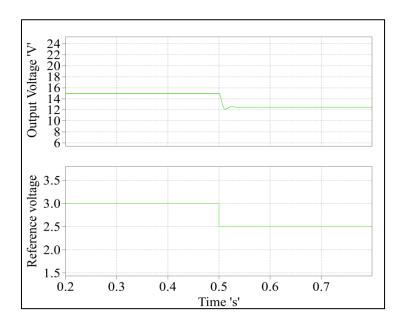

| 5.15    | : Controller response for step increase in reference voltage, (a) Simulation  |            |

|         | results, (b) Experimental results1                                            | .52        |

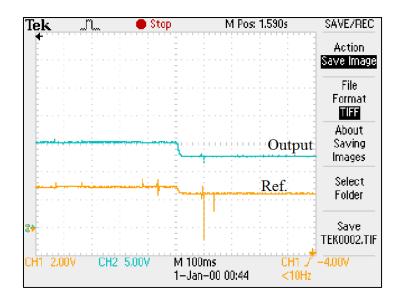

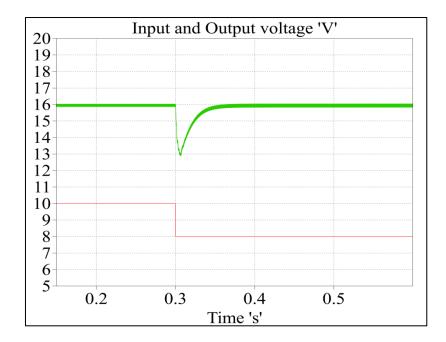

| 5.16    | : Controller response for step decrease in reference voltage, (a) Simulation  | 1          |

|         | results, (b) Experimental results1                                            | 53         |

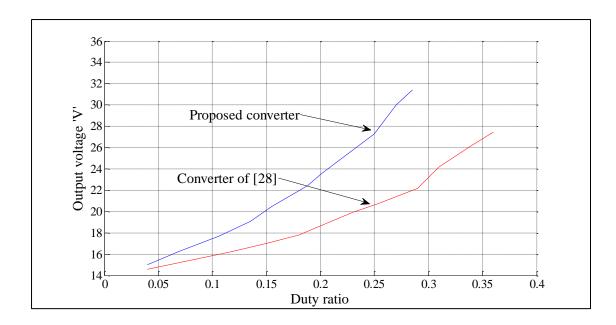

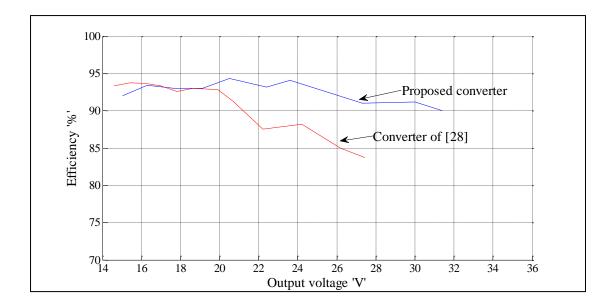

| 5.17(a) | : Comparison of output voltage against duty ratio1                            | 54         |

| 5.17(b) | : Converter's efficiency comparison for different output voltage1             | 54         |

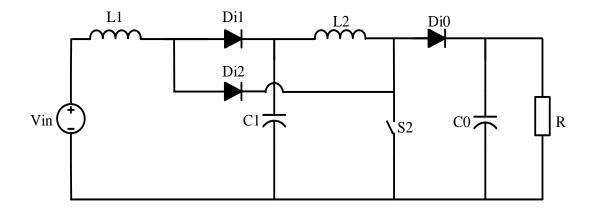

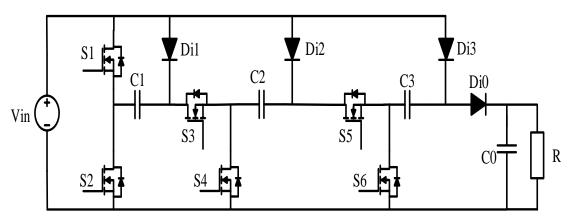

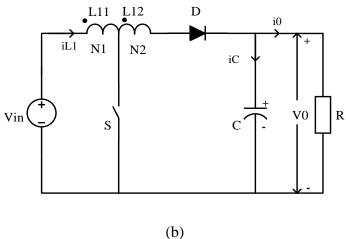

| 6.1     | : (a) Quadratic boost converter and (b) tapped boost converter1               | 58         |

| 6.2     | : (a) Semi-tapped quadratic boost converter and equivalent circuit (b) for    |            |

|         | switch-ON and (c) for switch-OFF1                                             | 59         |

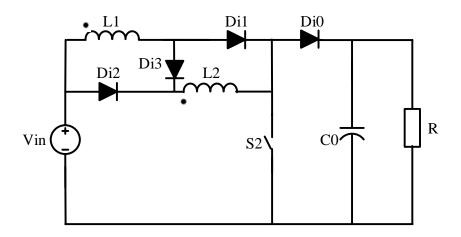

| 6.3     | : (a) Fully-tapped quadratic boost converter and equivalent circuits for      |            |

|         | (b)switch-ON, and (c) switch-OFF10                                            | 52         |

| 6.4     | : Quadratic boost converter with parasitic parameters10                       | 55         |

| 6.5     | : Voltage gain of quadratic boost converter with various loads16              | <b>5</b> 7 |

| 6.6     | : Efficiency of quadratic boost converter with various loads16                | i8         |

| 6.7     | : Semi-tapped quadratic boost converter with parasitic parameters1            | 69         |

| 6.8     | : Voltage gain of semi-tapped converter (n <sub>2</sub> =1)1                  | 70         |

| 6.9     | : Efficiency of semi-tapped converter (n <sub>2</sub> =1)1                    | 71         |

| 6.10    | : Fully Tapped-inductor quadratic boost converter with parasitic17            | 71         |

| 6.11    | : Voltage gain of fully-tapped converter $(n_1=n_2=1)$                        | 73         |

| 6.12    | : Efficiency of fully-tapped converter $(n_1=n_2=1)$ 1                        | 74         |

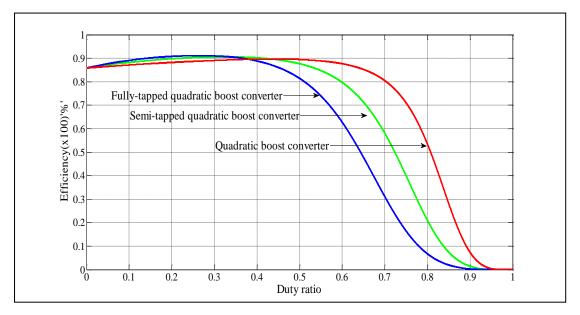

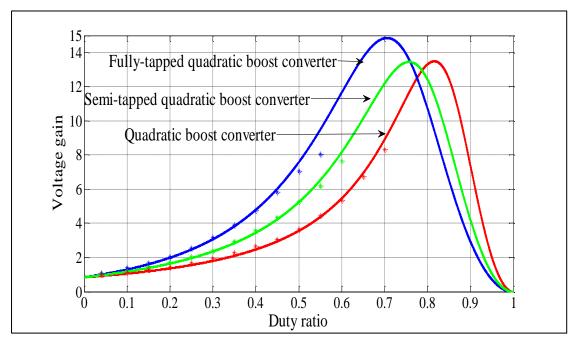

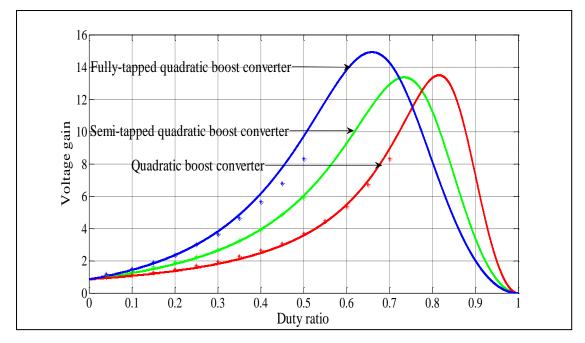

| 6.13(a) | : Comparison of efficiency for $n_1=n_2=1$ 1                                  | 75         |

| 6.13(b) | : Comparison of efficiency for $n_1=n_2=1.5$ 17                               | 75         |

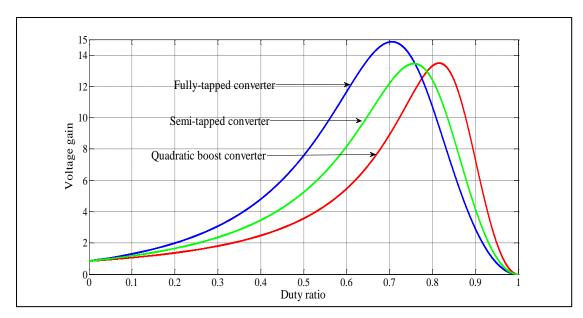

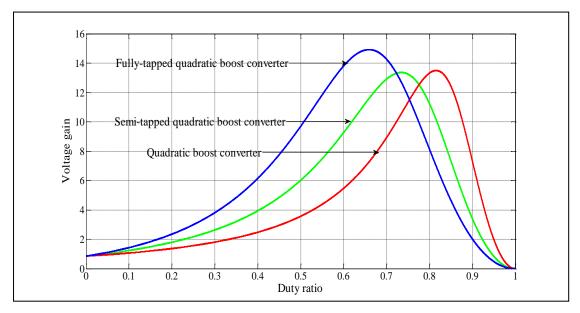

| 6.14(a) | : Comparison of Voltage gain for $n_1=n_2=1$ 1                                | 76         |

| 6.14(b) | : Comparison of Voltage gain for $n_1=n_2=1.51$                               | 76         |

|         |                                                                               |            |

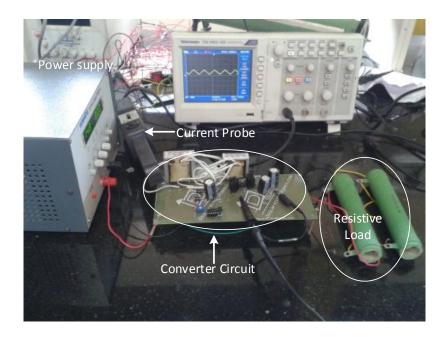

| 6.15     | : Experimental set-up1                                                                | .77 |

|----------|---------------------------------------------------------------------------------------|-----|

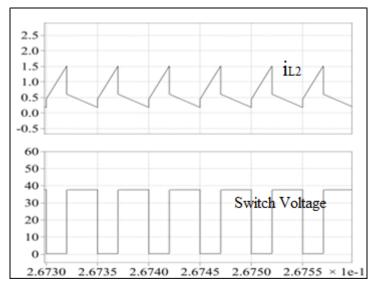

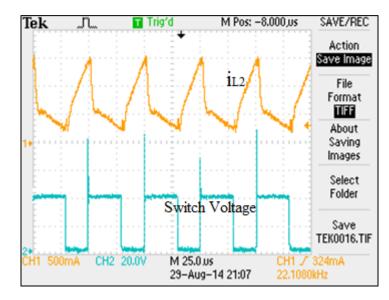

| 6.16     | : Semi-tapped converter for D=0.4 and $n_2$ =1.5 (a) simulation results for           |     |

|          | switch voltage and $i_{L2},$ (b) experimental results for switch voltage and $i_{L2}$ | ,   |

|          | and (c) experimental results for switch voltage and $i_{L1}$ 17                       | 78  |

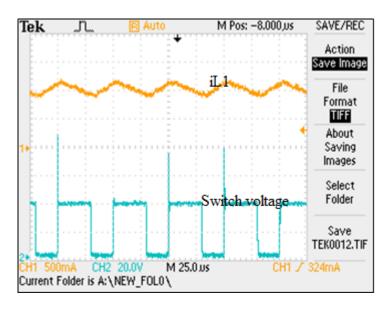

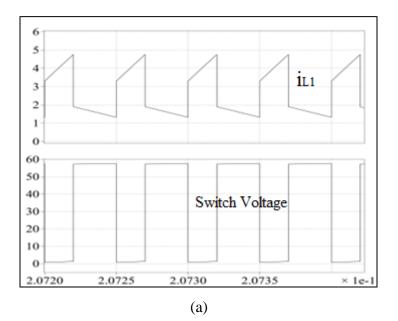

| 6.17     | : Fully-tapped converter for D=0.4 and for $n_1=n_2=1.5$ (a) simulation results       | 5   |

|          | of switch voltage and $i_{L1}$ , (b) experimental results of switch voltage           |     |

|          | and $i_{L1}$ ,and (c) experimental results of switch voltage and $i_{L2}$ 17          | 79  |

| 6.18(a)  | : Measured and calculated voltage gain for $n_1=n_2=1$ 1                              | 183 |

| 6.18(b)  | : Measured and calculated voltage gain for $n_1=n_2=1.51$                             | 83  |

| 6.19 (a) | : Calculated and measured voltage gain for $n_1=1$ and $n_2=1.51$                     | 84  |

| 6.19 (b) | : Voltage gain for $n_1=1.5$ and $n_2=1$                                              | 184 |

## LIST OF TABLES

| 2.1  | : Specifications of the converter                               | 49  |

|------|-----------------------------------------------------------------|-----|

| 2.2  | : Comparison between proposed converter and converter of [28]   | 56  |

| 3.1. | 1: Parameters used for analysis and simulation                  | 70  |

| 3.2. | 1: Details of converter's parameters                            | 91  |

| 5.1  | : Specification of laboratory prototype                         | 144 |

| 5.2  | : Comparison of proposed converter with converter of [28]       | 155 |

| 6.2  | : Parameters of converters                                      | 164 |

| 6.3  | : Comparison of voltage stress for active and passive switches  | 177 |

| 6.4  | : Measured values of voltage gain for quadratic boost converter | 181 |

| 6.5  | : Measured values for $n_1=n_2=1$                               |     |

| 6.6  | : Measured values for $n_1=n_2=1.5$                             |     |

## NOMENCLATURE

## Symbol- Definition

| •                              |                                             |

|--------------------------------|---------------------------------------------|

| $V_{in}$                       | - Input DC voltage                          |

| $\mathbf{V}_0$                 | -Output voltage                             |

| S                              | -Switch                                     |

| R                              | -Load resistance                            |

| F                              | -Switching frequency                        |

| $\mathbf{P}_0$                 | - Output power                              |

| $\eta$                         | - Efficiency                                |

| Ts                             | - Switching period                          |

| $V_{DC}$                       | - dc link voltage                           |

| $V_{C1}$                       | - quiescent voltage of C1 capacitor         |

| V <sub>C2</sub>                | - quiescent voltage of C2 capacitor         |

| V <sub>C1</sub>                | - C <sub>1</sub> capacitor voltage          |

| V <sub>C2</sub>                | - C <sub>2</sub> capacitor voltage          |

| $I_{L1}$                       | -quiescent value of L1 inductor current     |

| I <sub>L2</sub>                | -quiescent value of L2 inductor current     |

| $i_{L1}$                       | - L <sub>1</sub> inductor current           |

| $i_{L2}$                       | - L <sub>2</sub> inductor current           |

| $\Phi_1$                       | - quiescent value of flux through $L_1$     |

| $\Phi_2$                       | - quiescent value of flux through $L_2$     |

| n <sub>1</sub> ,n <sub>2</sub> | - turns ratio of $L_1$ and $L_2$            |

| k,k <sub>x</sub>               | - coupling coefficient                      |

| D                              | - quiescent value of duty ratio             |

| d                              | - average value of duty ratio               |

| $r_{L1}$                       | - resistance of inductor L <sub>1</sub>     |

| $r_{L2}$                       | - resistance of inductor L <sub>2</sub>     |

| $D_x$                          | - diodes                                    |

| $\phi_1$                       | - flux through inductor core L <sub>1</sub> |

| $\phi_2$                       | - flux through inductor core L <sub>2</sub> |

|                                |                                             |

| $L_1$           | - inductor 1                                    |

|-----------------|-------------------------------------------------|

| $L_2$           | - inductor 2                                    |

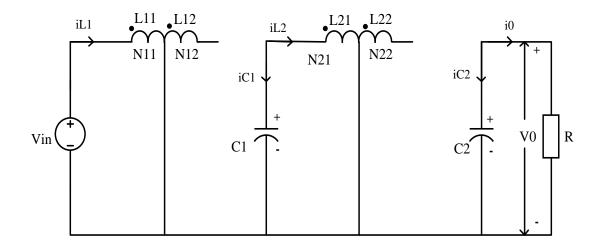

| L <sub>11</sub> | - first part of tapped inductor $L_1$           |

| L <sub>12</sub> | - second part of tapped inductor L <sub>1</sub> |

| L <sub>21</sub> | - first part of tapped inductor L <sub>2</sub>  |

| L <sub>22</sub> | - second part of tapped inductor L <sub>2</sub> |

| N <sub>11</sub> | - number of turns of $L_{11}$                   |

| N <sub>12</sub> | - number of turns of $L_{12}$                   |

| N <sub>21</sub> | - number of turns of L <sub>21</sub>            |

| N <sub>22</sub> | - number of turns of $L_{22}$                   |

| $r_{L11}$       | - resistance of inductor L <sub>11</sub>        |

| $r_{L12}$       | - resistance of inductor L <sub>12</sub>        |

| $r_{L21}$       | - resistance of inductor L <sub>21</sub>        |

| $r_{L22}$       | - resistance of inductor L <sub>22</sub>        |

| r <sub>C1</sub> | - resistance of C <sub>1</sub> capacitor        |

| r <sub>C2</sub> | - resistance of C <sub>2</sub> capacitor        |

| Ko              | - One cycle control constant                    |

| K <sub>C</sub>  | - constant in boundary condition                |

| $\hat{i}_x$     | - Small signal variation in current             |

| $\hat{v}_x$     | - Small signal variation in voltage             |

| $\hat{d}$       | - Small signal variation in duty ratio          |

| $\Delta v_x$    | - Voltage ripple                                |

| $\Delta i_x$    | - Current ripple                                |

| $\delta v_x$    | - Variation from average value of voltage       |

| $\delta i_x$    | - Variation from average value of current       |

| is              | - Switch current                                |

| $i_D$           | - Diode current                                 |

| $\widehat{v}_x$ | - Peak value of voltage                         |

| $\hat{i}_x$     | - Peak value of current                         |

|                 |                                                 |

M,M<sub>ideal</sub>- Ideal Gain

Mnonideal - Non-Ideal Gain

- Ploss Sum of losses

- P<sub>D</sub> Power loss in diode

- P<sub>S</sub> Power loss in switch

- P<sub>rlx</sub> Power loss in inductor

- P<sub>rcx</sub> Power loss in capacitor

- V<sub>SM</sub> Maximum value of voltage across switch

- $I_{XAV}$  Average value of current

- $V_{XAV}$  Average value of voltage

I<sub>R</sub> - Remaining current

- G<sub>vg</sub>(s) -Transfer function of output to input voltage

- $G_{ig}(s)$  Transfer function of input current to input voltage

- $G_{vd}(s)$  -Transfer function of output voltage to duty ratio

- $G_{ilxd}(s)$  -Transfer function of inductor current to duty ratio

- $C_X(s)$  -Transfer function of compensator

- $T_X(s)$  -Transfer function of loop

- V<sub>F</sub> Forward drop voltage of diode

- L<sub>f</sub> Filter inductor

- $C_{\rm f}$  Filter capacitor

- $\dot{i}_{Lx}$  Ripple current

## ACRONYMS

- ZS Z-Source

- ZSC Z-Source Converter

- ZSI Z-Source Inverter

- QZS Quasi Z-Source

- QZSI Quasi Z-Source Inverter

- OCC One Cycle Control

- CCM Continuous Conduction Mode

- DCM Discontinuous Conduction Mode

- PWM Pulse Width Modulation

- RHP Right Hand Plane

- EMI Electro Magnetic Interference

### **Chapter 1**

### Introduction and literature review

### **1.1 Introduction**

DC-DC converters with high voltage conversion ratio are now having increasing demand because of its applications in photovoltaic (PV) power generation systems, fuel cell based energy conversion systems, uninterrupted power supplies (UPS), high-intensity-discharge headlamps of automobiles and battery powered equipment.

Commercial PV module presents normally maximum power point power is lower than 300W and maximum power point voltage range from 15V-50V [1]. PV modules are connected in series and parallel to increase voltage and power level. However, a common problem in this arrangement is generation reduction due to partial shading of series connected PV modules [2]. Fuel-cells have been considered as excellent candidate to replace conventional fossil fuel in vehicles and emergency energy sources. Fuel-cells stack can provide voltage in the range of 40V-80V [3]. In order to use PV modules and fuel-cells for AC load or utility, it is required to process available energy to convert in suitable form as shown in Fig. 1. Front-end stage circuits of these applications need high step up converters to increase the source's voltage to the level required by the application and to produce a stable output voltage despite variations on the source voltage. Second stage of this process requires DC-AC converter. High intensity discharge lamp ballasts for automobile head lamps needs high step-up converters to boost 12V from battery to almost 100V at steady operation [4], [5].

Conventionally, boost converter or buck-boost converter with high duty ratio can be used for such applications. However, in practical implementation, the extreme high duty ratio operation may result in serious reverse-recovery problem, low efficiency and electromagnetic interference (EMI) problem [6]. Therefore many step-up topologies are reported in literature for high step-up operations. The main motive behind these topologies is to get higher boost with lower duty ratio and to reduce losses for a given power.

Following section reviews some of the basic non-isolated and isolated topologies of high step-up converters reported in literature.

Fig.1.1: Applications of high step-up DC-DC converters (a) PV power generation system, (b) Fuel-cell power generation system and (c) HID lamp ballast.

### **1.2 Review of step-up DC-DC converters**

In step-up applications, high step-up DC-DC converters are required as an integral interface between low voltage sources and the output loads, which operates at higher voltages. In literature, many researchers concentrate on how to realize high step-up converter to satisfy the requirement of above mentioned applications. This section gives an overview on available high step-up converters. The converter topologies reported in literature are mainly classified in isolated and non-isolated configurations of converters. Further, converters are grouped according to technique used for obtaining high conversion ratio.

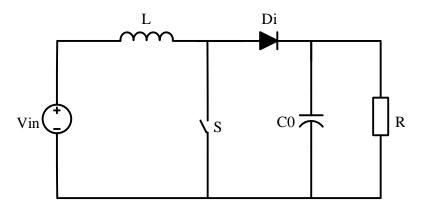

#### 1.2.1.1 Boost converter

The conventional single switch boost converter is shown in Fig. 1.2. Theoretically voltage gain of boost converter can be infinite when duty ratio approaches to one. However, the switch turn-off becomes short when duty ratio increases. At high duty ratio switch power loss increases and current ripples are large. This converter also suffers reverse recovery and electromagnetic interference at high duty ratio [7]. The voltage gain of boost converter can be given by

$$\frac{V_0}{V_{in}} = \frac{1}{1 - D}$$

(1.1)

Where  $V_0$  - output voltage,  $V_{in}$  - input voltage and D is duty ratio. The duty ratio can be defined as the ratio of switch ON time to sum of switch ON and switch OFF time.

Fig. 1.2: Boost converter.

#### 1.2.1.2 Interleaved boost converters

The interleaved boost converter shares the input current and reduces the current ripple. Input current ripple reduction is desirable feature for fuel cell and PV energy sources. Figure 1.3(a) shows a two phase conventional interleaved boost converter. The efficiency is limited and output diode reverse recovery problem is still serious for high output voltage applications. Interleaved boost converter voltage gain can be improved by using couple inductor in place of uncoupled inductors as shown in Fig. 1.3(b) [8].

Fig. 1.3(a): Interleaved boost converter.

Fig. 1.3(b): Coupled-inductor interleaved boost converter.

### 1.2.1.3 Three level boost converter

The conventional three level boost converter is as shown in Fig. 1.4. This converter can double the voltage gain and can reduce voltage stress of the power device in comparison with the conventional boost converter, these features makes it more suitable for low–voltage-input high voltage output applications. Due to lower voltage stress on power device, MOSFETs with lower switch-ON resistance can be used to reduce the converter cost and the conduction losses. However output diode reverse recovery problem is severe.

Fig. 1.4: Three level boost converter.

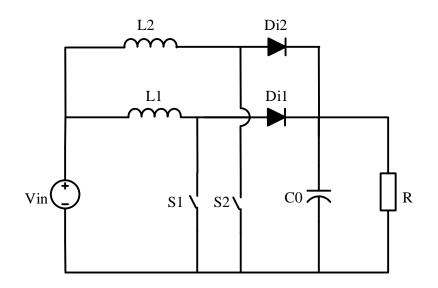

### 1.2.1.4 Cascaded boost converter

The voltage gain of three level boost converter is still not large enough for high stepup applications. The voltage gain can be increased to satisfy the requirements by using cascade structure as shown in Fig. 1.5(a). In this topology, the voltage stress of the first stage is low and it can be switched with high switching frequency to improve the power density. The second stage can be switched with lower switching frequency to reduce the switching losses. However, this topology requires two sets of switching circuits, control circuits and power devices, which makes it complex and expensive. The two switch of cascaded boost converter can be integrated to reduce complexity of this topology as shown in Fig. 1.5(b) [9]. The voltage gain of this configuration can be given by

$$\frac{V_0}{V_{in}} = \frac{1}{\left(1 - D\right)^2}$$

(1.2)

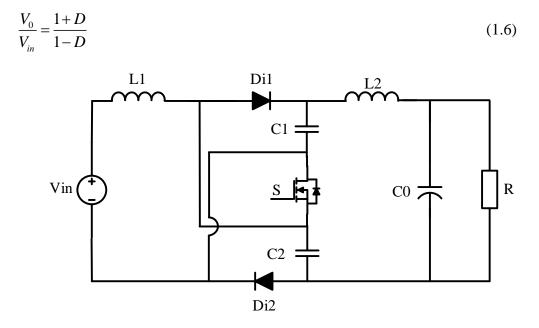

1.2.1.5 Switched inductor based converters

Figure 1.6(a) shows the switched inductor based boost converter [10]. The voltage gain of this configuration can be given by

$$\frac{V_0}{V_{in}} = \frac{1+D}{1-D}$$

(1.3)

Fig. 1.5(a): Cascaded boost converter.

Fig. 1.5(b): Quadratic boost converter.

Voltage gain of this converter is higher than conventional boost converter but not much suitable for high voltage gain applications. Switch voltage stress is also high in this converter. Figure 1.6(b) shows another example of switched inductor based converter [10], and the voltage gain of this converter can be given by

$$\frac{V_0}{V_{in}} = \frac{1+3D}{1-D}$$

(1.4)

### 1.2.1.6 Coupled inductor based converters

A coupled inductor can serve as a transformer that is used to enhance the voltage gain in non-isolated step-up converters [11].

Fig. 1.6(a): Switched-inductor boost converter.

Fig. 1.6(b): Switched-inductor with active network circuit converter.

Figure 1.7(a) shows a coupled inductor based high step-up converter. The voltage gain of coupled inductor based converter can be extended by proper design of turns ratio. A high step-up flyback-boost converter is derived by combining the conventional boost with flyback converter. Figure 1.7(b) shows coupled inductor based flyback-boost converter. The voltage gain of ideal converter for this configuration can be given by

$$\frac{V_0}{V_{in}} = \frac{1+nD}{1-D}$$

(1.5)

Fig. 1.7(a): Coupled-inductor high step-up converter.

Where **n** is turns ratio. In literature many variations are reported based upon combination of flyback and boost converter [12]. The advantages of coupled inductor based topologies are high gain and reduction in size of converter due to common magnetic core. The converters reported in [13], [14], [15] and [16] also uses coupled inductors to achieve high step-up ratio. However, the leakage energy induces high voltage stress and increased switching losses and also create EMI problem. An active clamp circuit can be used to minimize these problems in coupled inductor based converters.

Fig. 1.7(b): High step-up flyback-boost converter using coupled inductor.

#### 1.2.1.7 Switched capacitor based converters

Converters based upon switched capacitors can give high voltage gain depending upon number of capacitors used [17]. Figure 1.8(a) shows switched capacitor high step-up converter.

Fig. 1.8(a): High step-up converter with switched capacitor.

Fig. 1.8(b): High step-up converter with multilevel cell.

Another variation of switched capacitor converter is hybrid switched capacitor converter as shown in Fig. 1.8(b), which uses capacitor diode multiplier cell to increase reliability and efficiency of the converter. The converters reported in [18], [19] and [20] also used switched capacitors for high voltage gain.

The converters based upon switched capacitor do not require magnetic components such as inductors and transformers due to which size, cost and weight of converter is reduced. However, number of switches is high, which increases converter complexity and cost. The main disadvantages of switched capacitor based converters are (i) pulsating input current, (ii) voltage regulation is poor and difficult and (iii) the voltage gain is usually predetermined by the converter structure.

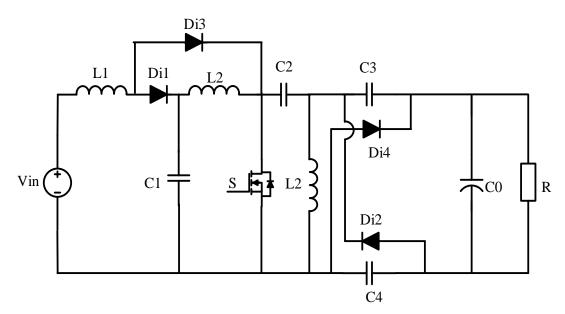

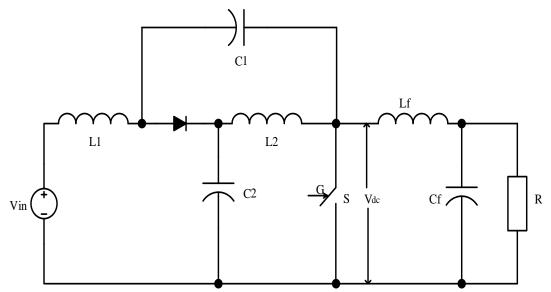

#### 1.2.1.8 Switched capacitor and inductor based converters

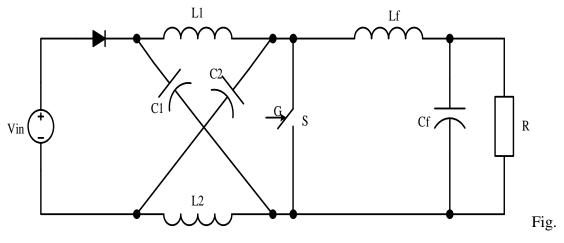

The switched capacitor based converter can be integrate with boost converter to get step less voltage gain [21]. Figure 1.9(a) shows an example of this type of converter. This converter can provide high gain with lower duty ratio but it suffers from pulsating output current. Another family of single switch high step-up dc-dc converter is introduced in [22], Fig. 1.9(b) shows an example of this family. The voltage gain of converter shown in Fig. 1.9(b) is given by

Fig. 1.9(a): High step-up converter presented in [21].

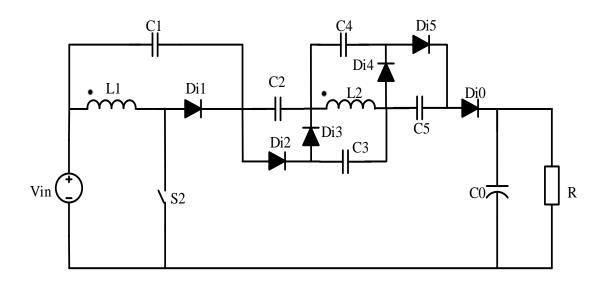

### 1.2.1.9 Coupled inductor and switched capacitor based converter

The concept of coupled inductor and switched capacitor can be integrate to derive high voltage gain converters [23]. Figure 1.10(a) shows an example of such combination of converter [24]. The reverse recovery problem of output diode is alleviated by leakage inductance of coupled inductor.

Fig. 1.9(b): High step-up converter presented in [22].

The voltage gain of converter shown in Fig. 1.10(a) can be given for coupling coefficient equal to one by

$$\frac{V_0}{V_{in}} = \frac{1+2n+nD}{1-D}$$

(1.7)

Fig. 1.10(a): High step-up converter presented in [24].

Another example of this combination is as shown in Fig. 1.10(b) [25] and the voltage gain of this configuration can be given by

$$\frac{V_0}{V_{in}} = \frac{1 + (1 + D)n}{1 - D}$$

(1.8)

The main features of this converter are (i) large step-up conversion ratio, (ii) less voltage stress on switch and (iii) recycling of leakage energy of coupled inductor.

Fig. 1.10(b): High step-up converter presented in [25].

## 1.2.1.10 Z-source (ZS)/quasi Z-source (QZS) based converters

Z-source converter is comparatively new topology [26]. The Z-source based converters can be used for high step-up applications [3], [27]. Figure 1.11(a) shows Z-source based PWM DC-DC converter [28]. The voltage gain of the converter shown in Fig. 1.11(a) is given by

$$\frac{V_0}{V_{in}} = \frac{1 - D}{1 - 2D} \tag{1.9}$$

Compared to conventional boost converter, the PWM Z-source converter has desirable features for high step-up applications such as (i) higher voltage gain for

1.11(a): Z-source DC-DC converter.

same duty ratio, (ii) it isolates source from load in case of a short circuit at load side. Limitations of this converter are discontinuous input current and floating switch.

The QZS converter has been proposed as a new converter topology based on Zsource inverter topology. Figure 1.11(b) shows QZS based DC-DC converter [29], which inherits all the advantages of ZSC and has several more advantages such as reduced passive component rating and common ground for source load and switch. The voltage gain of this converter is same as ZS based converter [28], as given by (1.9).

Fig. 1.11(b): Quasi Z-source DC-DC converter.

#### 1.2.2 Isolated converter topologies

In some countries galvanic isolation of PV energy source is necessary as per their electrical regulations and standards. In view of their requirement many isolated topologies are reported in literature [30]. The electrical isolation can be provided by transformer either at line frequency or at high frequency. Transformer at line frequency is not often used because of its size, weight and high price.

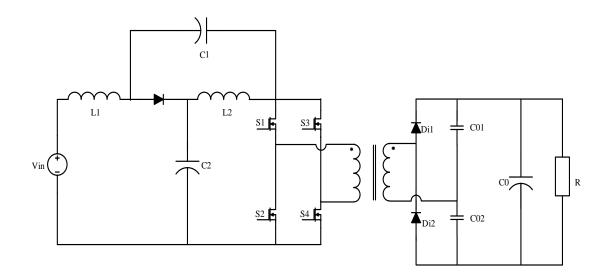

## 1.2.2.1 Basic isolated step-up converter topologies

A number of isolated step-up converter configurations are known, and some of these are briefly given here. Figure 1.12(a) shows full-bridge topology of isolated step-up converter. In this configuration voltage gain is transformation ratio times of boost converter as given by equation (1.10), and when turn ratio is one voltage gain is same as boost converter.

Fig. 1.12(a): Full-bridge isolated step-up converter.

$$\frac{V_0}{V_{in}} = \frac{n}{1 - D}$$

(1.10)

An isolated converter based on push-pull configuration is depicted in Fig. 1.12(b) [31]. In comparison with isolated full bridge boost topology it requires only two active switches. However the voltage rating of switches are higher than isolated full bridge boost topology. Operation is otherwise similar to isolated full bridge boost converter.

Figure 1.12(c) shows active clamp step-up DC-DC converter. This isolated converter configuration has the advantages of both flyback and forward converter. This topology uses active clamp circuit in both duration of switching operation so the input power is delivered to output in both switch-ON and switch-OFF duration.

Fig. 1.12(b): Isolated step-up converter based on push-pull configuration.

Fig. 1.12(c): Active clamp isolated step-up converter.

In this configuration voltage doubler circuit is used with secondary side of transformer. In primary side capacitors are used in parallel with diode to eliminate reverse recovery losses of diode.

The voltage gain of this configuration can be given as

$$\frac{V_0}{V_{in}} = \frac{2nD}{1-D}$$

(1.11)

## 1.2.2.2 Isolated resonant converters

Resonant soft-switching techniques can be incorporate with converters to achieve higher efficiency operation. In these converters only conduction losses are dominates as switching losses are negligible.

Figure 1.13(a) shows half bridge resonant converter [32]. The zero current switch (ZCS) condition is achieved by connecting appropriate value of capacitor Cr in series with transformer to form resonant tank with transformer leakage inductance.

The zero voltage switch (ZVS) condition based converter [33] is shown in Fig. 1.13(b). During switch-OFF capacitor C1 and C2 resonates with inductor Lr thus zero voltage switch-OFF is achieved. Switch-ON occurs when voltage across capacitor is zero.

In literature many other soft-switching based isolated converter configurations such as resonant push-pull converter [34], current fed multi-resonant converter [35] and series parallel resonant converters [36] are also reported for high step-up operation.

Fig. 1.13(a): Half-bridge resonant converter.

Fig. 1.13(b): Resonant half-bridge dual converter.

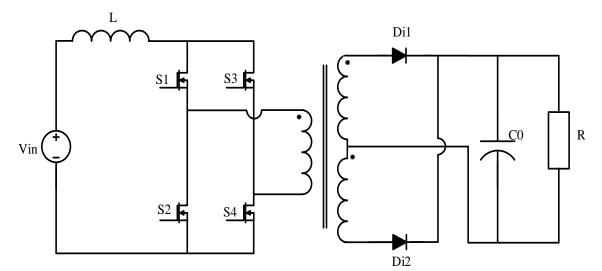

## 1.2.2.3 Z-source/quasi Z-source based isolated converters

Z-source based another topology was proposed in [37], which utilized coupled inductor for higher boost and load is isolated from the source. Figure 1.14(a) shows isolated DC-DC converter based upon Z-source topology. The voltage gain of this configuration can be given as

$$\frac{V_0}{V_{in}} = 2nk \frac{1-D}{1-2D}$$

(1.12)

Where  $\mathbf{n}$  is turns ratio and  $\mathbf{k}$  is coupling coefficient.

Fig. 1.14(a): Z-source isolated DC-DC converter.

The main features of this converter are (i) low turns ratio of coupled inductor, (ii) the leakage inductor energy does not create voltage stress over active switch or diode, (iii) switch voltage rating is low and (iv) isolation exists between input and output. The main limitation of this topology is the reverse recovery problem, which is alleviated due to secondary leakage inductance.

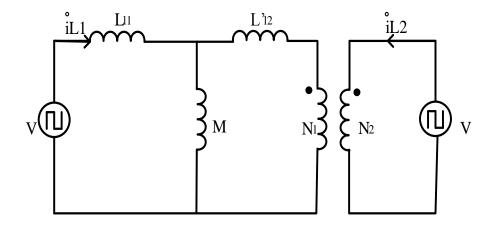

In [38] QZS based isolated DC-DC converter was proposed, which is similar to ZSC based isolated DC-DC converter. Figure 1.14(b) shows circuit of QZS based isolated DC-DC converter, it also utilize coupled inductors for isolation and to obtain high gain. The voltage gain of the converter shown in Fig. 1.14(b) can be given by

$$\frac{V_0}{V_{in}} = nk \frac{1-D}{1-2D}$$

(1.13)

The main features of this topology are (i) continuous input current, (ii) low turn ratio of coupled inductor, (iii) isolation exists between input and output, (iv) low voltage rating of switch and (v) leakage energy does not create stress on the active switch and diode.

Fig. 1.14(b): Quasi Z-source isolated DC-DC converter.

Figure 1.14(c) shows QZS based isolated converter [3]. This configuration contains QZS inverter, high frequency step-up transformer and voltage doubler rectifier. This topology can be used for providing stabilized output voltage with galvanic isolation for widely varying input voltage. The voltage gain of converter shown in Fig. 1.14(c) is given by

$$\frac{V_0}{V_{in}} = \frac{2n}{(1-2D)}$$

(1.14)

Fig. 1.14(c): QZSI based isolated high step-up DC-DC converter.

Cascaded QZS network based high step-up converter is proposed in [27]. Cascaded network decreases duty ratio required for high step-up operation. Low duty ratio operation reduces the required value of capacitor and inductor. As shown in Fig. 1.14(d) the secondary side of high frequency transformer is voltage doubler rectifier, same as given in [3]. The voltage gain of converter shown in Fig. 1.14(d) is given by

Fig. 1.14(d): Cascaded QZS network based high step-up converter.

QZS push-pull based isolated high step-up DC-DC converter is proposed in [39] as shown in Fig. 1.14(e). The voltage gain of this configuration is given by

$$\frac{V_0}{V_{in}} = \frac{2n}{3 - 4D}$$

(1.16)

This configuration provides wide voltage gain with small duty ratio and small turn ratio of isolation transformer. Hence conduction losses of switches and transformer is less in comparison with other configuration of same origin isolated configuration.

Fig. 1.14(e): QZS push-pull based high step-up converter.

In summary, in non-isolated topologies, high conversion ratio is mainly achieved by using cascading, coupled-inductor, switched-capacitor and switched-inductor techniques or any combination of these techniques. In all the isolated topologies either line frequency or high frequency transformer is used for galvanic isolation. Transformer not only provides isolation but it also step-up input voltage due to turn ratio and transformer working principal.

## **1.3 Scope and objectives of thesis**

It can be observed from the existing literature that non-isolated step up converters can reduce cost and improve efficiency for certain power levels and wherever there are no stringent requirement of isolation [1]. Therefore, many new non-isolated step up converter topologies are being proposed in the literature.

Z-source converter is one of the recently proposed converter topologies for DC-AC operation but it is also quite useful for DC-DC converter. In literature, few DC-DC converter configurations are available based on ZS or QZS networks which are

mainly isolated converters. It can be seen from the previous studies that ZS and QZS based DC-DC converters are also potential candidates for step-up applications. However, some of the non-isolated topologies are not well explored which are based on QZS converter. Further, some non-isolated topologies also can be developed which are based on these converters.

On the similar note, quadratic boost converters are well known for getting high step up ratios. Therefore, it will be interesting to investigate this topology for the development of new step-up converter topologies.

This thesis mainly focuses on study and development of various non-isolated converters based on QZS DC-DC converter and quadratic boost converter, which are of interest for high step-up applications.

The objectives of thesis are

- To analyze and control DC-DC converter based on ZS and QZS converter.

- To develop variations of QZS based DC-DC converters to achieve higher boost at low duty ratio.

- To develop a QZS based DC-DC converter to achieve minimum input current ripple.

- Development of tapped inductor based quadratic boost converters.

## **1.4 Contribution of thesis**

In this thesis six converter configurations are introduced. Four configurations are based upon quasi Z-source network and two configurations are based upon quadratic boost converter using tapped-inductor. The steady state analysis and design guidelines are presented for these converters.

The first converter studied is QZS based DC-DC fourth order converter. The converter performance and control technique is explored in detail. The gain of this converter is same as the converter in [28], the advantage is with less number of components. Advantages of this converter are continuous input current, common ground for source, load and switch.

The second converter is a tapped-inductor variation of the first converter. The voltage gain of this converter is enhanced by using tapped inductor.

The coupled inductor variation of the first converter is also presented where coupled inductor is used to reduce the ripple in input current. The effect of coupling coefficient on current ripple is studied in detail. In the coupled-inductor based topology, reduction in size and weight of converter can be achieved because of utilizing the same core for both the inductors.

Fourth converter is a high step-up non-isolated dc-dc converter which is derived from quasi Z-source converter and a boost converter. Compared to QZS and boost converters, it gives higher gain at a lower duty ratio.

Two converters which integrate the step-up capabilities of the quadratic boost converter and the tapped-inductor based converter are proposed in the sixth chapter. These proposed converters also have an advantage of low voltage stress on active switch.

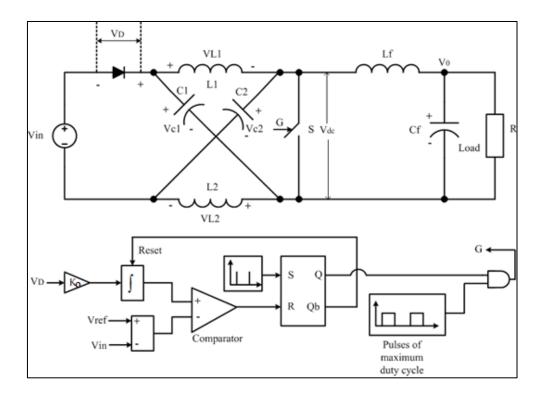

Further One Cycle Control technique is used for the voltage control of conventional ZS and QZS DC-DC converters along with fourth order QZS-based converter. Either capacitor voltage or output voltage can be controlled by using this method. It gives fast dynamic response, excellent reference tracking and input disturbance rejection.

## **1.5 Organization of thesis**

The work presented in this thesis is organized as follows.

**Chapter 2:** Detailed steady state and dynamic analysis of the fourth order QZS based converter is presented. Boundary condition between continuous conduction mode and discontinuous conduction mode is derived. Expressions for power loss in components are derived. Average current mode control based closed loop controller design is also presented. Simulation and experimental results are presented to substantiate the theoretical analysis.

**Chapter 3:** Tapped-inductor and coupled-inductor based fourth order QZS based converter topologies are proposed in this chapter. Steady state analysis of both the topologies is presented. Simulation and experimental results are reported.

**Chapter 4:** One cycle control operation of conventional ZS and QZS based converters are presented. Conditions are derived for changing controlled variable such as DC link voltage and intermediate capacitor voltage. Simulation and experimental results are demonstrated to verify the theoretical analysis.

**Chapter 5:** A high step-up converter based on QZS converter and boost converter is proposed. Steady state analysis and small signal model of converter is presented. Boundary condition for continuous conduction mode and discontinuous conduction

mode is derived. Closed loop controller design is presented. Simulation and experimental results for closed loop control and open loop operation are demonstrated.

**Chapter 6:** presents two new topologies based on quadratic boost converter topology. These converter uses tapped-inductor to achieve high voltage gain. Advantages of these topologies and operation are explained. Voltage gain and efficiency variation with different load and duty ratio is reported. Results are presented for different combination of turn ratio.

Chapter 7: Thesis is concluded in this chapter and future scope of work is discussed.

# Chapter 2

# A Fourth Order PWM DC-DC Boost Converter derived from Quasi Z-Source Topology

## **2.1 Introduction**

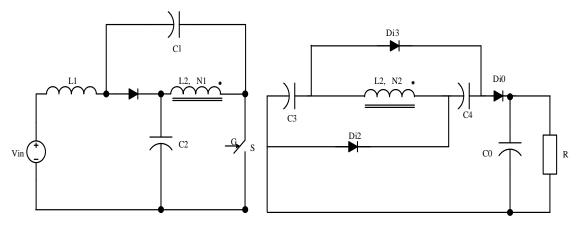

In applications like DC-AC conversion where voltage boost is obtained in a single stage, Z-source converter is a well-known converter topology. It uses an impedance network to couple the power source with converter main circuit [26]. In this topology, controlling of shoot-through state enables to control boost feature of converter with improved reliability. Further, its many variations like quasi Z-source inverter [40], series Z-source inverter [41], and Trans Z-source inverter [42] are present in the literature. In most of the currently available Z-source converter related literature, researchers have focused on DC-AC operation of Z-source converter and shoot through control techniques. Recently, in few publications authors have used Z-source converter for DC-DC mode of operation [28], [29], [43]. In [28] detailed steady state analysis of PWM Z-source DC-DC converter in CCM and effect of non-idealities on converter performance has been presented. Small-signal modeling by circuit-averaging technique of Z-source DC-DC converter in CCM mode is given in [43]. Control for quasi Z-source dc-dc converter is proposed in [29]. Quasi-Z source inverter based isolated DC-DC converter is proposed in [3].

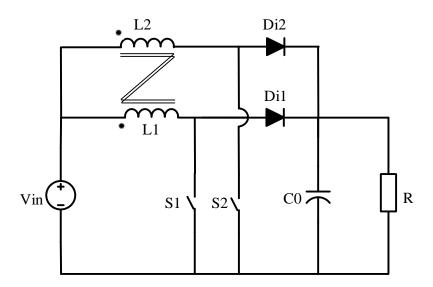

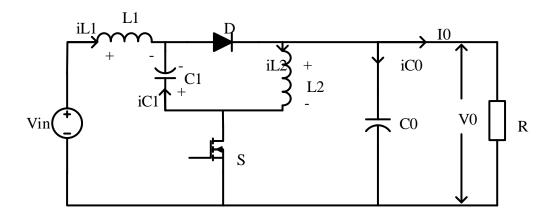

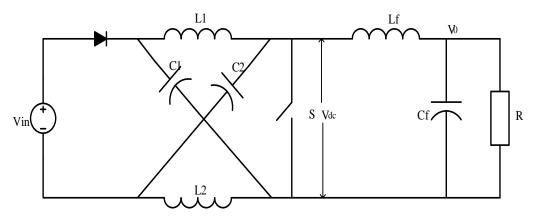

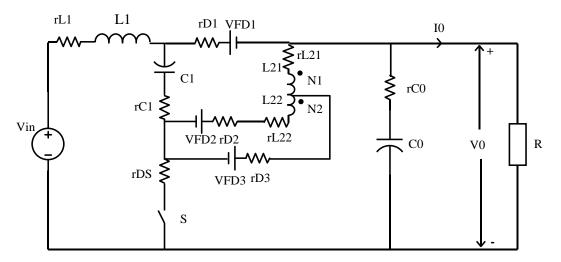

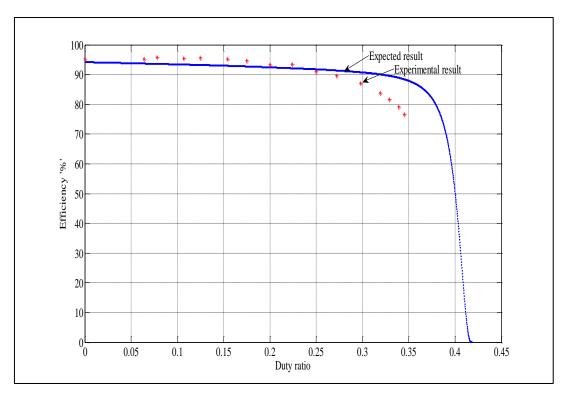

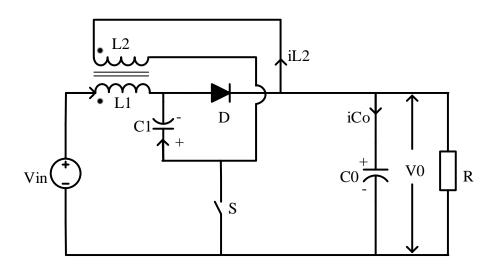

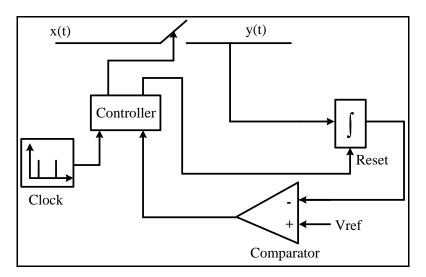

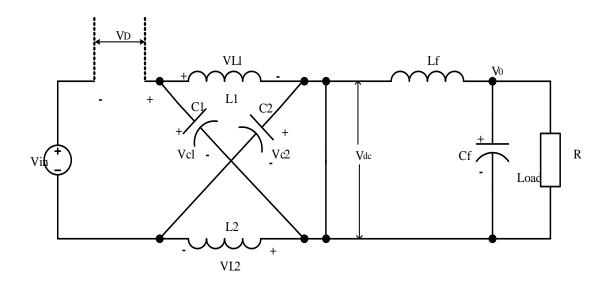

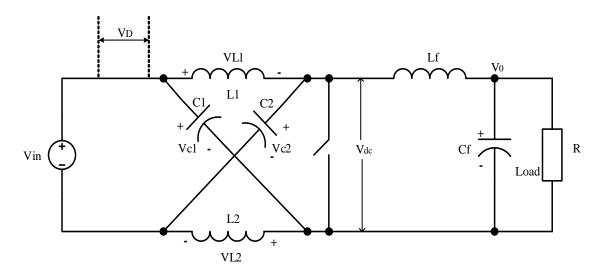

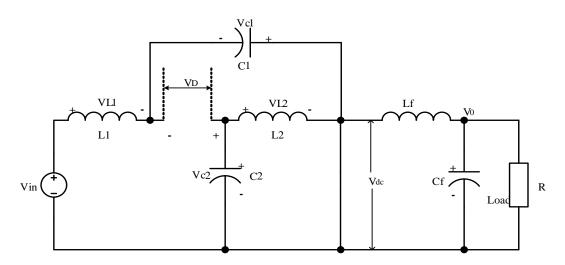

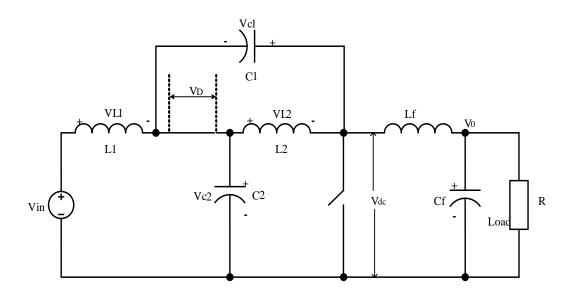

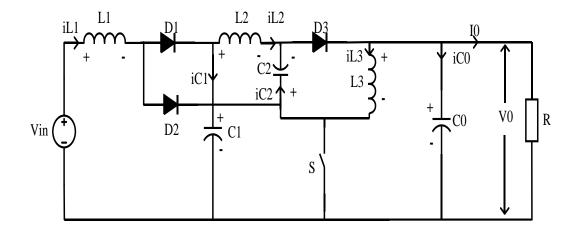

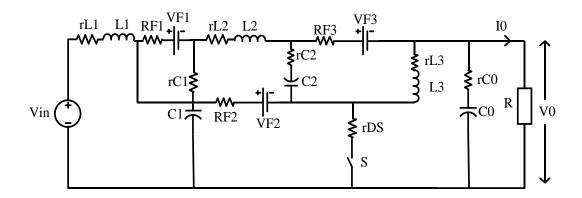

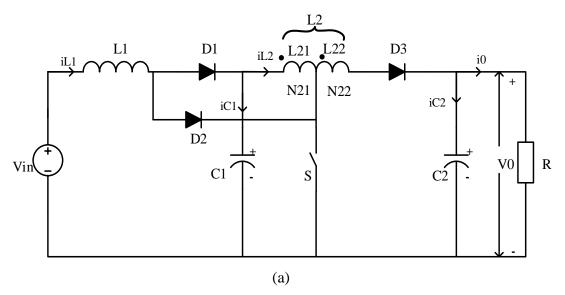

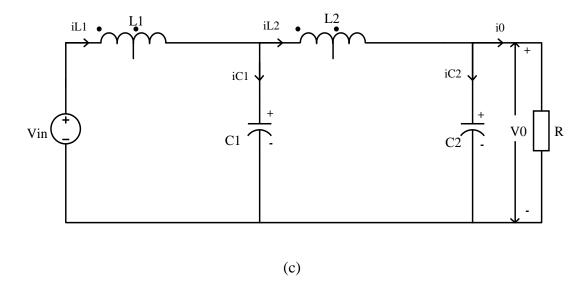

Fig. 2.1: Single phase Quasi Z-source inverter.

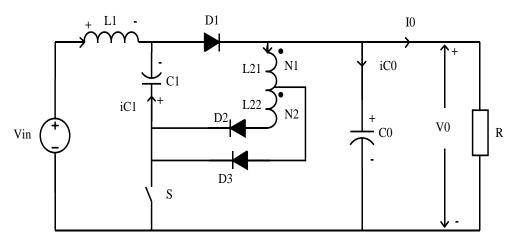

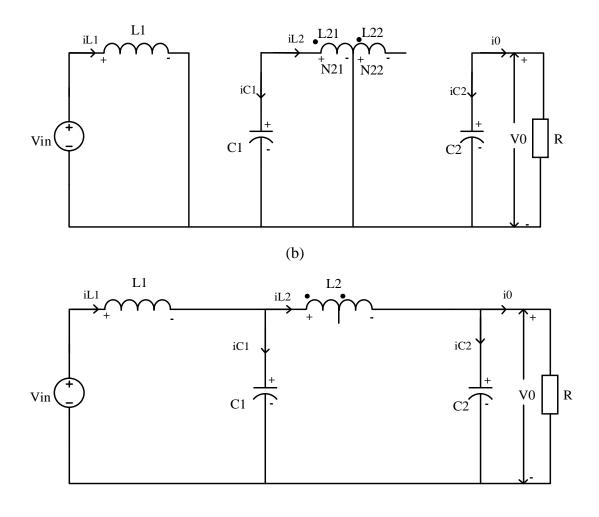

Figure 2.1 shows a single phase voltage fed quasi Z-source inverter. If four switches are replaced by one switch and circuit is rearranged as shown in Fig. 2.2, it results in a DC-DC converter configuration. This configuration can be called as fourth order stepup PWM DC-DC converter because of four dynamic elements and it is a hard switching converter.

The advantages of this converter in comparison with other Z-source based DC-DC converters [28] are reduced number of components for same output voltage, reduced voltage stress on one capacitor, continuous input current, lower inrush current and common ground for source, load and switch. In comparison of Quasi Z-source DC-DC converter as in [29], it has reduced number of components for the same gain.

These features lead to a possibility that it might be a potential topology for renewable energy applications. Its thorough investigation is still not reported in the literature.

Fig. 2.2: Fourth order step-up converter.

In this chapter, a detailed steady state analysis, dynamic analysis and controller design has been presented for a fourth order step up converter. The objectives of this chapter are 1) to present equivalent circuits and associated expressions corresponding to different stages of operation in CCM and DCM, 2) to obtain the dc voltage transfer ratio along with the effect of parasitic resistances, 3) to obtain power loss in different components and overall efficiency, 4) to present a dynamic model and associated controller design, 5) To validate the theoretical results with simulation and experimental results.

The chapter is organized as follows. Section 2.2 presents the equivalent circuit in CCM and related idealized waveforms. Relevant expressions are derived from these waveforms. Section 2.3 presents boundary condition between CCM and DCM.

Further the analysis is extended for DCM operation of converter. Section 2.4 presents power loss analysis and overall efficiency expressions. Small-signal model and controller design for converter are presented in section 2.5. Simulation and experimental results are presented in section 2.6. Conclusions are presented in section 2.7.

# 2.2 Idealized circuit analyses

The steady state analysis is based on following assumptions

- 1. All components are ideal and all resistors, capacitors and inductors are linear time invariant.

- 2.  $C_1$  and  $C_0$  are large enough so that voltages across them can be treated as constant.

- 3. Natural time constant of converter is much higher than the one switching time period.

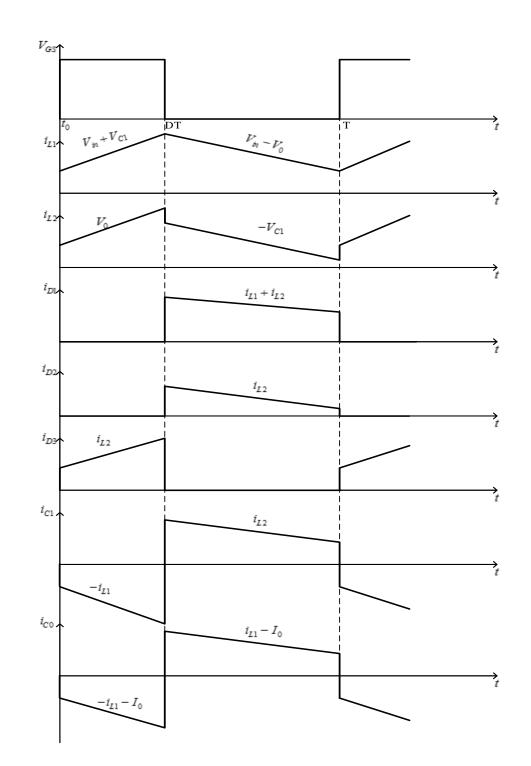

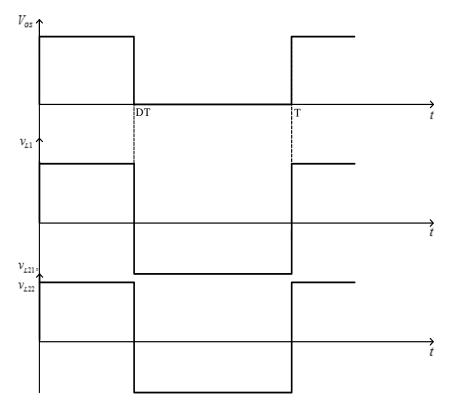

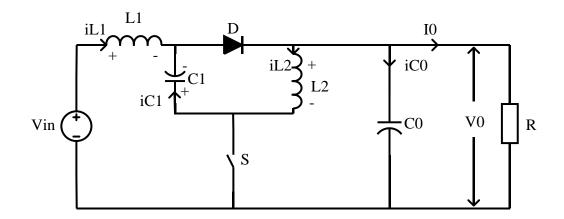

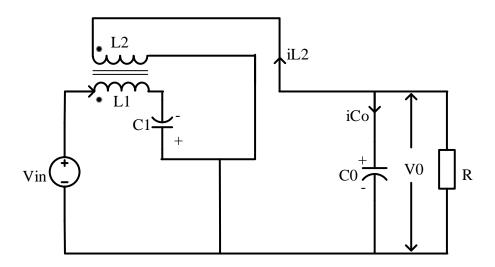

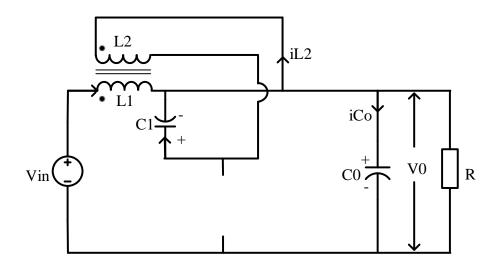

Referring to Fig. 2.2, the switch S is operating at switching frequency  $f_S=1/T$  with the duty ratio  $D=T_{on}/T$ . where  $T_{on}$  is the duration for which switch S is ON. Figures 2.3(a) and Fig. 2.3(b) shows circuit during switch ON and switch OFF condition. Figure 2.4(a) and Fig. 2.4(b) shows idealized current and voltage waveforms for CCM. The slopes of different currents are also shown in Fig. 2.4(a).

## 2.2.1 For time interval $0 \le t \le DT$

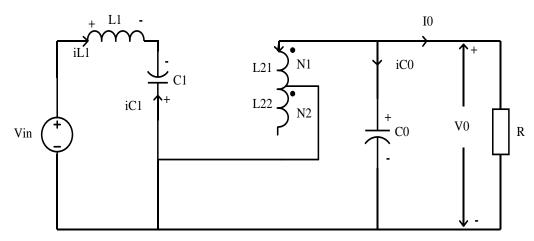

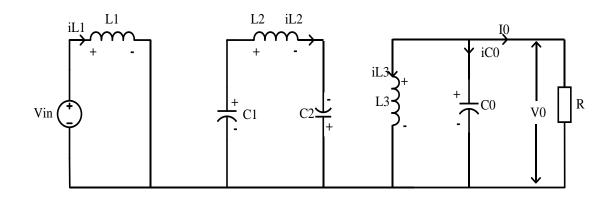

For this duration, equivalent circuit of the converter is as shown in Fig. 2.3(a).

Fig. 2.3(a): Equivalent circuit of converter when S is ON.

Fig. 2.3(b): Equivalent circuit of converter when S is OFF for CCM.

In this duration the main switch S is ON and diode is OFF. Diode is OFF due to reverse bias voltage ( $V_0+V_{C1}$ ). For ideal components, voltage across switch S and current through diode are zero.

Here voltage across inductor  $L_1$  is  $(V_{in}+V_{C1})$  and voltage across  $L_2$  is equal to output voltage  $V_0$ . The current through inductor  $L_1$  and inductor  $L_2$  are

$$i_{L1}(t) = \left(\frac{V_{in} + V_{C1}}{L_1}\right)t + i_{L1}(0)$$

(2.1)

$$i_{L2}(t) = \frac{V_0}{L_2} t + i_{L2}(0)$$

(2.2)

The current through the switch S is sum of both inductor current and is given by

$$i_{S}(t) = i_{L1}(t) + i_{L2}(t) = \left(\frac{V_{in} + V_{C1}}{L_{1}}\right)t + \left(\frac{V_{0}}{L_{2}}\right)t + i_{L1}(0) + i_{L2}(0)$$

(2.3)

From equation (2.1) and (2.2), the peak inductor currents which occurs at time t = DT are given as

$$i_{L1}(DT) = \left(\frac{V_{in} + V_{C1}}{L_1}\right) DT + i_{L1}(0)$$

(2.4)

$$i_{L2}(DT) = \frac{V_0}{L_2}DT + i_{L2}(0)$$

(2.5)

Peak to peak inductors current are expressed as

$$\Delta i_{L1} = i_{L1} \left( DT \right) - i_{L1} \left( 0 \right) = \left( \frac{V_{in} + V_{C1}}{L_1} \right) DT$$

(2.6)

$$\Delta i_{L2} = i_{L2} \left( DT \right) - i_{L2} \left( 0 \right) = \frac{V_0}{L_2} DT$$

(2.7)

Fig. 2.4(a): Idealized current Waveforms for CCM.

Fig. 2.4(b): Idealized voltage waveforms for CCM.

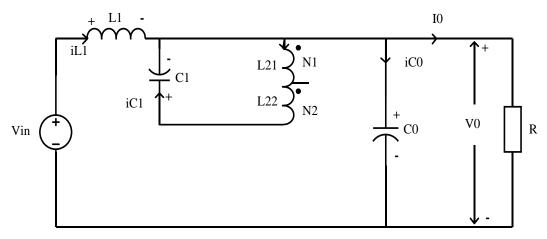

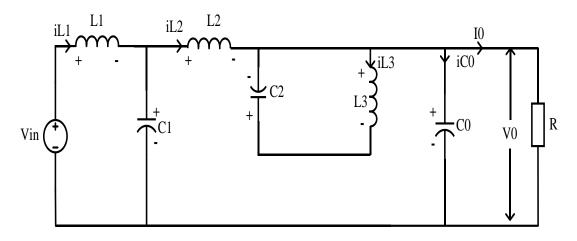

# 2.2.2 For time interval $DT \le t \le T$

Figure 2.3(b) shows equivalent circuit of converter for this time interval. The switch S is OFF and diode becomes ON, hence switch S current and voltage across diode are zero. The inductor  $L_1$  current is given as

$$i_{L1}(t) = \frac{V_{in} - V_0}{L_1} \left( t - DT \right) + i_{L1}(DT)$$

(2.8)

Similarly inductor  $L_2$  current is given as

$$i_{L2}(t) = \frac{V_{C1}}{L_2} (t - DT) + i_{L2}(DT)$$

(2.9)

In this interval, diode current will be equal to the sum of inductor currents and is given as

$$i_{D}(t) = \left(\frac{V_{in} - V_{0}}{L_{1}}\right) \left(t - DT\right) + \left(\frac{V_{C1}}{L_{2}}\right) \left(t - DT\right) + i_{L1} \left(DT\right) + i_{L2} \left(DT\right)$$

(2.10)

In steady state, inductor currents  $i_{L1}$  and  $i_{L2}$  at time T are given as

$$i_{L1}(T) = i_{L1}(0) = \left(\frac{V_{in} - V_0}{L_1}\right)(T - DT) + \left(\frac{V_{in} + V_{C1}}{L_1}\right)DT + i_{L1}(0)$$

(2.11)

$$i_{L2}(T) = i_{L2}(0) = \frac{V_{C1}}{L_2}(T - DT) + \frac{V_0}{L_2}DT + i_{L2}(0)$$

(2.12)

From equation (2.11) and (2.12), voltages  $V_{C1}$  is given as,

$$V_{C1} = \left(\frac{D}{1-D}\right) V_0 \tag{2.13}$$

Similarly from equation (2.11) and (2.13), output voltage in terms of input voltage is given as

$$V_0 = \left(\frac{1-D}{1-2D}\right) V_{in} \tag{2.14}$$

Therefore DC voltage transfer ratio in idealized converter is

$$M_{ideal} = \frac{V_0}{V_{in}} = \frac{1 - D}{1 - 2D}$$

(2.15)

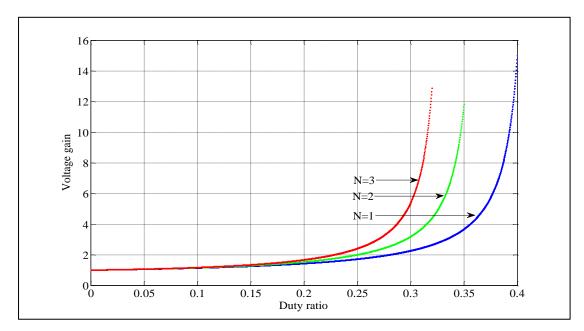

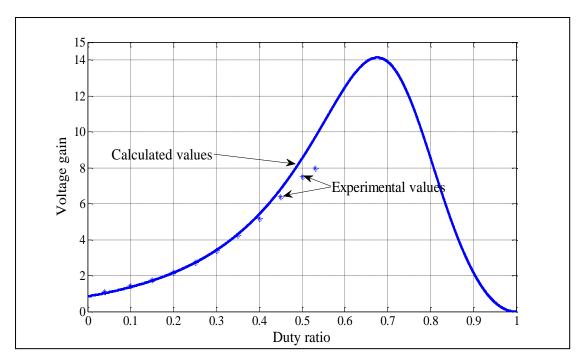

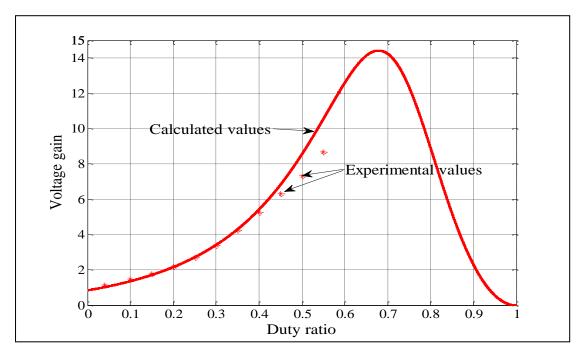

Figure 2.5 shows voltage gain response of ideal converter and it is derived by using equation (2.15). From Fig. 2.5 it can be observed that, converter provides positive gain for duty ratio range from 0 to 0.5 and for higher duty ratio converter gain is negative.

From equation (2.13) and (2.14), capacitor  $C_1$  voltage in terms of input voltage is given by

$$V_{C1} = \left(\frac{D}{1 - 2D}\right) V_{in} \tag{2.16}$$

For ideal converter,  $V_0I_0 = V_{in}I_{in}$ , therefore by using equation (2.15)

$$\frac{V_0}{V_{in}} = \frac{I_{in}}{I_0} = \frac{1 - D}{1 - 2D}$$

(2.17)

In this converter, average inductor current  $I_{L1}$  is same as input current  $I_{in}$ , therefore from equation (2.17)

$$I_{L1} = I_{in} = \left(\frac{1-D}{1-2D}\right) I_0$$

(2.18)

To find average inductor current  $I_{L2}$ , amp-second balance principle is applied on capacitor C<sub>1</sub> which gives

$$-DI_{L1} + (1-D)I_{L2} = 0 (2.19)$$

Therefore average inductor current  $I_{L2}$  is

$$I_{L2} = \left(\frac{D}{1-D}\right) I_{L1} = \left(\frac{D}{1-2D}\right) I_0$$

(2.20)

The current through inductor  $L_1$  at t=0 and current at t = DT can be given from (2.6) and (2.18) as

$$i_{L1}(0) = I_{L1} - \frac{\Delta i_{L1}}{2} = \left(\frac{1-D}{1-2D}\right) I_0 - \frac{V_0}{2L_1} DT$$

(2.21)

$$i_{L1}(DT) = I_{L1} + \frac{\Delta i_{L1}}{2} = \left(\frac{1-D}{1-2D}\right)I_0 + \frac{V_0}{2L_1}DT$$

(2.22)

Fig. 2.5: Voltage Gain variation with duty ratio.

And similarly for inductor  $L_2$  initial current and current at t = DT from (2.7) and (2.20) can be written as

$$i_{L2}(0) = I_{L2} - \frac{\Delta i_{L2}}{2} = \left(\frac{D}{1 - 2D}\right) I_0 - \frac{V_0}{2L_2} DT$$

(2.23)

$$i_{L2}(DT) = I_{L2} + \frac{\Delta i_{L2}}{2} = \left(\frac{D}{1-2D}\right)I_0 + \frac{V_0}{2L_2}DT$$

(2.24)

## 2.2.3 Peak and average values of currents and voltages for switch

According to Fig. 2.4(b) peak value of voltage across switch  $V_{SM}$  and peak reverse diode voltage  $V_{DRM}$  are equal and is given as

$$V_{SM} = V_{DRM} = V_0 + V_{C1}$$

$$V_{SM} = V_{DRM} = \frac{V_{in}}{1 - 2D}$$

(2.25)

Peak value of switch and diode current is sum of peak value of inductor currents,

$$I_{SM} = I_{DM} = I_{L1M} + I_{L2M} = I_{L1} + I_{L2} + \frac{\Delta i_{L1}}{2} + \frac{\Delta i_{L2}}{2}$$

(2.26)

Therefore from equation (2.6), (2.7), (2.18), (2.20) and (2.26),

$$I_{SM} = I_0 \left( \frac{1}{1 - 2D} + \frac{R}{2L} DT \right)$$

(2.27)

Where,  $L = L_1 \parallel L2$

Also from Fig. 2.4(a), average values of switch and diode currents are approximated as

$$I_{SAV} = \frac{D}{1 - 2D} I_0$$

(2.28)

$$I_{DAV} = \frac{1 - D}{1 - 2D} I_0$$

(2.29)

#### 2.2.4 Design of Capacitance values

For converter in CCM, the ripple voltages across capacitors can be found out by using averaged currents in the circuit. From Fig. 2.3(a), output capacitor  $C_0$  current during switch ON is given as

$$C_0 \frac{\Delta V_0}{DT} = I_{L2} + I_0 \tag{2.30}$$

From equations (2.17), (2.20) and (2.30), capacitor value can be derived for a given voltage ripple  $\Delta V_0$  as

$$C_{0} = \frac{V_{in} (1 - D)^{2} DT}{R (1 - 2D)^{2} \Delta V_{0}}$$

(2.31)

Also current in capacitor C1 during switch ON time is given as

$$C_1 \frac{\Delta V_{C1}}{DT} = I_{L1} \tag{2.32}$$

Using equations (2.17), (2.18) and (2.32), capacitor  $C_1$  value can be derived for given voltage ripple as

$$C_{1} = \frac{V_{in} (1-D)^{2} DT}{R (1-2D)^{2} \Delta V_{C1}}$$

(2.33)

# 2.3 Boundary between CCM / DCM and analysis in DCM

#### 2.3.1 Minimum inductance value for CCM

The boundary between continuous and discontinuous mode occurs when minimum value of diode current and switch current reaches zero. So at boundary,  $I_{S\min} = I_{D\min} = 0$ . From equation (2.3), it can be inferred as

$$I_{S\min} = I_{L1} + I_{L2} - \frac{\Delta i_{L1}}{2} - \frac{\Delta i_{L2}}{2} = \frac{I_0}{1 - 2D} - \frac{V_0 DT}{2L} = 0$$

(2.34)

Therefore

$$\frac{2L}{RT} = D(1-2D) \tag{2.35}$$

$$K_c \ge D(1-2D) \tag{2.36}$$

Where  $K_c = (2L/RT)$  and  $L = L_1 \parallel L_2$ . From equation (2.36), minimum value of inductor can be derived for continuous mode of operation of converter, for given values of load resistance, switching frequency and duty cycle.

#### 2.3.2 DC voltage transfer ratio in DCM and expression for remaining current

The boundary condition for switch current and diode current in discontinuous conduction mode is

$$i_{S}(0) = i_{D}(0) = i_{L1}(0) + i_{L2}(0) = 0$$

(2.37)

Therefore, the equivalent circuit of the converter in discontinuous conduction mode is shown in Fig. 2.6(a). Figure 2.6(b) shows different current waveforms in the circuit for the converter operating in DCM. Figure 2.6(b) also shows voltage waveform across inductor  $L_1$  and  $L_2$ .

For one cycle, volt-second balance equation for inductor  $L_1$  is

$$(V_{in} + V_{C1})D + (V_{in} - V_0)D_1 = 0$$

(2.38)

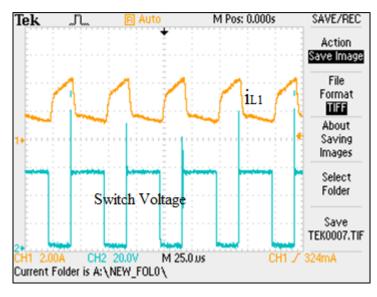

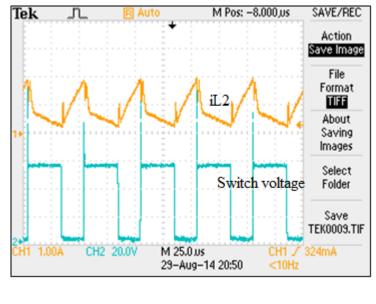

Fig. 2.6(a): Equivalent circuit of converter for DCM.